今天,小编将在这篇文章中为大家带来基于FPGA数字信号处理器设计AM调制的有关报道,通过阅读这篇文章,大家可以对本文的设计具备清晰的认识,主要内容如下。

一、AM调制的原理

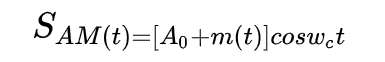

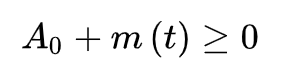

由此可以看出,第一,AM波的频谱与基带信号的频谱呈线性关系,只是将基带信号的频谱搬移到wc处,并没有产生新的频率成分,因此AM调制属于线性调制;第二,AM信号波形的包络与基带信号m(t)成正比,所以AM信号的解调既可采用相干解调,也可采用非相干解调(包括检波)。但为了使非相干解调时不发生失真,必须满足:

否则,就会出现过调制现象,形成包络失真。第三,AM的频谱中含有载频和上、下两个边带,无论是上边带还是下边带,都含有原调制信号的完整信息,故已调波的带宽为原基带信号带宽的两倍。

AM信号的总功率包括载波功率和边带功率两部分。只有边带功率才与调制信号有关。也就是说,载波分量不携带信息,所以,调制效率低是AM调制的最大缺点。

如果抑制载波分量的传送,则可演变出另一种调制方式,即抑制载波双边的调制。AM调制的优点是可用包络检波法解调,不需要本地同步载波信号,设备简单。

波形特点:已调波包络完全反应调制信号变化规律;

频谱特点:

AM信号的频谱SAM(ω)由载频分量和上、下两个边带组成;

上边带的频谱结构与原调制信号的频谱结构相同,下边带是上边带的镜像;

带宽:AM信号是带有载波的双边带信号,它的带宽是基带信号带宽Bb的两倍,即BAM=2Bb。

二、FPGA数字信号处理-AM调制的实现

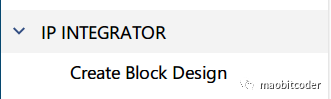

为了加速设计 我们推荐一种更方便的设计输入方式bd(block_design)。这种设计方式大概就是加价IP核 连连线。

创建一个DB

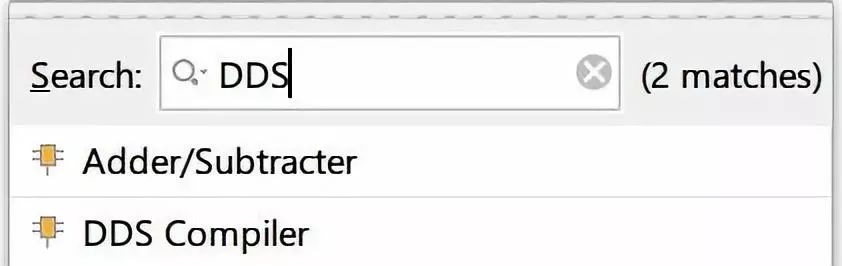

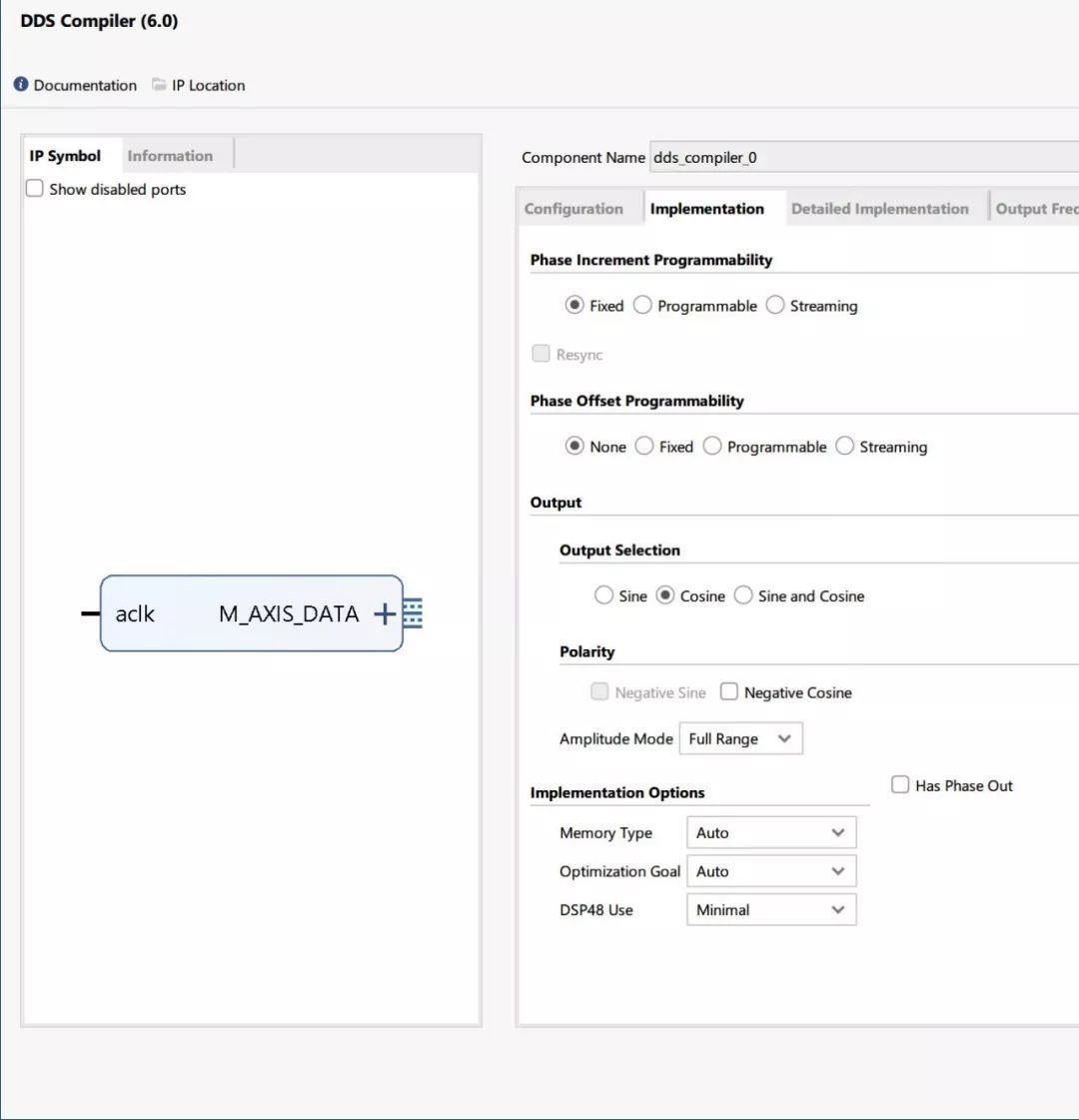

首先添加一个DDS核.然后开始配置它

这里有一个SFDR(动态范围)

一般意义上1bit ≈ 6.02bit。具体计算过程大家可以百度。

输出一个COS 不输出相位

一个数据有效位 八个数据位。输出频率设置为1Mhz

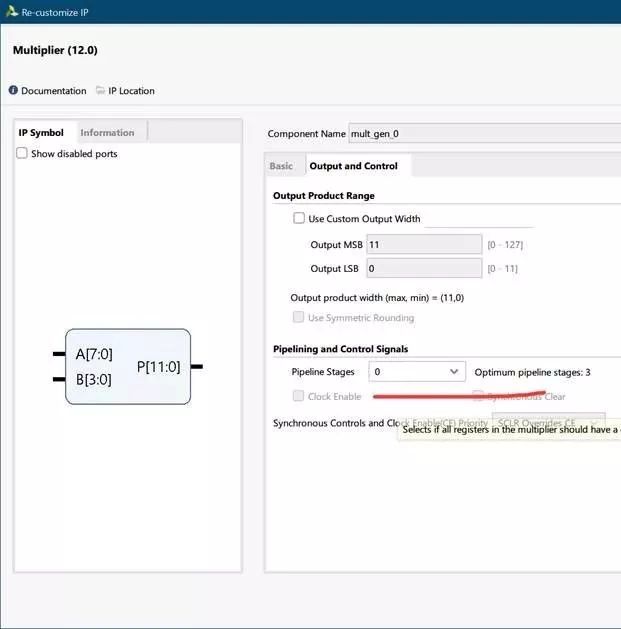

然后添加一个乘法器IP。我们要将这个信号乘以调制深度。

注意符号位,DDS IP核输出是有符号的。调制深度为无符号数,选择0延时输出即可

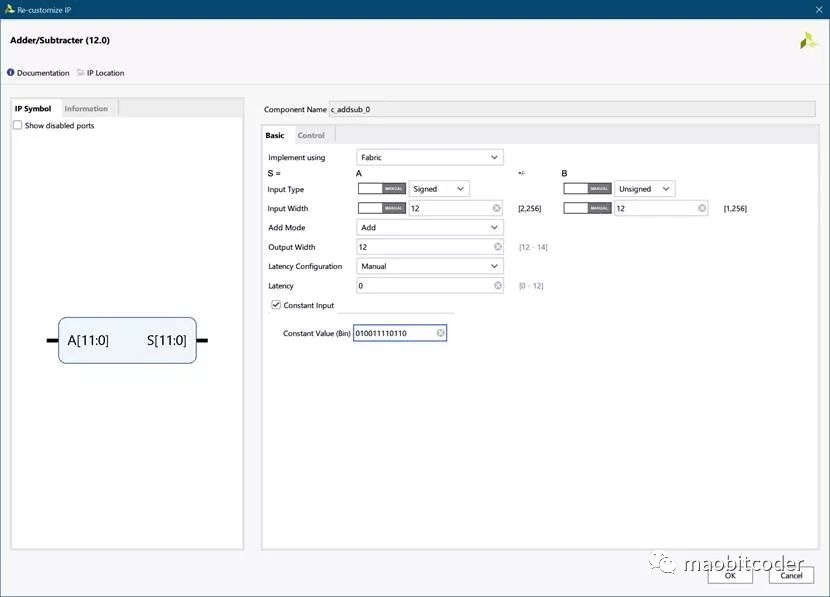

然后我们添加一个加法器IP用以添加增加直流分量。加法器IP为乘法器输出加一个定值。按图设置

这个首先需要指定B的类型和位宽然后输入二进制的数据

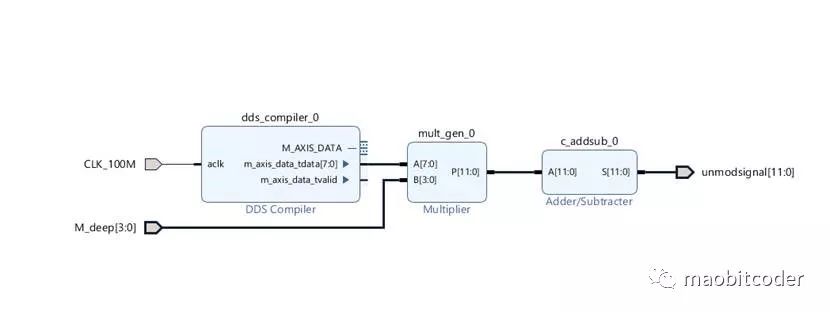

接下来将以上的IP链接起来。并且添加对外的端口(快捷键Ctrl+T)。

然后生成HDLwrapper(这个单词意思是包装,但是我没有能力恰当的翻译索性就直接这样称呼)

接下来我们写个testbench代码测试下 。看起来我们只要给一个时钟信号,给一个调制深度就OK。这里就不贴代码了。非常简单的

这样我们就完成了调制前的波形产生。

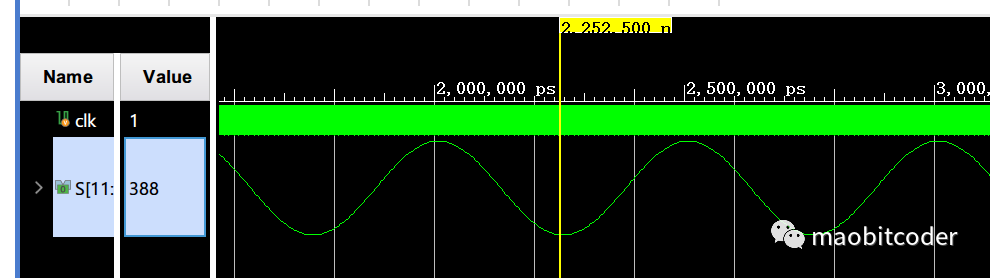

可以看到波形已经产生。且均为有符号数。

接下来如法炮制。添加一个载波DDS 频率设置为10M。添加一个乘法器IP。最终的BD图如所示。

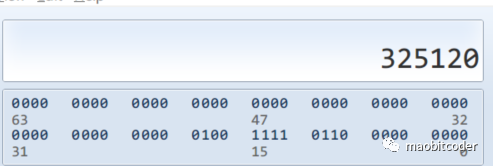

以看到输出有20bit我们进行一个简单的计算(1270*10+1270)*127 =325120

可以看到第20bit无用

所以我们选取[18:3]这16bit。作为输出。

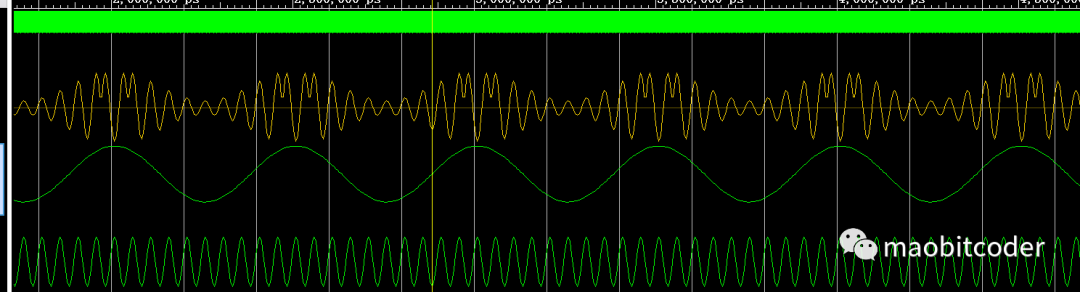

刚刚哪个testbench 改改还能用。最终效果如下。

以上便是小编此次想要和大家共同分享的内容,如果你对本文内容感到满意,不妨持续关注我们网站哟。最后,十分感谢大家的阅读,have a nice day!

2190

2190

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?