锁相环PLL

pll设计与进阶

ID:74100731326076025

爱吃一品蛋酥的浅溪穗瀣

锁相环(Phase-Locked Loop,PLL)是一种常用的电路设计技术,广泛应用于通信、计算机、数字信号处理等领域。本文将围绕PLL设计与进阶展开讨论,从基础概念、工作原理、设计方法、性能评估等多个方面进行深入分析。

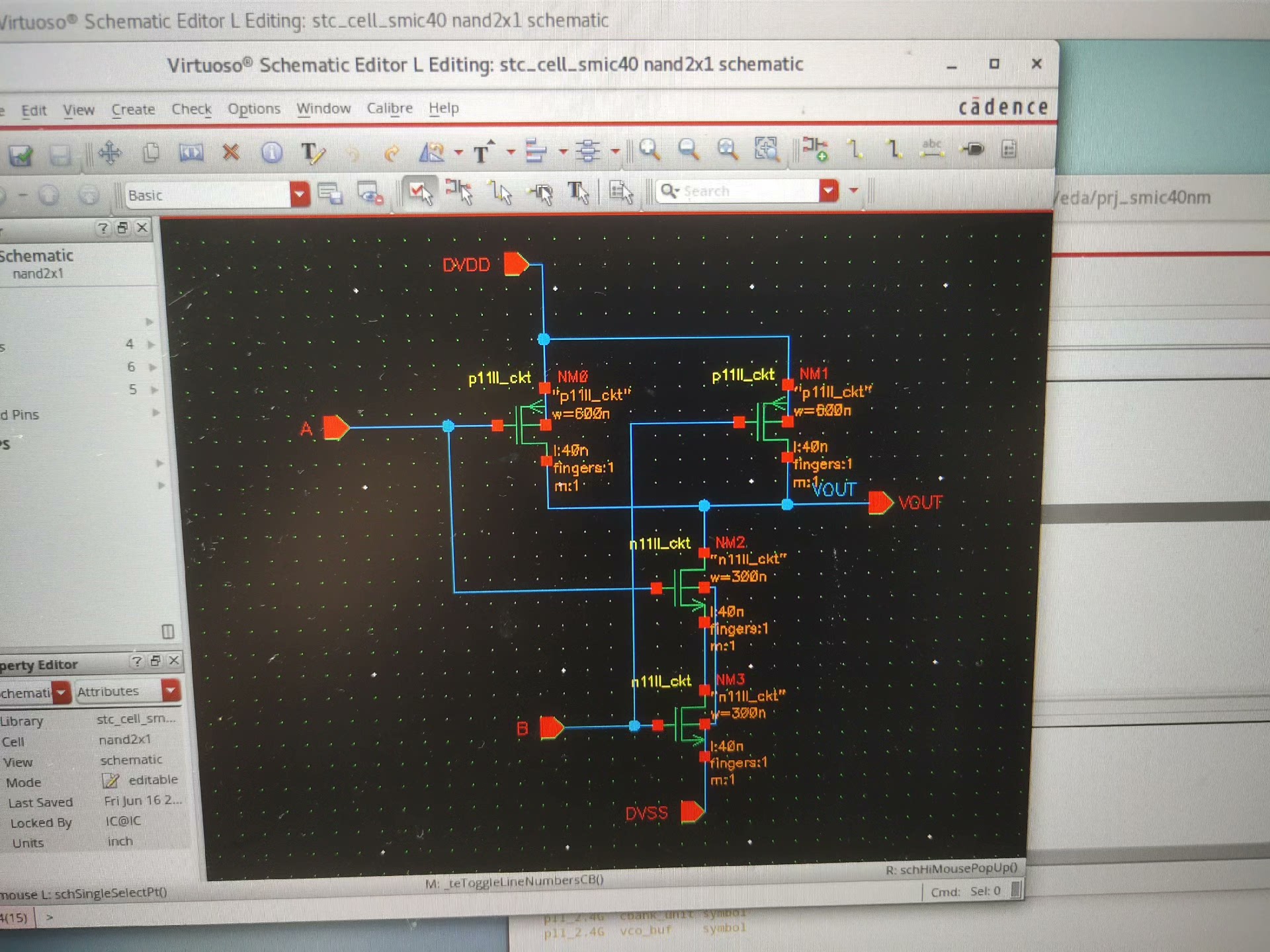

首先,我们来了解PLL的基本概念和工作原理。PLL是一种反馈控制系统,通过自动调节输出信号与参考信号之间的相位和频率差,实现输出信号与参考信号的同步。PLL的核心组成部分包括相频检测器、低通滤波器、电压控制振荡器(VCO)以及分频器等。相频检测器用于比较参考信号和输出信号的相位和频率差,低通滤波器用于平滑相频检测器的输出,VCO则根据低通滤波器的输出控制输出信号的频率和相位,分频器则用于将输出信号进行分频。

接下来,我们将重点探讨PLL的设计方法和技巧。PLL的设计过程中,需要确定的参数包括参考信号频率、输出信号频率、环路带宽、锁定时间等。通过合理选择参数,可以使PLL具备良好的稳定性、抗噪声干扰能力和快速的锁定时间。同时,在设计中还需要考虑相频检测器的选择、低通滤波器的设计、VCO的频率范围和线性度等因素。本文将通过实例分析来详细介绍设计方法和技巧,并给出相应的设计指导。

除了基础的PLL设计,本文还将深入讨论PLL的进阶应用。首先是多相位输出的PLL设计,通过适当的引入分频器和相位选择器,可以实现多个同步的输出信号,满足不同应用场景的需求。其次是频率合成器的设计,PLL可以通过频率合成技术将一个较低频率的参考信号合成为更高频率的输出信号,广泛应用于无线通信、频率调制等领域。此外,PLL还可以用于时钟恢复、时钟倍频、频率捕获等多种应用,这些进阶应用将在本文中进行详细介绍和分析。

最后,我们将对PLL的性能评估进行讨论。PLL的性能参数包括锁定范围、抖动、相位噪声、频率稳定性等,这些参数对于不同的应用具有重要意义。通过合理设计和调节,可以使PLL在各项性能参数上达到预期要求。本文将介绍评估PLL性能的方法和指标,并讨论如何优化和改进PLL的性能。

综上所述,本文围绕PLL设计与进阶展开了全面而深入的讨论。通过对PLL基础概念、工作原理、设计方法和进阶应用的分析,读者可以全面了解PLL的原理和设计技巧,并掌握评估和优化PLL性能的方法。希望本文能为读者提供有价值的技术指导和参考,帮助他们在实际应用中更好地应用和设计PLL电路。

【相关代码,程序地址】:http://fansik.cn/731326076025.html

2285

2285

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?