锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-Locked Loop)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

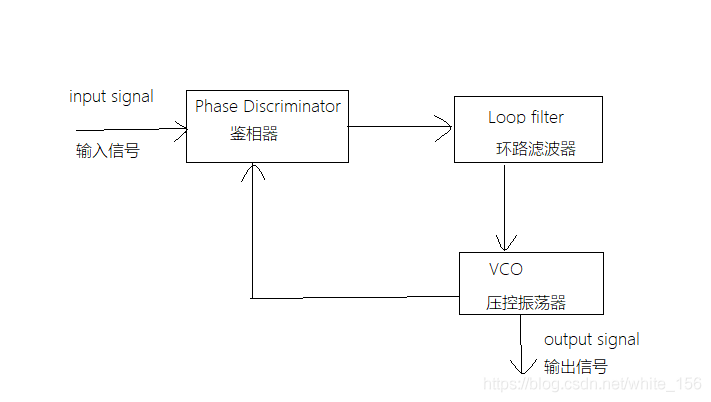

PLL工作原理框图如下

首先说明鉴相器Phase Discriminator:

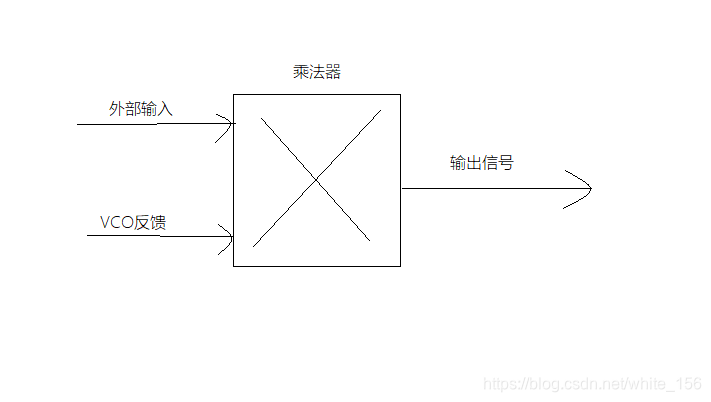

鉴频器可以由乘法器实现

设外部输入为 U i ( t ) = U m sin [ ω i t + θ i ( t ) ] U_i(t) = U_m \sin[\omega_i t+\theta_i(t)] Ui(t)=Umsin[ωit+θi(t)],VCO直流输出(无外接信号时输出)为 U o ( t ) = U o m cos [ ω o t + θ o ( t ) ] U_o(t)=U_{om}\cos[\omega_o t+\theta_o(t)] Uo(t)=U

PLL 锁相环原理介绍

最新推荐文章于 2024-05-04 14:15:04 发布

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

7388

7388

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?