写在前面

本系列文章主要讲解德州仪器(TI)TDA4VM芯片的相关知识,希望能帮助更多的同学认识和了解德州仪器(TI)TDA4VM芯片。

若有相关问题,欢迎评论沟通,共同进步。(*^▽^*)

错过其他章节的同学可以电梯直达目录↓↓↓

TDA4VM芯片

6. 时序和开关特性

6.3 系统时序

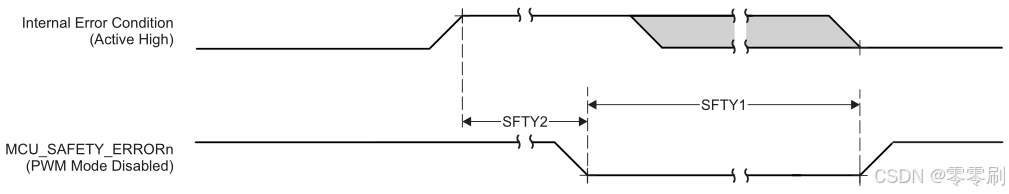

6.3.2 安全信号时序

本部分提供的表格和图表定义了MCU_SAFETY_ERRORn和SOC_SAFETY_ERROR的切换特性。

| 序号 | 参数 | 最小值 | 最大值 | 单位 | |

| SFTY1 | t w(MCU_SAFETY_ERRORn) | Pulse width minimum, MCU_SAFETY_ERRORn active (PWM mode disabled) | P*R | / | ns |

| SFTY2 | t d (ERROR_CONDITION-MCU_SAFETY_ERRORnL) | Delay time, ERROR CONDITION to MCU_SAFETY_ERRORn active | 50*P | / | ns |

表 9 MCU_SAFETY_ERRORn Switching Characteristics

注:

(1) P = ESM functional clock (MCU_SYSCLK0 /6).

(2) R = Error Pin Counter Pre-Load Register count value.

图 15 MCU_SAFETY_ERRORn Switching Characteristics

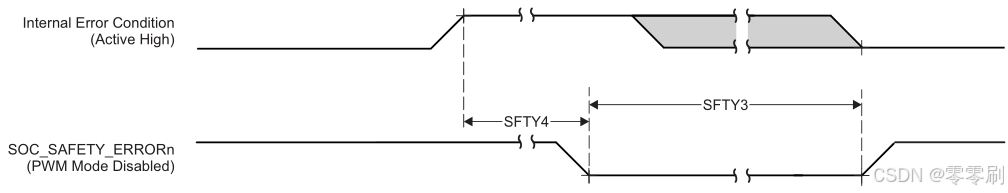

| 序号 | 参数 | 最小值 | 最大值 | 单位 | |

| SFTY3 | t w(SOC_SAFETY_ERRORn) | Pulse width minimum,SOC_SAFETY_ERRORn active (PWM mode disabled) | P*R | / | ns |

| SFTY4 | t d (ERROR_CONDITION-SOC_SAFETY_ERRORnL) | Delay time, ERROR CONDITION to SOC_SAFETY_ERRORn active | 50*P | / | ns |

表 10 SOC_SAFETY_ERRORn Switching Characteristics

图 16 SOC_SAFETY_ERRORn Switching Characteristics

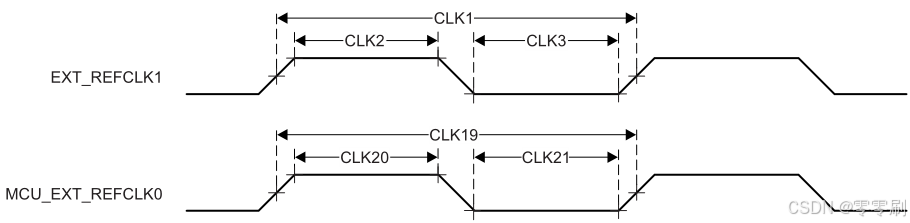

6.3.3 时钟时序

本节提供的表格和图表定义了时钟信号的定时要求和切换特性。

| 序号 | 参数 | 最小值 | 最大值 | 单位 | |

| CLK1 | t c(EXT_REFCLK1) | Cycle time minimum, EXT_REFCLK1 | 10 | / | ns |

| CLK2 | t w(EXT_REFCLK1H) | Pulse Duration minimum, EXT_REFCLK1 high | E*0.45 | E*0.55 | ns |

| CLK3 | t w(EXT_REFCLK1L) | Pulse Duration minimum, EXT_REFCLK1 low | E*0.45 | E*0.55 | ns |

注:E = EXT_REFCLK1 cycle time

表 11 Clock Timing Requirements

图 17 Clock Timing Requirements

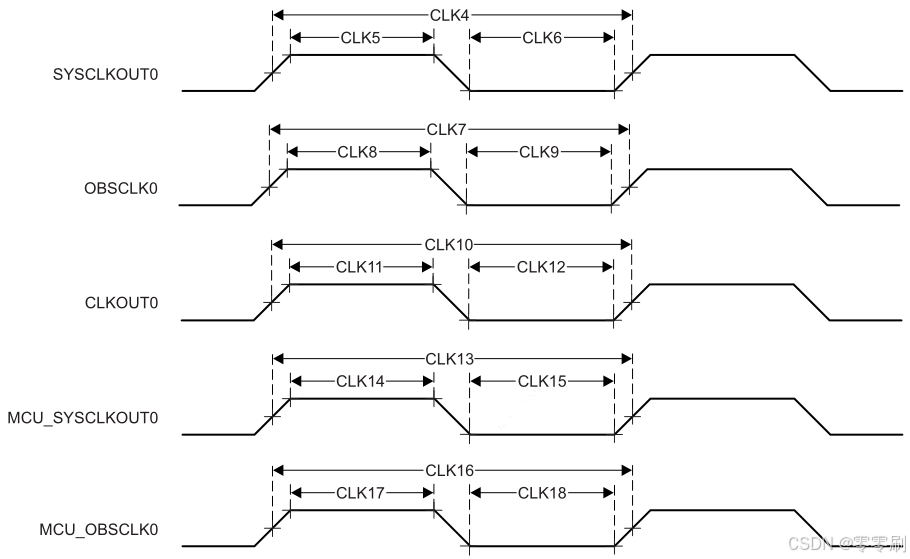

| 序号 | 参数 | 最小值 | 最大值 | 单位 | |

| CLK4 | t c(SYSCLKOUT0) | Cycle time minimum,SYSCLKOUT0 | 8 | / | ns |

| CLK5 | t w(SYSCLKOUT0H) | Pulse Duration minimum, SYSCLKOUT0 high | A*0.4 | A*0.6 | ns |

| CLK6 | t w(SYSCLKOUT0L) | Pulse Duration minimum, SYSCLKOUT0 low | A*0.4 | A*0.6 | ns |

| CLK7 | t c(OBSCLK0) | Cycle time minimum, OBSCLK0 | 5 | / | ns |

| CLK8 | t w(OBSCLK0H) | Pulse Duration minimum, OBSCLK0 high | B*0.4 | B*0.6 | ns |

| CLK9 | t w(OBSCLK0L) | Pulse Duration minimum,OBSCLK0 low | B*0.4 | B*0.6 | ns |

| CLK10 | t c(CLKOUT0) | Cycle time minimum, CLKOUT0 | 20 | / | ns |

| CLK11 | t w(CLKOUT0H) | Pulse Duration minimum, CLKOUT0 high | C*0.4 | C*0.6 | ns |

| CLK12 | t w(CLKOUT0L) | Pulse Duration minimum,CLKOUT0 low | C*0.4 | C*0.6 | ns |

注:

(1) A = SYSCLKOUT0 cycle time

(2) B = OBSCLK0 cycle time

(3) C = CLKOUT0 cycle time

表 12 Clock Switching Characteristics

图 18 Clock Switching Characteristics

本文章是博主花费大量的时间精力进行梳理和总结而成,希望能帮助更多的小伙伴~ 🙏🙏🙏

后续内容将持续更新,敬请期待(*^▽^*)

欢迎大家评论,点赞,收藏→→→

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?