p31

两种类型的pcie端点:

1、纯粹的pcie设备

2、传统的pcie设备

纯粹的pcie设备:

1、不支持IO事务和锁定事务

2、中断只支持msi

3、可预取存储器地址空间必须支持64位,不可预取存储器地址空间允许映射到低4GB区域

传统的pcie设备:

支持传统的、使用中断请求消息的中断生成(中断消息事务);也支持msi中断

中断的提交方式:p141

pci:

带外方式,利用INTx边带信号提交中断请求

pcie:

1、msi(pcie设备启动一个写存储器包,向根复合体/主桥发送一个中断向量,主桥再中断CPU,p33)

2、中断消息事务(向根复合体/主桥传达传统pci总线上的INTx#信号跳变情况)

p32

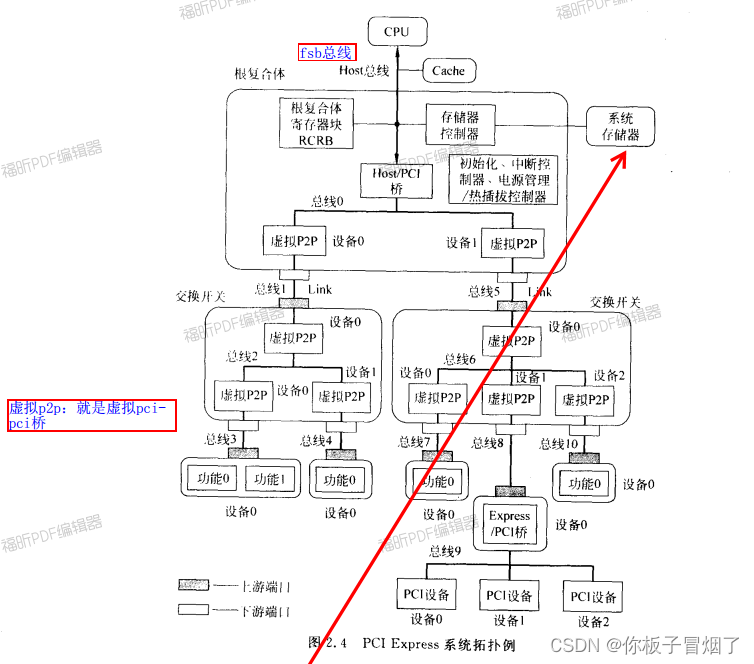

上游端口:指向根复合体

下游端口:离开根复合体

入端口:一个端口中接收包的部分

出端口:一个端口中发送包的部分

p32

pci -> pcie 存储空间、io地址空间、配置空间的演进:

存储空间不变

io空间不变

配置空间有变化:

每个功能(注意是按功能)的最大配置空间从pci的256B扩充到4kB,低256B与PCI相同

pcie还新增了一个消息空间(对应的新增了一个消息事务(新的事务类型)p32)

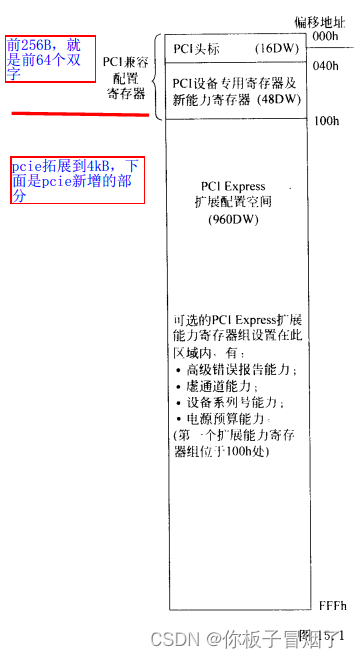

图来自p303

pcie比pci新增了一个消息事务(原来:存储器读、存储器写、io读、io写、配置读、配置写)p32

p32

转发事务:不需要完成包

非转发事务:需要

p32

TLP包里存在两种crc:

1、链路级crc:局限在一条链路的发送器和接收器之间。若检测出此crc错误,对端发送器自动重发(无软件参与)

2、端-端crc:可选的

二者的位置图示待后续补充

p32

pcie包的传输类别:

traffic class,取值0到7

由软件分配

表示包通过pcie线路结构的优先级

vc仲裁:

就是对vc,virtual channel,虚通道进行仲裁

一个端口设置有多个虚通道,包们在各个虚通道等待发送,端口把来自不同vc的包推到链路之前要判断顺序,那个vc的先

端口仲裁:

来自不同入端口的包若要被送到同一个vc输出缓冲器,要确定各个入端口的先后顺序

就是对不同端口仲裁

p33

pcie的五种设备电源状态:

D0:全开电源状态

D1

D2

D3hot

D3cold:最低小号电源状态

pcie的五种链路电源状态:

L0:全开链路状态

L0s

L1

L2

L3:Link-Off电源状态

p33

主动/自主的电源管理:

不涉及软件

设备意识到一定时间没有包通过链路,会将该链路置入省电状态

p33

pcie热插拔的实现 通过 热插拔中断消息传达到根复合体,然后热插拔软件去检测热插拔时间

p35

host总线、host-pci桥 图示

host-pci桥的次级总线为总线0 p36

p36

原级总线:桥上游端的总线 Primary Bus

次级总线:桥下游端的总线 Secondary Bus

下属总线:次级总线以下(包括次级总线本身)到下游分支最远的总线成为桥的下属总线(总线号最大的) Subordinate Bus

p36

pcie的4种事务:

1、存储器事务

2、配置事务

3、IO事务(纯粹的pcie设备不支持,传统的pcie设备支持)

4、消息事务(pcie设备支持,pci设备不支持)

其中只有存储器写事务和消息事务是转发事务,其他都是非转发的

TLP

tlp包的组成: p37

1、起始码(Start of Packet, SOP):标志着TLP的开始。

2、TLP头(TLP Header):包含了事务的类型、地址信息、数据长度等控制信息。

3、数据(Data):根据具体的事务类型,可以包含传输的数据。

4、结束码(End of Packet, EOP):标志着TLP的结束。

每个带数据的tlp完成包最多带4KB数据 p38

p312

在PCIe(Peripheral Component Interconnect Express)协议中,CRS Completion是指Configuration Request Retry Status类型的Completion。

这里的CRS是Configuration Request Retry Status的缩写。

在PCIe总线规范中,当一个设备发送配置事务时,如果因为某种原因不能立即完成该事务,它可能会返回一个带有特定状态码的Completion报文。

其中一个可能的状态码就是CRS,表示Configuration Request需要重试(Retry),通常是因为目标设备正在处理其他请求或者处于无法响应配置事务的状态。

在传统的PCIe TLP(Transaction Layer Packet)中,并没有专门的“CRS completion”类型,但在某些上下文中,

如果Completion包中的Status字段被设置为指示Configuration Request需要Retry的状态,则可以称这样的Completion为“CRS completion”。

在较新的PCIe规范版本中,如PCIe 6.0之前,非配置请求的Completion中出现CRS状态会被认为是Malformed TLP(格式错误的事务层数据包)。而在PCIe 6.0及以后版本中,这个概念有所变化,原先的CRS被RRS(Request Retry Status)所替代,用于所有类型的请求。

p302

pcie配置空间中,总线号8位,设备号5位,功能号3位,组成每一个功能的16位地址。

配置空间的设备id寄存器也是16位 见图15.1 p303

判断一个pcie设备是什么类型?

读配置空间的状态寄存器(PCI头标区偏移6),判断其bit4(能力链表位):此位为1标明功能在其PCI兼容配置空间的高48DW内存在一个或多个新能力寄存器组p330

所有的PCIE功能此位都会置1 p330

确认存在新能力寄存器组后,读配置空间0x34能力寄存器组,见图示16.5 p327,然后顺着这条链表遍历,看看有没有capility id为0x10的能力寄存器组(PCI Express Capability寄存器组)见表16.2 p328

有的话,读PCIe能力寄存器组(见图17.1 p367)中的偏移为2的PCIe能力寄存器(图17.2 p367)的bit4到bit7,判断它是:纯粹pcie端点、传统pcie端点、根复合体的根端口、交换开关的上下游端口、pcie-pci(x)桥和pci(x)-pcie桥中的一种 p368

pcie的配置空间一共有4KB。共1024个双字DB。

至 16DB / 64B:PCI头标区

至 64DB / 256B:PCI兼容配置空间/PCI设备关联区,存放设备专用的配置寄存器;还有一些随着spec更新新增的配置寄存器,头标区放不下了,转而放到这个区域 p302

至 960DB / 4KB:PCIe拓展配置空间,存放可选的PCIe扩展能力寄存器组 详见17.2节

上述区域分布见图15.1 p303

这些宏定义了PCI设备头部类型 / 头标区类型:

-

PCI_HEADER_TYPE_NORMAL:值为0,定义了一个标准或常规PCI设备的头部类型。这类设备通常直接与系统总线交互,并提供用户可访问的功能,如网卡、声卡等。 -

PCI_HEADER_TYPE_BRIDGE:值为1,定义了PCI到PCI桥接器设备的头部类型。这种类型的设备用于连接两个或多个独立的PCI总线,

允许数据在不同的总线之间传输,从而扩展系统的PCI功能和配置空间。 -

PCI_HEADER_TYPE_CARDBUS:值为2,定义了CardBus桥接器的头部类型。CardBus是PCI的一种便携式扩展标准,通常用于笔记本电脑等移动设备上,

支持PC Card(也称为PCMCIA卡)。CardBus桥接器负责将更传统的PCI总线连接到CardBus插槽,使得系统可以使用更小、更低功耗的CardBus设备。

每个PCI设备都有一个配置空间,其中包含了设备类型信息,通过读取设备的配置头类型寄存器(Header Type Register),

操作系统可以根据上述定义来识别并正确处理各种不同类型的PCI设备。

就是配置空间头标区的类型

pcie的一级链接和二级链接:

一级链接是直接与根复合体(Root Complex)相连的链路

二级链接是指从一个PCIe端点设备(Endpoint Device)或者桥接设备(Bridge Device)出发的额外链路,用于连接更多的子设备。

pcie兼容配置空间(前256B)寄存器详解见:第16章

pcie设备的中断引脚寄存器 p340 取值0x01到0x04,分别对应4个PCI中断请求引脚

待确认:pcie设备这个值为多少?

msi和msi-x的区别:

PCIe协议中,MSI(Message Signaled Interrupts)和MSI-X(Message Signaled Interrupts Extended)都是用于改进中断处理机制的两种不同技术,它们都替代了传统的PIN-based中断(INTx),提供了更高效、更低延迟的中断服务。以下是两者的主要区别:

-

中断向量数量:

- MSI:最多支持32个不同的中断向量,每个设备功能只能配置一组固定的中断向量。

- MSI-X:允许为每个设备功能配置多个独立的中断向量,并且支持的数量远超32个,可以达到上千个,具体数量取决于平台和设备的具体实现。

-

中断向量分配灵活性:

- MSI:如果设备需要多个中断,则必须连续使用中断向量号,资源有限,可能不适用于具有大量并发中断需求的高端设备。

- MSI-X:不要求中断向量号连续,系统可以根据需要动态分配,从而更加灵活地管理中断资源。

-

结构与配置空间:

- MSI:在PCI Express设备的配置空间中有特定的位置来设置MSI中断消息地址和数据,其配置相对简单。

- MSI-X:引入了一套新的capability structure,其中包括一个中断消息表(Message Table),每个表项对应一个中断向量,每个向量都有独立的消息地址和数据。此外,还有其他相关控制寄存器,如Pending Bit Array和Mask Bits Array等,以提供更多的中断管理功能。

-

目标处理器的选择:

- MSI:虽然也可以指定中断的目标CPU,但通常不如MSI-X灵活,特别是在多核处理器系统中。

- MSI-X:可以更为精确地将中断定向到系统的任意处理器核心,这对于优化性能和负载均衡非常有利。

-

硬件支持:

- MSI:大多数现代PCIe设备都支持MSI。

- MSI-X:是一种扩展形式,支持更多的中断请求,通常较新的和高级的PCIe设备会支持MSI-X。

总结来说,MSI-X是MSI的一个增强版本,它不仅解决了MSI中断数量限制的问题,还提供了更高的灵活性和可编程性,使得设备能够更好地适应复杂的、多线程及多核心环境下的中断处理需求。

活动状态电源管理(ASPM Active State Power Management) 微软VISTA以及之后的系统上所支持的一种电源链接管理方案,尝试在设备(PCI Express)空闲时采用节电模式。

1696

1696

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?