项目用到DS90UB948/MAX96762解串器和LVDS转MIPI芯片,一些专业术语及基础知识,记录下来。以下资料都是从网上搜索到的。

CDR(Clock Data Recovery)

时钟数据恢复,

DCS (DisplayCommandSet)

DCS是一个标准化的命令集,用于命令模式的显示模组。MIPI中应用

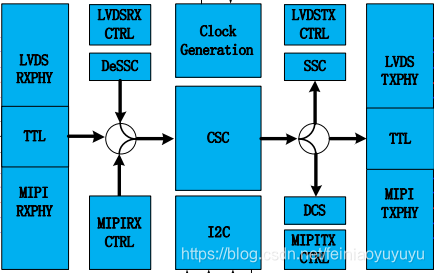

CSC(Color Space Conversion)

颜色空间转换,一般是将sRGB空间转换到YUV。

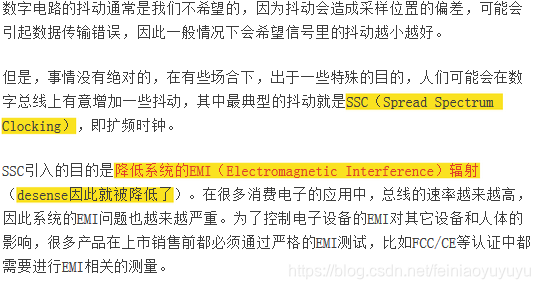

SSC(Spread Spectrum Clocking)

Gamma

在相机中通过Gamma与反Gamma操作,扩展存储的动态范围,并在显示设备上显示符合人眼亮度响应(对暗敏感)的图像。

宽动态技术

在亮与暗强烈对比下,让摄像机看到影像特点而运用的技术。即生成HDR图像。常见的方法是长短帧曝光,融合长帧的低位信息和短帧的高位信息。

PRBS:Pseudo-Random Binary Sequence,即伪随机码(伪随机二进制序列)

常用于高速串行通道的测试。为什么叫伪随机,因为其对于信道来说,码型看上去像是随机的,没有规律的出现,但实际上的码型是由生成多项式确定了的,并且有重复周期。

(equalizer)均衡器

在通信系统的基带或中频部分插入的,能够减少码间干扰, 起到补偿作用的滤波器。

扰码器(scambler)/解扰器(de-scambler)

设计数字通信系统时,必须考虑发送信息的信号特征,这些特征会影响到设计性能。总的来说,发送的信息应注意:(1).避免出现长串的0或1,否则对于从0、1交换点处提取位同步信息的系统,容易错判导致失去同步;(2).避免传输信号具有周期性,否则在多路传输的通信系统中容易造成串扰。

信道编码中的加扰器和解扰器便是完成上述功能,将发送信号处理成没有长传的0或1,并且数字信号最小周期足够长。对信号加扰处理可以使其统计特性接近于高斯白噪声的统计特性,在接收端需要用逆运算解扰恢复出原始发送序列。

FPD-Link--->FPD-LinkII--->FPD-Link III

FPD-Link采用 LVDS标准,单根双绞线的视频数据速率达到350Mbit/s。24-bit色彩数据FPD-Link需要使用的5个双绞线。

FPD-LinkII相对于FPD-Link,FPD-LinkII仅使用一个差分对来传输时钟和视频数据。使用LVDS转换为CML(current mode Logic)来达到高速率的数据传输---1.8Gbit/s.

FPD-LINK III (Flat Panel Display Link III) 与II的主要区别在于,在一个差分对上可以进行双向通行,除了传输视频数据外可以传输一些控制信号, 因此,FPD-Link III通过消除用于I2C和CAN总线等控制通道的电缆,甚至进一步降低了电缆成本。停止使用LVDS技术,而仅将CML用于串行化的高速信号。这使它可以轻松地在长度超过10m的电缆上以大于3 Gbit / s的数据速率工作。

LVDS中文名是低电压差分信号,它只是一个物理层的规范。在它的基础上有很多通信层标准,比如:FPD-Link。

FPD-Link是高速数字视频接口,主要用来传输视频数据。FPD-Link是第一次对LVDS规范的应用,由于FPD-Link是第一次对LVDS的成功使用,许多显示工程师LVDS术语来代替FPD-Link。

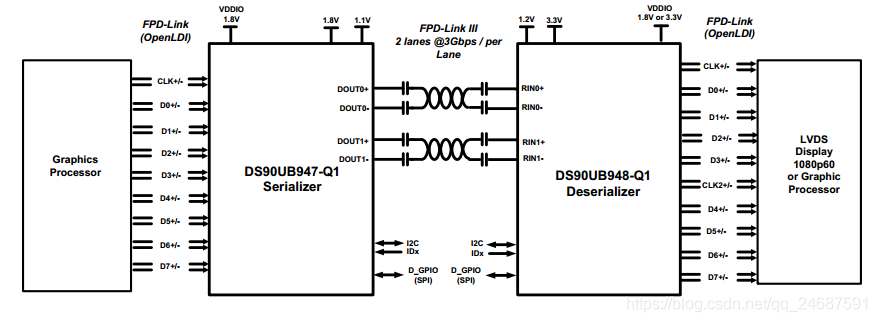

DS90UB948-Q1 是一款 FPD-Link III 解串器,与 DS90UB949A/949/947-Q1 串行器配合使用时可将单 通道或双通道 FPD-Link III 流转换成 FPD-Link (OpenLDI) 接口格式。

该解串器能够在具有成本效益的 50Ω 单端同轴或 100Ω 差分屏蔽双绞线 (STP) 电缆上 运行。

它能够从单通道或双通道 FPD-Link III 串行流中 恢复数据,然后将其转换为双像素 FPD-Link(8 个 LVDS 数据通道 + 时钟),最高可支持 2K (2048x1080) 的视频分辨率(24 位色深)。

这可为各 个支持 HDMI 的源(例如 CPU)间提供桥接,以便连 接到现有 LVDS 显示器或应用处理器。

FPD-Link III 接口支持通过同一条差分链路进行视频和 音频数据传输以及全双工控制(包括 I2C 和 SPI 通 信)。

通过两个差分对实现视频数据和控制的整合可减 小互连线尺寸和重量,并简化系统设计。

通过使用低压 差分信令、数据换序和随机生成最大限度地减少了电磁 干扰 (EMI)。

在向后兼容模式下,该器件在单一差分链 路上最高可支持 WXGA 和 720p 分辨率(24 位色 深)。

该器件将自动检测 FPD-Link III 通道并提供一种时钟对 齐和偏移补偿功能,无需任何特殊的训练模式。

这可在 互连线路(例如,PCB 布线)中出现不匹配问题、电 缆线对长度存在差异以及连接器不平衡时确保相位偏移在容差范围内。

原文链接:https://blog.csdn.net/dfysy/article/details/54346335

FPDLINK是TI设计的高速差分传输总线,主要用于传输图像数据,比如camera和显示数据。而且该标准还在不断的演进,从最初的一对线传输720P@60fps图像,到目前可以传输1080P@60fps,后续的芯片还可以支持更高的图像分辨率。传输距离也很远,能达到20米左右,非常适合汽车应用。

FPDLINK在传输的过程中有高速的前向通道,用于传输高速的图像数据和小部分的控制数据。也有速度相对较低的后向通道,用于传输反向的控制信息。前后向通信构成双向的控制通道,从而有了本文中将要讨论的FPDLINK中I2C的巧妙设计问题。

FPDLINK在使用中都是一个serializer和deserializer配对使用,CPU可以连接到serializer,也可以连接到deserializer,取决于具体的应用。比如,在camera应用中,camera sensor连接到serializer,将数据发送到deserializer,cpu则接收从deserializer发送过来的数据。在显示应用中,CPU则将数据发送给serializer,deserializer接收serializer的数据再传送给LCD屏进行显示。

CPU的i2c则可以连接到serializer或者deserializer的i2c。以下我们以上图的camera为例来讲解FPDLINK的i2c设计

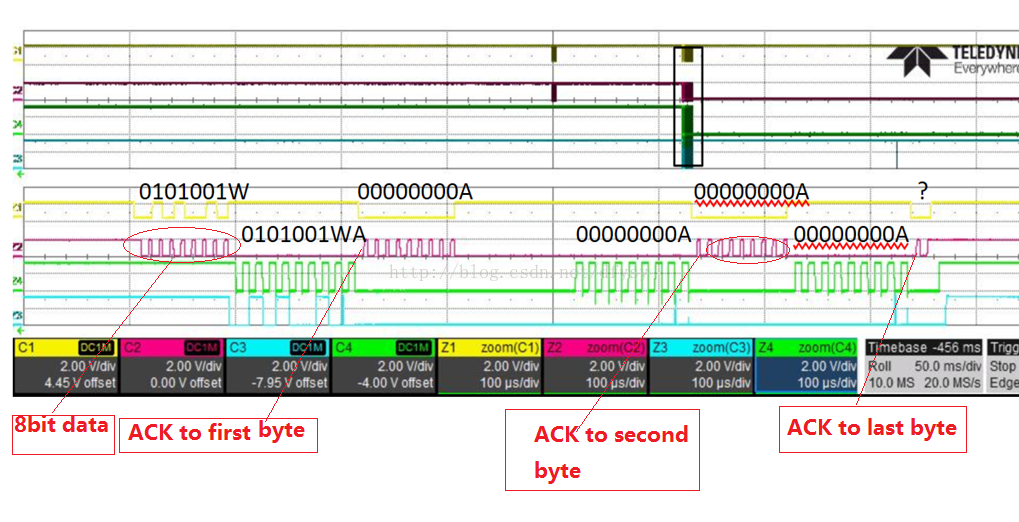

FPDLINK芯片接收CPU发送过来的I2C信息,将I2C信息通过FPDLINK传送到另外一端。我们知道,在i2c协议中,SDA是通过SCL来进行同步的。在一般应用中,在SCL的上升沿锁存数据,这就需要master或slave需要在SCL下降沿准备好数据。但是在FPDLINK里面,由于FPDLINK传输是有时间的,当master发送数据时不会有问题,最多slave收到的数比master发送的晚一些clock。但是slave往master回复的信息就会有问题,比如当slave回应ACK给master时,当ACK传输到master时,比slave发出的时间已经晚了,即已经经过了FPDLINK的延时,可能已经错过了SCL的上升沿。

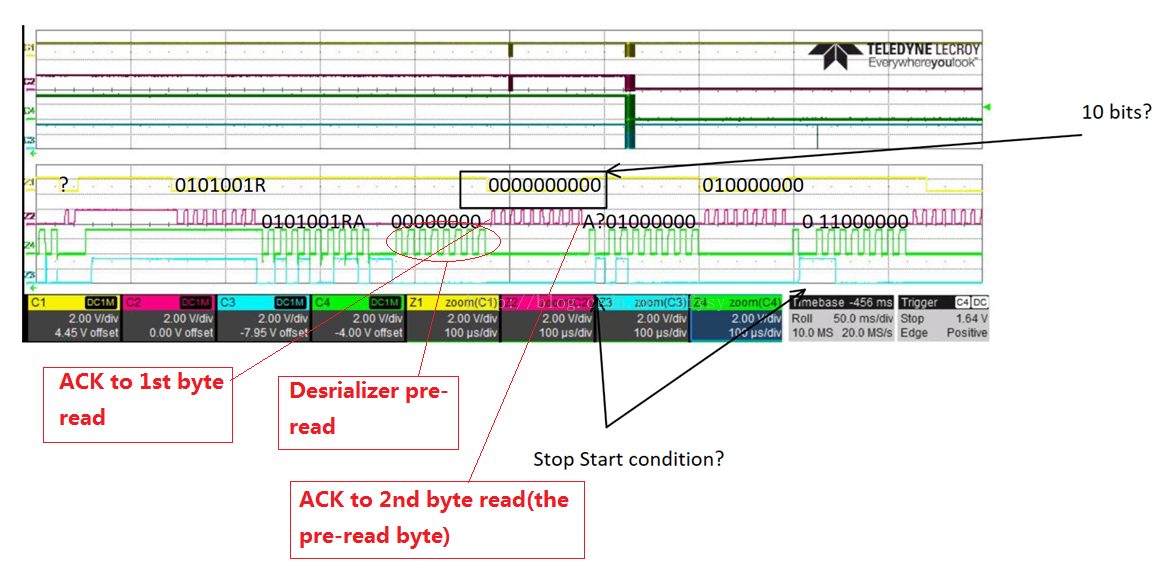

幸好i2c 协议考虑到了这种情况,i2c spec规定了一个属性叫i2c stretch,也就是i2c slave在没有准备好的情况下,在发送ACK之前可以将SCL拉低,这样master在尝试拉高SCL的时候就会失败,这样master就会一直尝试将SCL拉高,等slave将SCL释放以后,master就可以拉高SCL,接收ACK bit。因此在分析FPDLINK Slave端i2c 波形时,会发现每次发slave地址部分都只有8个bit,其实ACK会在后面进行回应,如下图

TI的FPDLINK芯片充分利用了这个特性,他并不是把接收到的i2c波形进行简单的转发(即保持和发送端相同的波特率),而是将收到的数据重新再按照FPDLINK芯片上设置的波特率重新发送。因此在分析FPDLINK Slave端i2c 波形时,需要注意这一点。可能CPU的i2c波特率是400K,但是FPDLINK slave接收端的i2c的波特率是100K或者1M,这个取决于FPDLINK芯片里面的SCL high和low的相关设置。

通过分析slave的i2c波形,还会发现一个挺有意思的现象,在读寄存器数据时,slave会自己先发出波形进行预先读取,比如要读取的寄存器地址为0x00的数据,会在波形上看到在当master发出写寄存器地址0x00以后,接着会发出slave的地址进行读(R/W = 1), slave 在发出该波形后,会紧接着发出8个SCL波形进行预先读取,而这8个clock在master侧是没有对应的,其实是master要在后面才发的,所以slave相当于先发了。

这个地方的设计是非常巧妙的,因为i2c协议规定,i2c stretch只能发生在第九bit,也就是ACK bit。如果slave回应了master的slave读的ACK,则当master发出正式读取数据的SCL时从机将没有机会拉住SCL,因为读取数据的SCL头八个波形是不允许拉的,而此时也没有收到从机的数据,所有就有问题了。

TI的做法是,既然前面有一次写的动作,后面又紧接着发的是一个读的slave地址,显然要读的是前面写的那个寄存器地址,因此将在master发送读的slave地址的第9bit ACK拉住,同时发出8个SCL进行寄存器读写,再释放SCL,master检测到SCL释放后,重新发送读数据clock,此时就有数据返回给CPU了。

虽然I2C可能是比较简单的总线协议之一,但是其中的某些设计还是非常非常巧妙的。

————————————————

版权声明:本文为CSDN博主「dfysy」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/dfysy/article/details/54346335

一、MIPI

MIPI(移动行业处理器接口)是Mobile Industry Processor Interface的缩写。MIPI(移动行业处理器接口)是MIPI联盟发起的为移动应用处理器制定的开放标准。

已经完成和正在计划中的规范如下:

二、MIPI联盟的MIPI DSI规范

1、名词解释

• DCS (DisplayCommandSet):DCS是一个标准化的命令集,用于命令模式的显示模组。

• DSI, CSI (DisplaySerialInterface, CameraSerialInterface

• DSI 定义了一个位于处理器和显示模组之间的高速串行接口。

• CSI 定义了一个位于处理器和摄像模组之间的高速串行接口。

• D-PHY:提供DSI和CSI的物理层定义

2、DSI分层结构

DSI分四层,对应D-PHY、DSI、DCS规范、分层结构图如下:

• PHY 定义了传输媒介,输入/输出电路和和时钟和信号机制。

• Lane Management层:发送和收集数据流到每条lane。

• Low Level Protocol层:定义了如何组帧和解析以及错误检测等。

• Application层:描述高层编码和解析数据流。

3、Command和Video模式

• DSI兼容的外设支持Command或Video操作模式,用哪个模式由外设的构架决定

• Command模式是指采用发送命令和数据到具有显示缓存的控制器。主机通过命令间接的控制外设。Command模式采用双向接口

• Video模式是指从主机传输到外设采用时实象素流。这种模式只能以高速传输。为减少复杂性和节约成本,只采用Video模式的系统可能只有一个单向数据路径

三、D-PHY介绍

1、 D-PHY 描述了一同步、高速、低功耗、低代价的PHY。

• 一个 PHY配置包括

• 一个时钟lane

• 一个或多个数据lane

• 两个Lane的 PHY配置如下图

• 三个主要的lane的类型

• 单向时钟Lane

• 单向数据Lane

• 双向数据Lane

• D-PHY的传输模式

• 低功耗(Low-Power)信号模式(用于控制):10MHz (max)

• 高速(High-Speed)信号模式(用于高速数据传输):80Mbps ~ 1Gbps/Lane

• D-PHY低层协议规定最小数据单位是一个字节

• 发送数据时必须低位在前,高位在后.

• D-PHY适用于移动应用

• DSI:显示串行接口

• 一个时钟lane,一个或多个数据lane

• CSI:摄像串行接口

2、Lane模块

• PHY由D-PHY(Lane模块)组成

• D-PHY可能包含:

• 低功耗发送器(LP-TX)

• 低功耗接收器(LP-RX)

• 高速发送器(HS-TX)

• 高速接收器(HS-RX)

• 低功耗竞争检测器(LP-CD)

• 三个主要lane类型

• 单向时钟Lane

• Master:HS-TX, LP-TX

• Slave:HS-RX, LP-RX

• 单向数据Lane

• Master:HS-TX, LP-TX

• Slave:HS-RX, LP-RX

• 双向数据Lane

• Master, Slave:HS-TX, LP-TX, HS-RX, LP-RX, LP-CD

3、Lane状态和电压

• Lane状态

• LP-00, LP-01, LP-10, LP-11 (单端)

• HS-0, HS-1 (差分)

• Lane电压(典型)

• LP:0-1.2V

• HS:100-300mV (200mV)

4、操作模式

• 数据Lane的三种操作模式

• Escape mode, High-Speed(Burst) mode, Control mode

•从控制模式的停止状态开始的可能事件有:

• Escape mode request (LP-11→LP-10→LP-00→LP-01→LP-00)

• High-Speed mode request (LP-11→LP-01→LP-00)

• Turnaround request (LP-11→LP-10→LP-00→LP-10→LP-00)

• Escape mode是数据Lane在LP状态下的一种特殊操作

•在这种模式下,可以进入一些额外的功能:LPDT, ULPS, Trigger

•数据Lane进入Escape mode模式通过LP-11→LP-10→LP-00→LP-01→LP-00

•一旦进入Escape mode模式,发送端必须发送1个8-bit的命令来响应请求的动作

• Escape mode 使用Spaced-One-Hot Encoding

•超低功耗状态(Ultra-Low Power State)

•这个状态下,lines处于空状态 (LP-00)

• 时钟Lane的超低功耗状态

•时钟Lane通过LP-11→LP-10→LP-00进入ULPS状态

•通过LP-10 → TWAKEUP →LP-11退出这种状态,最小TWAKEUP时间为1ms

• 高速数据传输

•发送高速串行数据的行为称为高速数据传输或触发(burst)

•全部Lanes门同步开始,结束的时间可能不同。

•时钟应该处于高速模式

• 各模操作式下的传输过程

•进入Escape模式的过程 :LP-11→LP-10→LP-00→LP-01→LP-00→Entry Code → LPD (10MHz)

•退出Escape模式的过程:LP-10→LP-11

•进入高速模式的过程:LP-11→LP-01→LP-00→SoT(00011101) → HSD (80Mbps ~ 1Gbps)

•退出高速模式的过程:EoT→LP-11

•控制模式 - BTA 传输过程:LP-11→LP-10→LP-00→LP-10→LP-00

•控制模式 - BTA 接收过程:LP-00→LP-10→LP-11

• 状态转换关系图

四、DSI介绍

1、DSI是一种Lane可扩展的接口,1个时钟Lane/1-4个数据Lane

• DSI兼容的外设支持1个或2个基本的操作模式:

• Command Mode(类似于MPU接口)

• Video Mode(类似于RGB接口)- 必须用高速模式传输数据,支持3种格式的数据传输

• Non-Burst 同步脉冲模式

• Non-Burst 同步事件模式

• Burst模式

• 传输模式:

• 高速信号模式(High-Speed signaling mode)

• 低功耗信号模式(Low-Power signaling mode) - 只使用数据lane 0(时钟是由DP,DN异或而来)。

• 帧类型

• 短帧:4 bytes (固定)

• 长帧:6~65541 bytes (可变)

• 两个数据Lane高速传输示例

2、短帧结构

• 帧头部(4个字节)

• 数据标识(DI) 1个字节

• 帧数据- 2个字节 (长度固定为2个字节)

• 错误检测(ECC) 1个字节

• 帧大小

• 长度固定为4个字节

3、长帧结构

• 帧头部(4个字节)

• 数据标识(DI) 1个字节

• 数据计数- 2个字节 (数据填充的个数)

• 错误检测(ECC) 1个字节

•数据填充(0~65535 字节)

• 长度=WC*字节

• 帧尾:校验和(2个字节)

• 帧大小:

• 4 + (0~65535) + 2 = 6 ~ 65541 字节

4、帧数据类型

原文链接:https://blog.csdn.net/weixin_34236334/article/details/112532655

LVDS: Low-Voltage Differential Signaling, 低电压差分信号技术,一种定义了高速数据传输接口电路电气特性的通用技术标准,而非协议,因为协议是特定于应用程序的。LVDS标准工作组选择仅定义驱动器和接收器的电气特性以确保LVDS能成为多用途接口标准,每个使用LVDS的应用程序都应参考适当的协议和互连标准。

LVDS接口利用非常低的电压摆幅(约350mv)在屏蔽双绞线(STP)或平衡电缆上传输差分信号,传输速率可达数十兆位(Gbps)。由于采用的是低电压和差分对传输,有效地实现了数据传输的高速率、低噪声、远距离、低功耗和可靠性。

1、LVDS接口电路

如图1所示,在液晶显示器中(以常见的汽车全尺寸液晶仪表屏为例),LVDS接口电路一般包括两个部分,即主机端的LVDS输出驱动接口电路(Serializer,串行器)和液晶面板侧的LVDS输入接口电路(Deserializer,解串器)。

图1 LVDS接口电路示意图

LVDS串行器将主机端的图形处理器(Graphics Processor)输出的并行RGB数据信号和控制信号转换成低电压串行LVDS信号,然后通过主机端和显示端之间的LVDS线束将信号传送到显示端的LVDS解串器。LVDS解串器再将串行信号转换为并行信号,送往液晶屏时序控制与行列驱动电路。

1)LVDS串行器和解串器需要成对使用,而且要求是同一家公司的芯片。目前主流的就两家:TI(德州仪器)和Maxim(美信)。他们各自在LVDS接口标准上开发了自家的串行通讯协议规范,TI的是FPD-LINK,Maxim是GMSL。

2)并行信号格式常用的有OpenLDI、HDMI、DP++等,主机端和客户端可以不一样。

3)LVDS线束是指差分屏蔽双绞线(STP)或单端同轴电缆(single-ended coaxial cable)。目前广泛使用的是罗森伯格(Rosenberger)公司的产品。

4)串行信号目前主要是指符合TI FPD-LINK和Maxim GMSL协议格式的信号。

2、LVDS传输格式

1)LVDS串行器在一个时钟脉冲周期内,每个数据通道都输出7bit的串行数据信号,而不是常见的8bit数据,如图2所示。该时钟遵循4:3占空比方案,以2个高电平位开始,紧接着3个低电平位,再2个高电平位结束。

图2

2)LVDS串行器输出信号的格式:即LVDS串行器输入的RGB数据,以及行同步信号HS、场同步信号VS、有效显示数据使能信号DE及其他信号在各个输出通道中数据位的排列顺序。

由于几大LVDS芯片生产厂家制定了各自不同的协议标准,因此存在着几种不同的LVDS输出数据格式,实际使用中要求LVDS串行器和解串器成对使用同一家的产品。如图3是TI芯片厂家的LVDS单通道24bit色的传输格式。

图3

3、LVDS常见名词或术语

1)差分对:指LVDS信号传输利用两个输出驱动来驱动两条传输线,一条携带信号,另一条携带它的互补信号。所需的信号就是两条传输线上的电压差,它携带要传输的信号信息。

2)信号对:指LVDS接口电路中,每一个数据传输通道或时钟传输通道的输出都为两个信号(正输出端和负输出端)

3)发送器(Source):产生包括文字、图形、图像、音频和视频数据集合的设备。

4)接收器(Sink):处理和显示数据的设备。

图4

5)FPD-LINK:Flat Panel Display Link,1996年由美国国家半导体公司(2011年被德州仪器TI收购)创建的基于LVDS标准的高速数字视频接口规范,支持从图形控制器到LCD面板的数据传输。

6)GMSL:Gigabit Multimedia Serial Link,Maxim公司基于LVDS标准开发的LVDS信号传输协议格式。

7)Forward channel:指从串行器Serializer到解串器Deserializer的高速数据传输通道。

8)Back Channel:又叫Reverse Channel,指从解串器Deserializer到串行器Serializer的低速数据传输通道。

————————————————

版权声明:本文为CSDN博主「是TuTu兔」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

93

93

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?