扫盲DDR的发展史:http://blog.chinaaet.com/justlxy/p/5100051912

http://blog.chinaaet.com/justlxy/p/5100052027

http://blog.chinaaet.com/justlxy/p/5100051913

https://www.cnblogs.com/shengansong/archive/2012/09/01/2666213.html

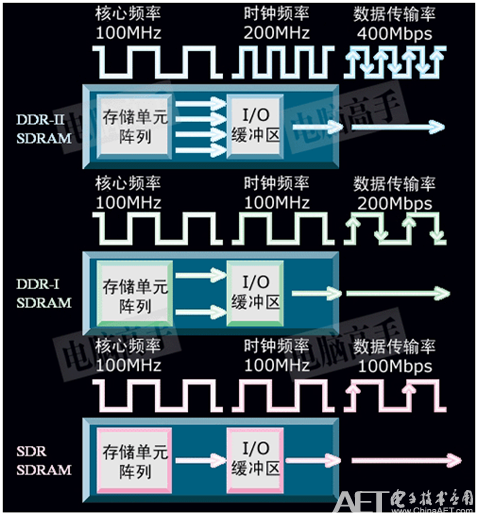

先介绍三个频率:

核心频率:即内部存储颗粒工作的频率,现在很难提升,提升的花费也很大。n-prefetch需要内部存储单元在核心频率下多读n倍的数据(通过多条线来实现)。

时钟频率:指的是I/O缓存区的时钟频率,根据n-bites的prefetch,时钟频率是核心频率的n/2倍。

等效频率:即外部接口需要的频率,由于采用上下沿双触发,所以是时钟频率的两倍。

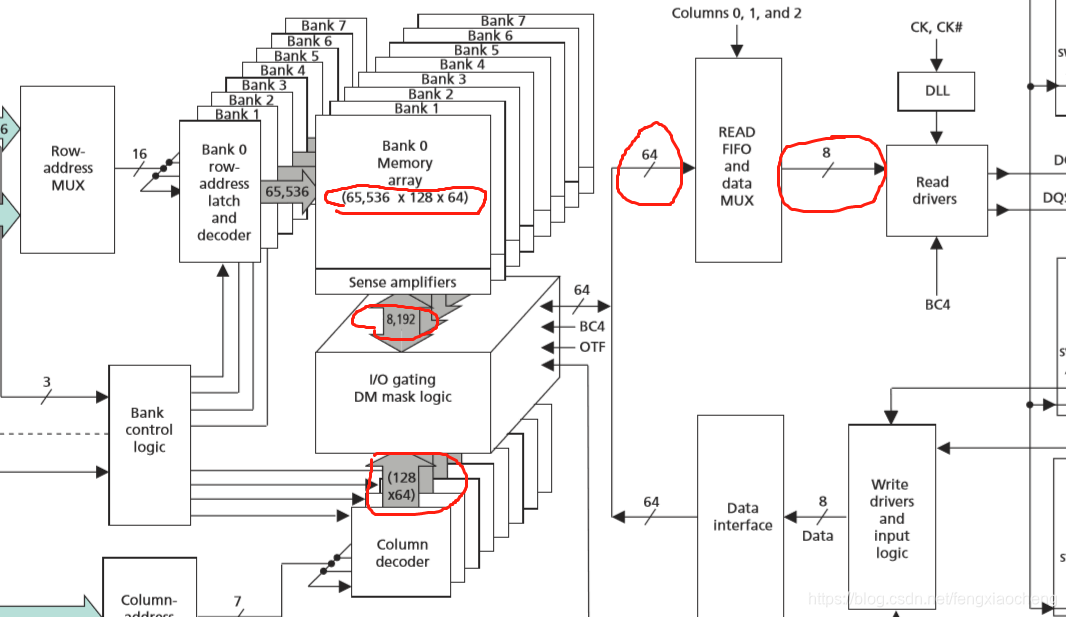

prefetch 字面意思就是预取,在DDR memory chip里面用的一个技术方案。DDR1 采用2n prefetch,DDR2采用4n prefetch,DDR3采用8n prefetch。所谓的n指的是chip对外的I/O width。以DDR3为例,它的IO gating buffer与FIFO的接口宽度是FIFO与外部IO的接口宽度的8倍。对于8bits位宽的 DDR3 MEMORY chip,为了满足8n prefetch,IO gating buffer的宽度要达到64 bits的位宽。

如下图所示,fifo两端的位宽就是8倍的差距,所以可以实现8bits的prefetch

这张图很能帮助理解:

1>SDRAM假设最开始是1bytes传输到I/O缓冲区,接着8bits一个周期传输到FIFO上,FIFO在传到外部。

2>DDR1,内部一个周期传输2bytes到I/O缓存区,由于上下沿都读取,所以连接外部的FIFO可以实现一个周期2bytes数据的传输,2-n prefetch 指的是内部通过增加线的方式,一下子传输了2byte数据出来。

3>DDR2,内部一个周期传输4bytes传输到I/O缓冲区,时钟频率变为两倍,再加上上下沿,FIFO接到外部是就变成了了内部的4倍。

4>DDR3,8bits的prefetch

5>DDR4,16bites的prefetch

Internal Rate: SDRAM内部时钟频率MHz

DDR1 SDRAM内部时钟频率=100-200MHz

DDR2 SDRAM内部时钟频率=100-266.67MHz

DDR3 SDRAM内部时钟频率=100-266.67MHz

DDR4 SDRAM内部时钟频率=133.33-266.67MHz

I/O Bus Clock: 总线时钟频率MHz

DDR1总线时钟频率=1*DDR1 SDRAM内部时钟频率=100-200MHz

DDR2总线时钟频率=2*DDR2 SDRAM内部时钟频率=200-533.33MHz

DDR3总线时钟频率=4*DDR3 SDRAM内部时钟频率=400-1066.67MHz

DDR4总线时钟频率=8*DDR4 SDRAM内部时钟频率=1066.67-2133.33MHz

Transfer Rate: 传输速率MT/s, 也即内存等效频率, 同时也是大众所熟知的频率, 如DDR4-3200

DDR1传输速率=2*DDR1 SDRAM内部时钟频率=200-400MT/s

DDR2传输速率=4*DDR2 SDRAM内部时钟频率=400-1066.67MT/s

DDR3传输速率=8*DDR3 SDRAM内部时钟频率=800-2133.33MT/s

DDR4传输速率=16*DDR4 SDRAM内部时钟频率=2133.33-4266.67MT/s

2、回到一个简单的问题上,如何计算DDR3 SDRAM的容量

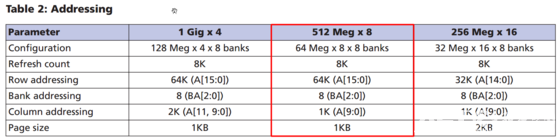

以Mircon的某型号DDR3 SDRAM为例:

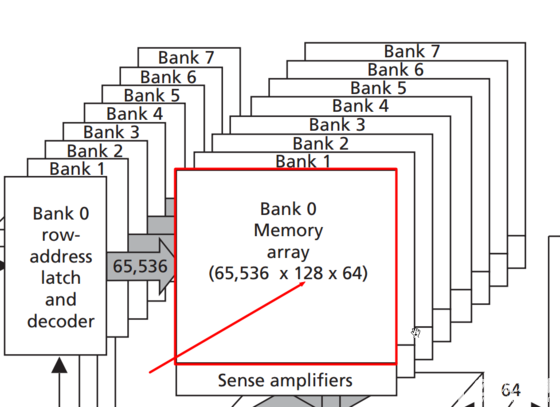

以图中红色部分的内容作为分析案例(8个bank,x8的Configuration):

计算方式一(错误):

64K*8*1K*8(Row Addressing * Bank Addressing * Column Addressing * x8 Configuration)= 4Gb(512 Megx8)。

大部分材料给出的都是这种错误的计算方法,误导了很多的初学者。这种计算方法咋一看好像是对的。但是,仔细推敲一下,便可以发现,按照计算方式一的逻辑,则认为每一个Cell的容量是1bit*8(x8 Configuration),即8bit。这与我们在第一部分所讨论的结果(一个Cell的容量为64bits,x8 Configuration下)不符。

当然,从某种角度来说,计算方式一也是正确的,因为分离出的Column Address的位数实际上是和prefetch对应的。比如DDR3 8-bit Prefetch对3bits的Column Address,DDR2 4-bit Prefetch对应的是2bits的Column Address。只是如果直接按照计算方式一来计算的话,对于初次接触DDR的人来说,理解起来存在一定的困难,这也是我写这一篇博文的原因。

下面给出正确的计算方式,并说明原因。

计算方式二(正确):

64K*8*(1K/8)*8*8(Row Addressing * Bank Addressing * (Column Addressing / 8) * x8 Configuration * 8-bit Prefetch)= 4Gb(512 Megx8)。

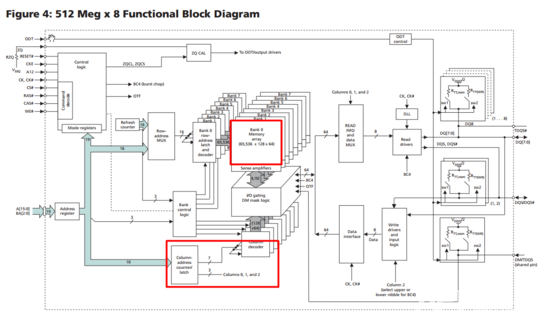

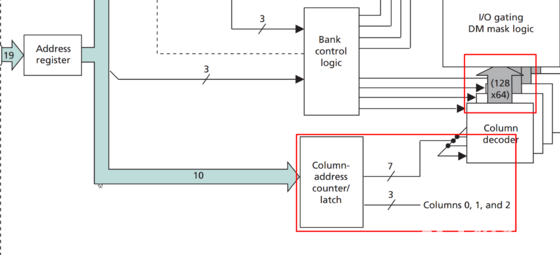

很多人都会问,为什么要把列地址寻址(Column Addressing)除以8呢?似乎计算方式二看起来更加不合理。接下来,我们先来回顾一下DDR3 SDRAM的结构框图(还是以Mircon的某型号为例):

大图可能看的不太清楚,下面来几个特写:

没错!你没有看错!10bit的Column Address的寻址能力只有128!!!刚好差了8倍(这就是我们在计算方式二中将Column Addressing除以8的原因)!

那么问题又来了,为什么Column Address的寻址能力只有128呢?莫急,请继续看下图:

在上图中,可以清晰地发现,10bits的Column Address只有7bits用于列地址译码!列地址0,1,2并没有用!!!

那么,问题又来了!……

列地址0,1,2,这3bits被用于什么功能了?或者是Mircon的设计者脑残,故意浪费了这三个bits?显然不是。

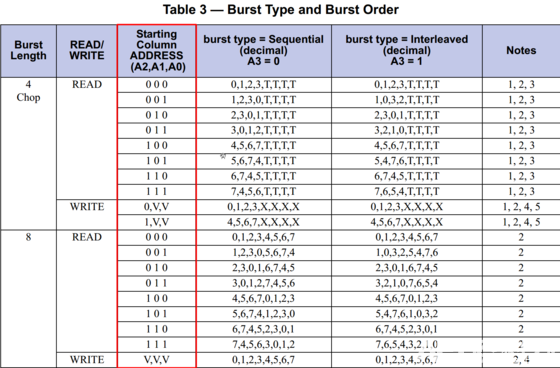

在JESD79-3规范中有如下的这个表格:

可以发现,Column Address的A2,A1,A0三位被用于Burst Order功能,并且A3也被用于Burst Type功能。由于一般情况,我们采用的都是顺序读写模式(即{A2,A1,A0}={0,0,0}),所以此时的A3的取值并无直接影响。

那么,问题又来了!……

Burst又是什么鬼呢?且看第三部分。

3、DDR中的Burst Length

Burst Lengths,简称BL,指突发长度,突发是指在同一行中相邻的存储单元连续进行数据传输的方式,连续传输所涉及到存储单元(列)的数量就是突发长度(SDRAM),在DDR SDRAM中指连续传输的周期数。上一部分讲到的Burst Type和Burst Order实际上就是关于Burst Length的读写顺序的配置。

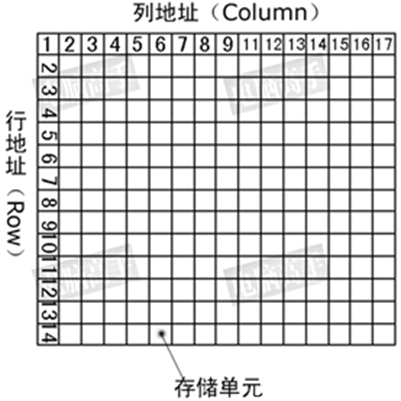

逻辑Bank

SDRAM的内部是一个存储阵列,要想准确地找到所需的存储单元就先指定一个(row),再指定一个列(Column),这就是内存芯片寻址的基本原理。

芯片位宽

SDRAM内存芯片一次传输率的数据量就是芯片位宽,那么这个存储单元的容量就是芯片的位宽(也是L-Bank的位宽);

存储单元数量=行数*列数(得到一个L-Bank的存储单元数量)*L-Bank的数量也可用M*W的方式表示芯片的容量,M是该芯片中存储单元的总数,单位是兆(英文简写M,精确值是1048576),W代表每个存储单元的容量,也就是SDRAM芯片的位宽,单位是bit;

DDR SDRAM内部存储单元容量是芯片位宽(芯片I/O口位宽)的一倍;

DDR2 SDRAM内部存储单元容量是芯片位宽的四倍;

DDR3 SDRAM内部存储单元容量是芯片位宽的八倍;

DDR4 SDRAM内部存储单元容量是芯片位宽的八倍。

为什么要说内部存储单元容量≠芯片位宽,这就是因为预读取,比如DDR3预读取8bits,所以存储单元容量是位宽的8倍,这样,一次就能读取8*64bits数据,由于内部时钟是等效时钟的1/8,所以吞吐量刚好相等,这也就可以在保持内部存储颗粒核心频率不变的情况下(核心频率的提高花费很大,而且很难),将等效的频率提高8倍。

3198

3198

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?