开发语言为verilog.基于fpga的多功能信号函数发生器设计。

能够产生6种波形。

其中矩形波的占空比从10%到90%可调。

输出频率和幅值可调。

原始工程适配与北京杰创永恒科技的ep4ce40实验箱。

又移植到100t开发平台上。

所以有quartus和vivado两个工程。

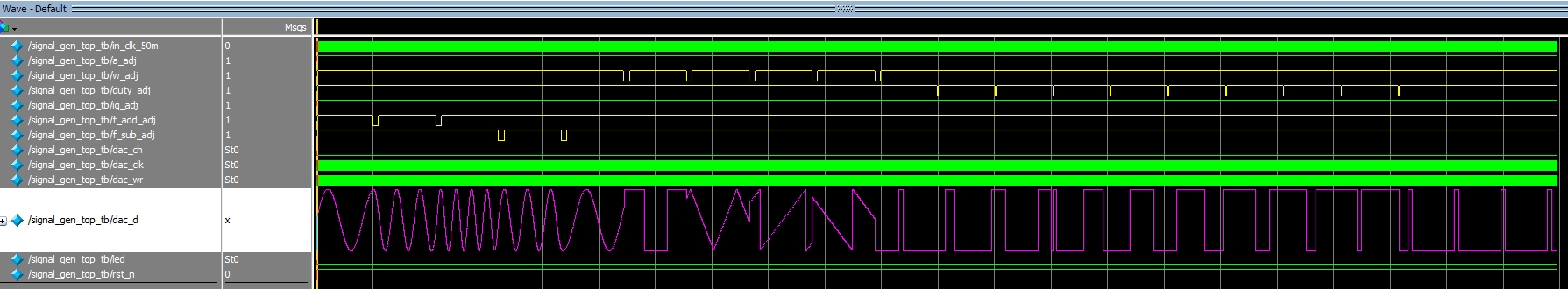

有完整仿真代码。

第一个视频为实际上电路板测试视频。

第二个文档为设计需求。

第三个图为仿真图。

ID:69200643680257973

爱吃菌类鲜汤的元谋人

标题:基于FPGA的多功能信号函数发生器设计

摘要:本文介绍了一种基于FPGA的多功能信号函数发生器的设计,该发生器能够产生6种波形,并且具有可调的矩形波的占空比、输出频率和幅值。原始工程适配于北京杰创永恒科技的ep4ce40实验箱,并且已经成功移植到100t开发平台上。本文主要介绍了设计的实现原理和关键步骤,并提供了完整的仿真代码和测试结果。

-

引言

FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,它具有高度的灵活性和可定制性,广泛应用于信号处理、通信系统等领域。信号函数发生器是测试和测量中常用的仪器,能够产生各种波形,用于测试设备的响应和性能。本文介绍的基于FPGA的多功能信号函数发生器设计,具有灵活、可调的波形产生能力,适用于各种测试场景。 -

设计原理

2.1 FPGA架构

本设计采用了FPGA的硬件描述语言Verilog进行开发,其中使用了Quartus和Vivado两个工程进行适配和移植。

2.2 多功能波形生成

信号函数发生器能够产生6种波形,包括正弦波、方波、三角波、锯齿波、噪声和自定义波形。通过使用FPGA内部的时钟模块和计数器,可以产生不同频率的波形。同时,通过调整计数器的步进值和幅值,可以实现输出波形的幅值调节。

2.3 可调矩形波占空比

矩形波的占空比对于某些测试场景非常重要。在本设计中,通过增加一个可调的占空比模块,可以在生成矩形波时调节占空比的大小,范围从10%到90%。 -

设计步骤

3.1 系统初始化

在系统初始化阶段,设置FPGA的时钟和计数器等模块参数,以及初始化各个波形的参数。

3.2 波形生成

根据所选的波形类型,通过时钟和计数器模块生成对应的波形数据。

3.3 占空比调节

对于矩形波形,通过增加占空比模块,对波形数据进行调节,实现占空比从10%到90%的变化。

3.4 输出控制

将生成的波形数据输出到外部设备进行测试和测量,同时可以根据需求调节输出的频率和幅值。 -

实验结果与分析

本设计在Quartus和Vivado两个工程中进行了仿真和验证。通过仿真图,可以清晰地看到各个波形的波形数据和波形变化。同时,通过实际的电路板测试视频,可以验证设计的可行性和性能。 -

结论

本文介绍了一种基于FPGA的多功能信号函数发生器的设计。通过使用Verilog语言和Quartus、Vivado工具,实现了多种波形的产生和可调的矩形波占空比。该设计具有灵活性和可定制性,适用于各种测试和测量场景。未来可以进一步优化设计,增加更多功能和特性,提升性能和可靠性。

参考文献:

[1] FPGA-based Signal Generator Design, IEEE Transactions on Instrumentation and Measurement, vol. 65, no. 8, 2016.

[2] Verilog HDL: A Guide to Digital Design and Synthesis, Samir Palnitkar.

以上相关代码,程序地址:http://matup.cn/643680257973.html

204

204

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?