1.interface

(1)interface可以在硬件环境和软件环境中传递,例如作为module的端口列表,也可以作为软件方法的形式参数。

![]()

(2)interface的优势

-

将有关信号封装在同个接口中,如果需要新添加信号,只需要在接口中定义这个信号,对于设计和验证环境都便于维护和使用。

-

由于接口既可以在硬件世界(module)中使用,又可以在软件世界(class)中使用。在软件世界中不能例化interface,但可以用指针找到interface的实例及其变量。

-

interface定义和module类似,它可以定义端口,也可以定义双相信号;可以使用initial和always,也可以定义function和task;在interface的端口列表中只需要定义时钟、复位等公用信号,或者不定义任何端口信号,转而在变量列表中定义各个需要跟DUT和TB连接的logic变量,为了简单,推荐使用logic来定义变量。

-

interface可以结合parameter(参数化方式)提高复用性。

(3)interface和module的不同

module中可以例化module和interface,但是interface不能例化module。

(4)interface的例化

2.竞争问题

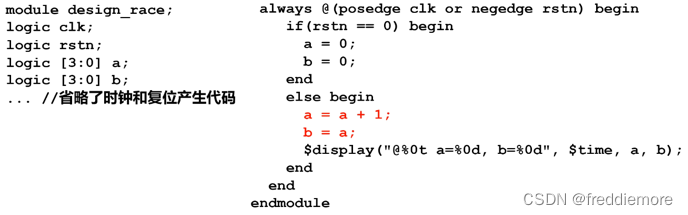

(1)竞争冒险问题(例子)

-

当显示a=1时,b也会显示1。

-

a会综合成4bit的reg,b综合为wire。

-

一拍中,b总和a的值一样。

(2)

-

在仿真行为中,为尽量避免时序电路中时钟和驱动信号的时序竞争问题,需要给出尽量明确的驱动时序和采样时序。

-

为了避免在RTL仿真行为中发生的信号竞争问题,建议通过非阻塞赋值或者特定的信号延迟来解决同步的问题。

3.delta-cycle与time-slot

(1)简述

-

默认情况下,时钟对于组合电路的驱动会添加一个无限最小时间(delta-cycle)的延迟,而该延迟无法用绝对时间单位衡量,它要比最小时间单位精度还小。一般最小时间为1ps。

-

在一个时间片(time-slot)中可以发生很多事情,时间片中包含了无数个delta-cycle。

-

仿真器中敲入命令"run 0",即是让仿真器运行一个delta-cycle的时间。

(2)例子

在45ns处,clk1在上升沿采样d1的数值为1,clk2在45ns处采样的数值2。

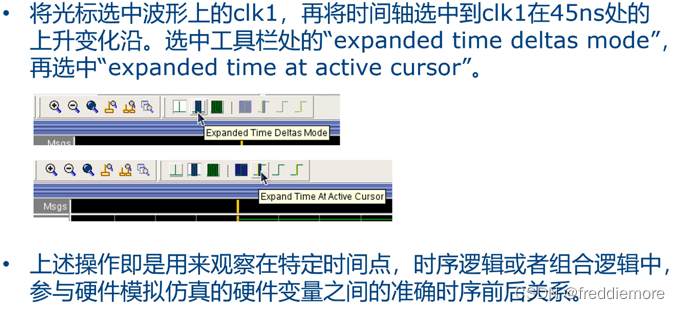

(3)在仿真软件中查看delta-cycle

(4)

其实就是说clk2是由clk1赋值的,而赋值的时总是延迟个delta-cycle,所以用clk1采样和用clk2采样则不同。

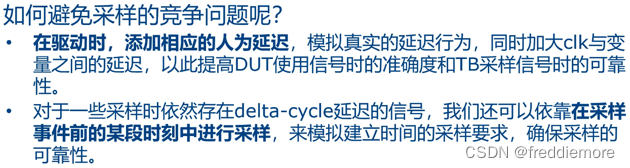

4.避免采样的竞争问题

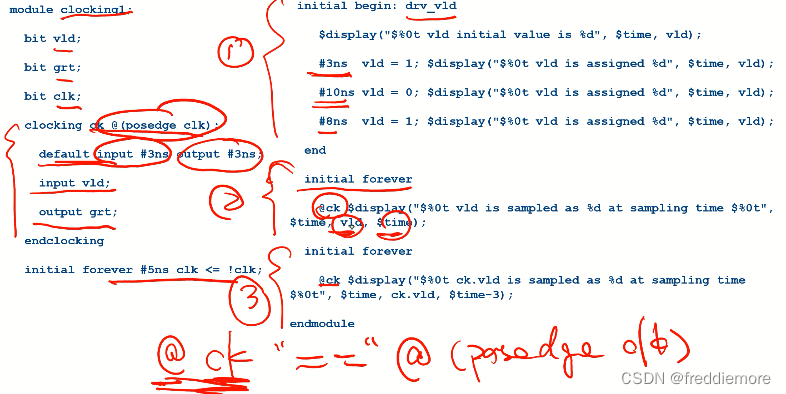

5.利用clocking (时序块)解决采样和驱动问题

(1)clocking可用在interface、program和module中,常见在interface中。

-

clocking中列举的信号不是自己定义的,而是应该由interface或者其它声明clocking的模块定义的。

-

clocking在声明完名字之后,应该伴随着定义默认的采样事件,即"default input/output event"。如果没有定义,则会默认地在clocking采样事件前的1step对输入进行采样,在采样事件后的#0(时钟片)对输出进行驱动。

-

除了定义默认的采样和驱动事件,也可以在定义信号方向时,用新的采样事件对默认事件做覆盖。

-

可定义多个clocking,且同个变量在不同的clocking中定义不同的方向。

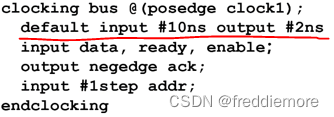

(2)clocking的定义:

-

第一行定义了一个clocking块bus,由clocking的上升沿来驱动和采样;

-

第二行指出了在clocking块中所有的信号默认情况下会在clocking事件(clocking上升沿)的前10ns对其进行输入采样,在事件的后2ns进行输出驱动;

-

第三行是声明了要对其采样的三个输入信号data, ready和enable信号,这三个信号作为输入,它们的采样事件即采用了默认输入事件(clock1上升沿前的10ns)。

-

第四行声明了要驱动的ack信号,而驱动该信号的事件是时钟clock1的下降沿,即覆盖了原有的默认输出事件(上升沿的后2ns);

-

第五行的addr,也采用了自身定义的采样事件,即clock1上升沿前的1step.文里的1step会使得采样发生在clock1上升沿的上一个时间片采样区域,即可以保证采样到的毅据是上一个时钟周期的数据。

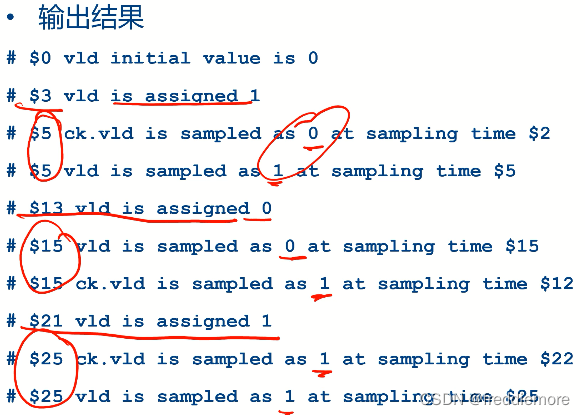

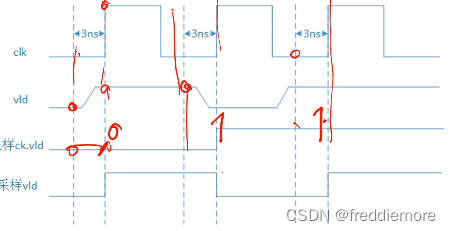

(3)利用clocking采样的例子

三个initial是并行的,第一个直接采样;第二个是在上升沿处采样;只有第三个是用clocking采样的(第二个不是)。

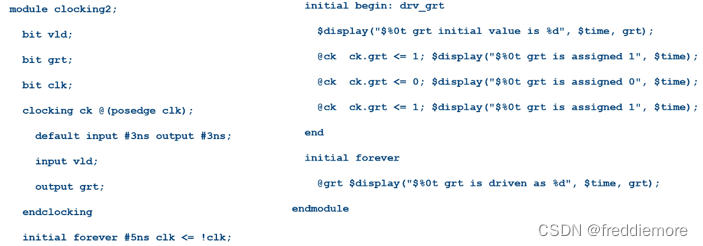

(4)利用clocking驱动的例子

同样地,利用clocking块通过一种类似于物理保持时间"的驱动方式,可以实现时钟沿叠加偏移量的延迟驱动效果。

6.测试的开始与结束

(1)仿真可以没有其他的激励,但是要有复位和时钟。

(2)即是只给设计提供复位和时钟信号,整个仿真也会一直持续下去。

7.用系统函数调用方法结束:

(1)$finish():结束仿真

(2)$stop:暂停仿真

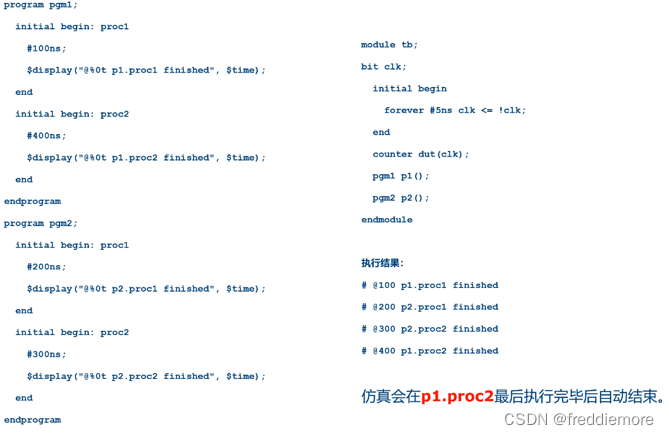

8.program隐式结束

(1)SV将每个program作为一个独立的测试,利用program来自动结束。

(2)如果TB中只有一个program,则会在执行完该program中最后一个initial过程块后自动结束仿真。如果TB中有多个program,那么等待所有program中最后一个initial过程块完成后,才能结束仿真。

(3)例子

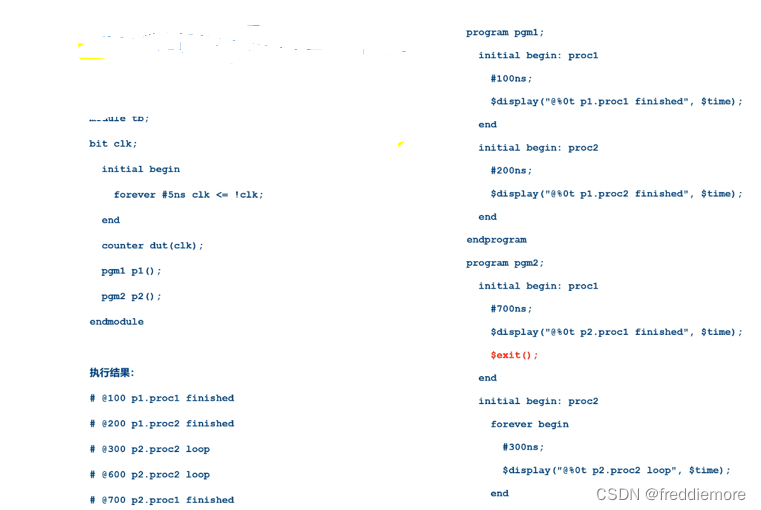

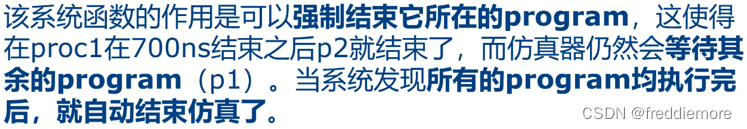

(4)遇到有的program中的initial语句块会一直运行下去,就可在目标program内置入系统函数$exit(),强制结束。待该program结束后,仿真器仍会等待其他program执行完毕后再结束仿真。

(5)program可以用来帮忙消除采样竞争问题以及自动结束测试用例。

(6)

641

641

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?