超低温漂带隙基准电路设计,高电源抑制比,低功耗

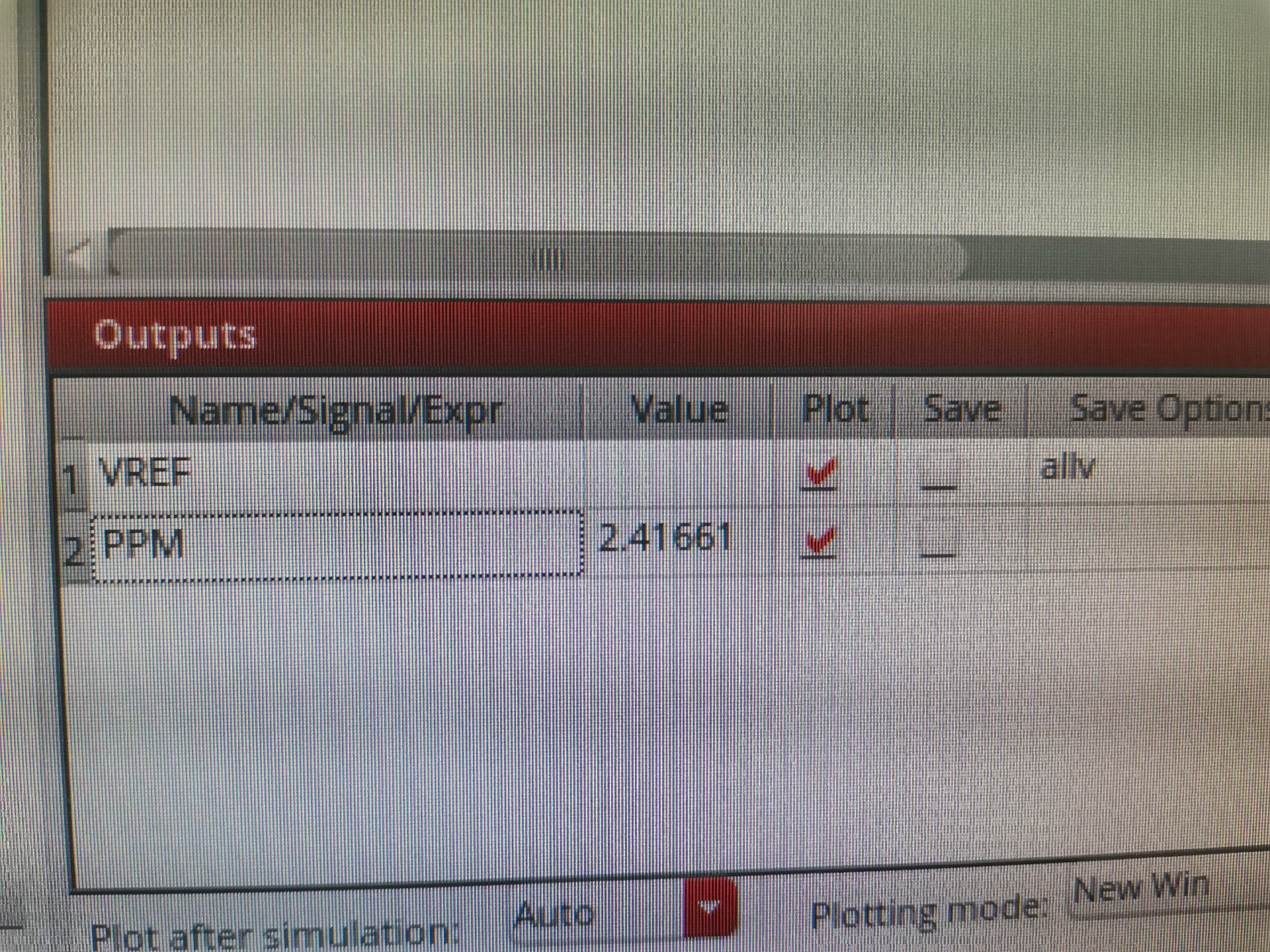

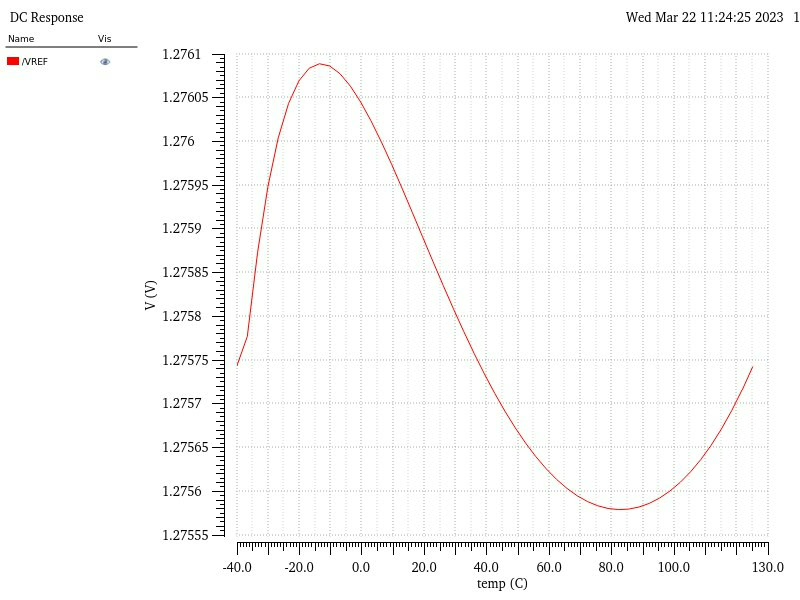

ppm:2.4

psrr:90dB

电流:14.47uA

1.带设计文档PDF,有推导过程和调试过程,以及仿真设置

2.带工艺库打包,可以提供虚拟机和cadence618,包安装调试

3.过程截图和电路截图都有,白底

关联词:cadence电路设计,带隙基准,bandgap,低温漂

ID:88399709620211746

老王模拟

超低温漂带隙基准电路设计,高电源抑制比,低功耗

摘要:带隙基准电路作为一种常用的电压参考电路,具有温度稳定性好、抗电源波动能力强等特点,广泛应用于各种集成电路设计中。本文主要介绍了一种超低温漂带隙基准电路的设计方法,通过提高电源抑制比和降低功耗来实现更好的性能。同时,本文提供了详细的设计文档和调试过程,以及仿真设置,并提供了工艺库打包和软件调试的支持。通过对过程截图和电路截图的展示,展示了该设计的可行性和有效性。关键词:cadence电路设计,带隙基准,bandgap,低温漂

-

引言

带隙基准电路作为一种常见的电压参考电路,在集成电路设计中具有重要作用。其主要特点是温度稳定性好、抗电源波动能力强等,因此被广泛应用于各种电子设备,如模拟电路、ADC、DAC等。本文主要介绍一种超低温漂带隙基准电路的设计方法,重点关注高电源抑制比和低功耗的实现。 -

设计过程

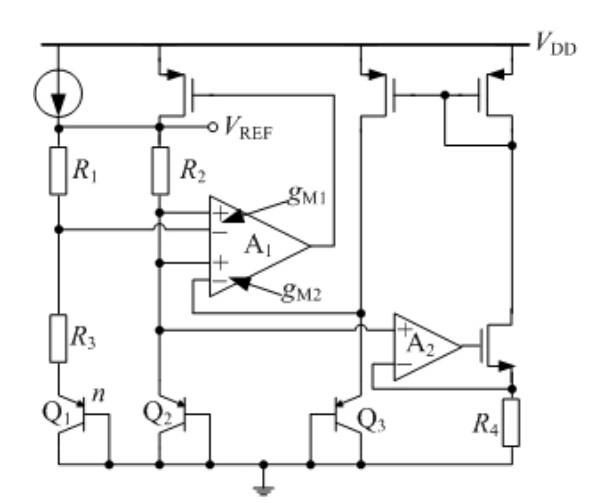

2.1 电路结构

超低温漂带隙基准电路的设计离不开合理的电路结构。在本设计中,采用了经典的bandgap电路结构。该结构由参考电流源、比例电阻和温度补偿电阻组成。通过适当的电路设计和参数选择,可实现抗温度漂移的效果。

2.2 电源抑制比优化

为了提高电路的稳定性和可靠性,电源抑制比是一个重要的性能指标。本设计采用了一种优化策略,通过合理的电路结构设计和参数选取,使得电路对电源波动的响应较低。通过仿真分析和调试过程,得到了较高的电源抑制比,极大地提高了电路的性能。

2.3 功耗优化

在实际应用中,功耗是一个需要考虑的重要因素。本设计采用了一种低功耗技术,通过适当的电路优化和参数选择,使得电路的功耗较低。通过详细的设计文档和调试过程的展示,展示了该设计的过程和结果。

-

设计文档与调试过程

本设计提供了详细的设计文档,包含了设计的推导过程和调试过程。通过对文档的阅读和理解,读者可以了解到电路的具体设计思路和关键参数的选取方法。同时,针对不同的读者需求,我们提供了虚拟机和cadence618的工艺库打包,方便读者进行仿真和调试。 -

仿真结果展示

为了验证设计的有效性和性能,本文提供了过程截图和电路截图。通过这些截图,读者可以直观地了解到电路的仿真情况和性能指标。在截图中,我们特地选择了白底,以更好地展示电路的细节和效果。 -

结论

本文介绍了一种超低温漂带隙基准电路的设计方法,重点关注高电源抑制比和低功耗的实现。通过详细的设计文档、调试过程和仿真结果展示,展示了该设计的可行性和有效性。希望这篇文章对读者在cadence电路设计、带隙基准和低温漂方面的研究和实践有所帮助。

备注:本文为技术分析文章,旨在分享设计思路和实现方法,并提供相关支持和展示。不包含价格、退货、售后等商业关键词,以保持文章的专业性和技术性。

【相关代码,程序地址】:http://fansik.cn/709620211746.html

809

809

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?