——以下均为学习笔记,如有错误请指出

一、 芯片制造流程

我的资源搜"半导体"可见晶圆的诞生学习笔记

芯片制造流程的主要干线为:原物料检验(Incoming Quality Assurance,IQA)、晶圆前段工艺(FEOL)监控、晶圆后段工艺(BEOL)监控、晶圆验收测试(Wafer Acceptance Test,WAT)、晶圆出货检验(Outgoing Quality Asurance,OQA)、晶圆良率测试(Chip Probing或Circuit Probing,CP)、芯片封装工艺监控、芯片最终测试(Final Test,FT)、芯片上板工艺监控(On-board Test)、系统级测试(System Level Test,SLT)和终端用户使用[4]。

主干线以上部分,是质量与良率(Yield)管理中需要用到的主要系统和方法;主干线以下部分,则是可靠性管理工作中所要用到的主要手法及管理要点。

二、良率、缺陷与分析(Yield,Defect & Analysis)

1. Yield 良率

解释:全公司最关心的指标,没有之一。指的是一片晶圆上,通过所有测试的、合格的芯片(Good Die)数量占总芯片数量的百分比。

要点:良率直接决定了公司的盈利。所有工程师的工作,无论是工艺开发、设备维护还是流程优化,最终目标都是为了提升和稳定良率。

介绍:在半导体生产制造的各个环节,都可能会引起最终产品的失效。 yield(良率,合格率)是一个量化失效的指标,通常也是工艺改善最 重要的指标。

在半导体生产制造中,yield定义为

在半导体生产制造中,yield定义为

yield可以基于晶粒(die)或者晶片(wafer)或者批次(lot)定义。

定义在wafer或者lot上的yield,一般反映生产工艺中的控制问题, 如操作人员的误操作,设备故障等,通常也称为生产线良率(line yield)。例如,生产线下线1000片wafer,最后由于各种原因报废 (scrap)20片wafer,那么line yield就等于98%。

2. Yield Excursion / Yield Crash (良率漂移 / 良率崩盘)

解释:指产品良率突然或持续地偏离正常基线(Baseline)。

要点:这是Fab里最紧急的警报。一旦发生,会立即成立跨部门的“作战小组”(Task Force)来解决问题。

3. D0 / Defect Density (缺陷密度)

解释:单位面积内的缺陷数量。D0是衡量工艺洁净度的核心指标。

要点:D0越高,良率越低。我们持续不断地工作,就是为了把D0降到最低。

4. Kill Ratio (致命率)

解释:某个特定类型的缺陷导致芯片最终失效的概率。

要点:并非所有缺陷都是致命的。一个大尺寸的颗粒落在有源区,Kill Ratio可能接近100%;而一个小缺陷落在非关键区域,可能就毫无影响。分析Kill Ratio有助于我们优先处理最致命的缺陷问题。

5. Systematic vs. Random Defect (系统性 vs. 随机性缺陷)

解释:系统性缺陷是有规律的、重复出现的,通常与光罩、设备或特定工艺步骤的设计相关。随机性缺陷是偶然的、无规律分布的,如环境中的颗粒。

要点:解决两者的思路完全不同。系统性缺陷需要从根源上(如修改OPC、优化Recipe)解决;随机性缺陷则需要改善设备维护和工厂环境。

6. In-line Inspection (在线检测)

解释:在生产过程中的关键步骤后,立刻用设备(如KLA的扫描仪)检查晶圆表面,而不是等到所有工序完成后。

要点:这能让我们在问题发生的早期就发现它,及时拦截有问题的晶圆,并快速定位问题工序,避免整批报废。

三、工艺术语介绍

1. 通用与生产控制 (General & Production Control)

-

>>> Fab(晶圆厂)

解释:Fabrication Plant的简称,就是我们整个制造工厂。

要点:不同的Fab有不同的代号(如Fab A, Fab B)和技术节点。

-

>>> Cleanroom(无尘室)

解释:我们进行芯片制造的核心区域。空气经过高效过滤,对尘埃粒子(Particle)有极其严格的控制。

要点:为什么要穿无尘服(Bunny Suit)?因为人体是最大的污染源。空气中一个微小的尘埃落在晶圆的关键区域,就可能导致整个芯片报废。无尘室有等级之分,如Class 1、Class 10,数字越小代表越洁净。

-

>>> lot (批次)

解释:生产的基本单位,通常是一盒(A Cassette / FOUP)晶圆,标准数量是25片。所有生产指令、数据追踪都以Lot为单位。

要点:你会整天听到“这个Lot跑到哪了?”、“查一下那个Lot的数据”。Lot ID是它的身份证号。

是晶圆的量化单位,一般一个晶片盒的晶圆为1个Lot;多个Lot可以组成一个Batch;一批晶片最多可以有25片,最少可以只有一片。

lotcode又叫 lot No. , lot No. 是 lot number的缩写,是“批号”的意思。厂家为了可以追溯和审查该批元器件的生产历史,所以每一批产品都有相应的的生产号码。生产批号是同一批元器件的编号。它是用于识别“批”的一组数字或字母加数字。一般的,根据批号可以追踪产品的生产情况(生产日期、质量等级、出厂时间、产地等等)。现在大多数企业都逐渐把元器件的生产日期和生产批号统一化。不同的原厂给定的lot number 和 D/C形式各不一样。

lot priority:每一批产品在加工的过程中被选择进机台的先后顺序

bullet lot:也叫做super hot lot,优先顺序为1,等级最高,必要时当lot在上一站加工时,本站要空着机台等待

hot lot:优先顺序为2

delay lot:优先顺序为3

normal lot:优先顺序为4,属于正常等级,按照正常派货

-

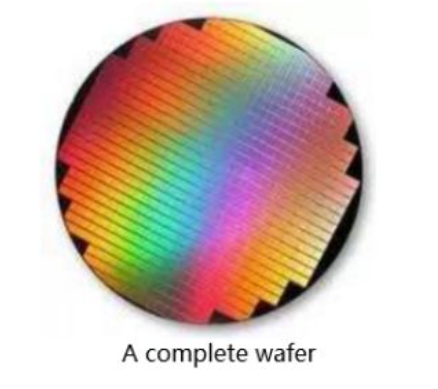

>>> wafer (晶圆)

解释:制造芯片的基底,通常是高纯度的硅片。我们所有的工艺步骤都是在这片圆形的“画布”上进行的。

要点:主流尺寸是8英寸(200mm)和12英寸(300mm)。尺寸越大,单片晶圆上能制造的芯片(Die)就越多,成本效益越高。

下图图片所示即为晶圆,由纯硅(Si)构成。一般分为6英寸、8英寸、12英寸规格不等,晶片就是基于这个wafer上生产出来的。晶圆是指硅半导体集成电路制作所用的硅晶片,由于其形状为圆形,故称为晶圆;在硅晶片上可加工制作成各种电路元件结构,而成为有特定电性功能的集成电路产品。

高纯度的多晶硅溶解后掺入硅晶体晶种,然后慢慢拉出,形成圆柱形的单晶硅。硅晶棒在经过研磨,抛光,切片后,形成硅晶圆片,也就是晶圆。目前国内晶圆生产线以 8英寸和 12 英寸为主。晶圆的主要加工方式为片加工和批加工,即同时加工1 片或多片晶圆。随着半导体特征尺寸越来越小,加工及测量设备越来越先进,使得晶圆加工出现了新的数据特点。同时,特征尺寸的减小,使得晶圆加工时,空气中的颗粒数对晶圆加工后质量及可靠性的影响增大,而随着洁净的提高,颗粒数也出现了新的数据特点。

-

>>> SPC(SStatistical Process Control / 统计过程控制)

解释:一套监控生产过程稳定性的工具,最常见的就是控制图(Control Chart)。

要点:当你看到某个参数的SPC图表“飘红”或“报警”,意味着这个工艺步骤可能失控(OOC, Out of Control),需要立即处理,否则会影响整个Lot的良率。这是我们工程师的“仪表盘”。

-

>>> die 晶粒(裸片 )

① 介绍:Die(裸片、裸晶、晶粒或晶片)是指从一整片圆形硅晶圆(Wafer)上,通过精密切割(Dicing)工艺分离下来的、单个含有完整集成电路(IC)功能的小方块,封装后就成为一个颗粒。每一片Die都是一个未经封装的、功能齐全的电路单元,比如一个CPU核心、一个GPU核心、一个存储器模块或一个射频收发器。

② 通俗理解:晶圆 (Wafer)是一张印满了邮票的大版纸。Die (晶粒)就是从这张大版纸上撕下来的那一枚枚独立的邮票。

③ 形态:通常是正方形或矩形,非常薄,表面有极其复杂的电路结构。

④ 材质:主要由高纯度单晶硅制成。

⑤ 状态:这是**未封装(Unpackaged)**的状态。它非常脆弱,直接暴露在空气中容易受到污染和物理损伤。

⑥ 单复数:它的单数是Die,复数是Dice或Dies。

⑦ Die的生命周期:

- 第1步:晶圆制造 (Wafer Fabrication)

一切始于一块高纯度的硅晶圆(Wafer)。在超净间(Cleanroom)里,通过光刻(Photolithography)、蚀刻(Etching)、薄膜沉积(Deposition)、离子注入(Ion Implantation)等数百道复杂工序,在晶圆表面制作出成千上万个完全相同的电路结构。此时,所有的Die还都连在一起,共同存在于晶圆之上,形成一个网格状阵列(Array)。

- 第2步:晶圆测试 (Wafer Probing / CP Test)

在切割之前,需要对晶圆上的每一个Die进行初步的电性测试。这个过程叫做晶圆探针测试(Circuit Probing, 简称CP测试)。探针卡(Probe Card)上的细小探针会接触到每个Die上的焊盘(Bond Pad),以检测其功能是否正常。测试不合格的Die会被标记下来(传统上是点上墨点,现在通常是在电子地图Wafer Map中记录),在后续工序中被废弃。这个步骤是为了尽早剔除次品,避免在无用的Die上浪费后续的封装成本。

- 第3步:晶圆切割 (Wafer Dicing)

通过CP测试的晶圆会被送到切割机(Dicing Saw)上。高速旋转的钻石切割刀会沿着Die之间的**切割道(Scribe Line)**进行精确切割,将一整片晶圆分离成数千个独立的Die。

- 第4步:芯片封装 (Packaging / Assembly)

从晶圆上取下的合格Die(此时称为Good Die),会被送入封装流程。

a. 固晶 (Die Attach):将Die的背面粘贴到封装基板(Substrate)或引线框架(Leadframe)上。

b. 引线键合 (Wire Bonding / Flip-Chip):建立Die与外部世界的电气连接。

引线键合 (Wire Bonding):用极细的金线或铜线,将Die上的焊盘(Bond Pad)连接到基板或引脚上。

倒装焊 (Flip-Chip):Die的正面(有电路的一面)直接朝下,通过其上的焊球(Solder Bump)直接连接到基板上。这种方式路径更短,性能更好,是高性能芯片的主流选择。

c. 塑封 (Molding):用环氧树脂(Epoxy)将Die、引线等所有内部结构包裹起来,形成我们常见的黑色“芯片”外观。这起到了保护内部Die、散热和方便安装的作用。

经过封装后,脆弱的Die就变成了坚固耐用的芯片(Chip)或IC,可以焊接到PCB板上使用了。

-

>>> layer(层)

晶圆上的一个结构层,即从 硅片 到 wafer 的一道道加工工序,例如氧化层就是一个layer。芯片的制造本质上就是循环重复“增层-光刻-刻蚀-去胶”的过程,一层一层地构建出整个三维结构。

-

>>> chip 芯片

半导体元件产品的统称。

一片载有Nand Flash晶圆的wafer,wafer首先经过切割,然后测试,将完好的、稳定的、足容量的die取下,封装形成日常所见的Nand Flash芯片(chip)。芯片一般主要含义是作为一种载体使用,并且集成电路经过很多道复杂的设计工序之后所产生的一种结果。

-

>>> wafer & die & chip & cell 关系

Wafer上一个小块晶片晶圆体学名die,封装后成为一个颗粒。通俗来讲就是,一整块叫 wafer(晶圆),里面单个叫 die(晶片)

品质合格的die切割下去后,原来的晶圆成了下图的样子,是挑剩下的Downgrade Flash Wafer。残余的die是品质不合格的晶圆。黑色的部分是合格的die,会被原厂封装制作为成品NAND颗粒,而不合格的部分,也就是图中留下的部分则当做废品处理掉。

封装前的单个单元的裸片叫做die。chip是对芯片的泛称,有时特指封装好的芯片。cell也是单元,但是比die更加小 cell <die< chip。

2. 核心工艺流程 (Core Process Flow)

-

>>> FEOL (Front-End-Of-Line / 前段工艺)

解释:指在晶圆上制造出基本元器件(主要是晶体管)的过程。从裸硅片开始,到第一个金属层(M1)之前的所有工序。

要点:这是芯片的“地基和主体结构”,决定了芯片最核心的电学性能。包括隔离、栅极、源漏极等结构。

-

>>> BEOL (Back-End-Of-Line / 后段工艺)

解释:在FEOL完成的晶体管之上,制造多层金属连线(Interconnects)的过程。

要点:好比为一座建好的大楼铺设复杂的电线、水管、网络系统。这些连线负责将亿万个晶体管连接起来,形成完整的电路。

-

>>> Process Flow / Route (工艺流程)

解释:制造一个特定产品的完整“菜谱”,包含了从头到尾几百上千个详细的工艺步骤。

要点:每个产品都有自己专属的Process Flow。工程师的任何改动都必须经过严格的验证,因为“牵一发而动全身”。

-

>>> Recipe (程序 / 配方)

解释:针对某个特定工艺步骤,在某台设备上执行的具体参数设置。例如,一次刻蚀的Recipe会规定气体流量、功率、压力、时间等。不同的产品(如芯片型号)、不同的工艺阶段,会对应不同的recipe。优化recipe是提升半导体良率的重要手段,通过精准设定参数,可减少工艺偏差导致的缺陷,从而提高合格芯片的比例。是机台加工不同产品时的对应程式;是由制造工程师提前在机台上设置,EAP控制生产时会自动根据货的类型选择并通知机台按照预选的方式进行加工;当wafer进入机台加工时,机台所提供的一定步骤,与每个步骤具备的条件。机台的recipe记录wafer进机台后先进哪个 chamber,再进哪个。每个chamber反应时要通过哪些气体。

要点:Recipe是工艺流程的基本执行单元,其稳定性和准确性至关重要。

3. 关键工艺模块 (Key Process Modules)

-

>>> Lithography (光刻)

Photoresist / PR (光刻胶):一种对特定光(如DUV、EUV)敏感的化学物质,涂在晶圆表面。

Mask / Reticle (光罩 / 掩膜版):一块刻有电路图形的石英板,是光刻的“底片”。

CD (Critical Dimension / 关键尺寸):电路中最细的线条宽度,是衡量工艺先进程度的关键指标。我们经常会用SEM去量CD。

核心任务:将电路设计图“印刷”到晶圆上。 -

>>> Etch(刻蚀)

Dry Etch (干法刻蚀):使用等离子体(Plasma)进行刻蚀,方向性好,能刻出垂直的陡峭侧壁。

Wet Etch (湿法刻蚀):使用化学液体进行腐蚀,成本低,但通常是各向同性的(会侧向腐蚀)。

核心任务:根据光刻留下的图形,精确地“雕刻”掉不需要的材料层。

-

>>> Thin Film(薄膜沉积)

CVD (Chemical Vapor Deposition):通过化学反应在晶圆表面生成薄膜。

PVD (Physical Vapor Deposition):通过物理方法(如溅射)将靶材原子“打”到晶圆上,常用于沉积金属。

核心任务:在晶圆上生长或沉积出各种材料层,如绝缘层(Oxide, Nitride)或导电层(Metal)。

-

>>> Implant / Diffusion(离子注入/扩散)

Dose (剂量):注入离子的总数量。

Energy (能量):决定离子注入的深度。

Anneal (退火):一个高温热处理步骤,用于激活注入的杂质并修复晶格损伤。

核心任务:将特定杂质原子(如硼、磷)掺入硅晶格中,改变其导电属性,形成N型或P型半导体。这是制造晶体管PN结的关键。

-

>>> CMP(Chemical Mechanical Planarization / 化学机械抛光)

核心任务:像砂纸一样,将晶圆表面打磨得极其平坦。

要点:为什么需要平坦?因为BEOL要堆叠很多层,如果下一层不平,上面的光刻就无法精确对焦,整个芯片就废了。CMP是实现多层金属互连的关键技术。

4. 量测与分析 (Metrology & Analysis)

-

>>> Metrology (量测)

解释:泛指所有在生产过程中的测量行为,比如测量薄膜厚度、CD尺寸等。

-

>>> SEM (Scanning Electron Microscope / 扫描电子显微镜)

解释:我们工程师的“眼睛”。用来拍摄晶圆上微观结构的高分辨率照片,用于检查图形、尺寸和形貌是否符合要求。

-

>>> Defect (缺陷)

解释:任何不应该出现在晶圆上的东西,如Particle(颗粒)、Scratch(划伤)、Pattern issue(图形问题)等。

要点:专门的扫描设备会在每个关键步骤后检查Defect,并生成Defect Map。分析这些缺陷是提升良率的重要工作。

-

>>> WAT (Wafer Acceptance Test / 晶圆允收测试)

解释:晶圆完成所有制造流程后的“期末考试”。通过探针台测试划片槽(Scribe Line)中的测试晶体管,获取Vth、Id_sat等关键电学参数。

要点:WAT数据直接反映了我们整个工艺流程的最终成果。WAT飘了(参数超出规格),就是我们PIE工程师最头疼的时刻,需要立刻启动调查。

-

>>> FA (Failure Analysis / 失效分析)

解释:当芯片失效或WAT参数异常时,进行的“尸检”工作。通过各种精密的物理和化学手段,层层剥茧,找到问题的根本原因(Root Cause)。

5. 工艺整合与控制 (Process Integration & Control)

-

>>> Process Window (工艺窗口)

解释:指某一个工艺参数(如曝光能量、刻蚀时间)可以变化的范围,在这个范围内,产出的结果(如CD、薄膜厚度)都能满足规格(Spec)。

要点:窗口越宽,代表工艺越稳定(Robust),抵抗各种生产波动的能力越强。我们做研发和优化的一个核心目标,就是想方设法“拓宽工艺窗口”。 -

>>> Process Margin (工艺裕度)

解释:与工艺窗口类似,但更强调当前操作点距离规格边界的“安全距离”。

要点:当有人说“这个工艺的Margin很小”,意思就是它非常敏感,稍微有点波动就可能产生废品,需要特别关注。

-

>>> DOE (Design of Experiments / 实验设计)

解释:一种科学的、高效的安排实验的方法,用于研究多个工艺参数对结果的影响。

要点:这是工程师解决复杂问题的“核武器”。当遇到棘手的良率问题或需要开发新工艺时,我们不会盲目试错,而是通过DOE来系统性地找到最优参数组合。你会经常听到“我们来下一批DOE Wafer”。

-

>>> TCAD (Technology Computer-Aided Design / 工艺与器件仿真)

解释:在计算机上模拟整个芯片制造过程和器件的电学行为。

要点:这是“虚拟晶圆厂”,可以在不动用真实晶圆的情况下,预测工艺变化对器件性能的影响。能极大节约研发成本和时间,是先进制程研发的必备工具。

-

>>> Scribe Line (划片槽)

解释:芯片(Die)与芯片之间的分割区域。在制造时,我们会在这个区域放置专门用于测试的结构。

要点:你看到的WAT数据,就是测试这些Scribe Line里的测试键(Test Key)得来的。它们是评估整片晶圆工艺均匀性和健康度的“哨兵”。

-

>>> Dummy Pattern / Fill Pattern (虚拟图形 / 填充图形)

解释:为了提高图形密度均匀性而在电路的空白区域额外增加的、无实际功能的图形。

要点:这对于CMP和Etch工艺至关重要。如果没有Dummy,图形稀疏区和密集区的研磨、刻蚀速率会不一致(称为Loading Effect),导致平坦度和尺寸控制变差。

6. 单元工艺进阶 (Advanced Module Terminology)

-

>>> Lithography & Etch (光刻与刻蚀)

① Overlay (套刻精度):衡量前后两层光刻图形对准的精确度。套刻不准,晶体管就无法正确形成,好比盖楼时二楼盖到了一楼的外面。

② Selectivity (选择比):在刻蚀过程中,目标材料的刻蚀速率与非目标材料(如光刻胶或下层薄膜)刻蚀速率的比值。

要点:选择比越高越好,意味着在刻穿目标层的同时,能最大程度地保护下面的功能层和光刻胶“面具”。

③ Profile / Taper Angle (轮廓 / 斜角):

刻蚀后侧壁的形貌。可以是垂直的(Anisotropic),也可以是倾斜的(Tapered),甚至是各向同性的(Isotropic)。

要点:不同的应用需要不同的Profile。例如,接触孔(Contact)需要垂直的侧壁以保证良好填充,而某些斜坡结构则需要特定的角度。

④ OPC (Optical Proximity Correction / 光学邻近效应校正):

在光罩上对图形进行预先的微小扭曲和变形,以补偿光刻过程中因光学衍射导致的图形失真。

要点:没有OPC,你设计的矩形在晶圆上可能会变成哑铃形。这是保证图形保真度的关键。

-

>>> Thin Film & Thermal (薄膜与热处理)

① Step Coverage (台阶覆盖率):

薄膜沉积在有高低不平结构的表面时,其在台阶侧壁的厚度与在平坦表面厚度的比值。

要点:差的Step Coverage会导致连接孔内金属断裂或绝缘层空洞,是可靠性的杀手。ALD(原子层沉积)技术就是因其完美的Step Coverage而备受青睐。

② Stress (应力):

薄膜内部存在的张应力(Tensile)或压应力(Compressive)。

要点:过大的应力会导致晶圆弯曲(Bow/Warp),甚至薄膜开裂、剥落。但我们也会利用应力来提升器件性能,这就是“应变工程”(Strain Engineering)。

③ RTA (Rapid Thermal Anneal / 快速热退火):

一种热处理技术,能在几十秒内将晶圆快速升至高温再快速降温。

要点:相比传统炉管(Furnace)几小时的处理,RTA能实现相同的激活/修复效果,同时有效控制杂质的过度扩散,对于尺寸微缩至关重要。

7. 设备与运营 (Equipment & Operations)

-

>>> MES (Manufacturing Execution System / 制造执行系统)

解释:Fab的“大脑”和“神经中枢”。它追踪每一个Lot的实时位置,控制设备执行正确的Recipe,收集海量的生产数据。

要点:工程师通过MES系统下指令、查数据、Hold Lot。你每天的工作都离不开它。 -

>>> PM (Preventive Maintenance / 预见性维护)

解释:设备工程师定期对设备进行的清洁、保养和更换耗材的工作。

要点:就像汽车需要定期保养一样。高质量的PM是保证设备稳定运行、降低D0的基础。PM后的设备状态恢复,是我们工艺工程师需要密切监控的。

-

>>> Hold Lot (扣留批次)

解释:由于发现异常(如SPC OOC、量测超标、高Defect),通过MES系统将一个Lot暂停在当前步骤,禁止其继续流片。

要点:这是止损的关键动作。Hold住的Lot需要工程师进行分析和判定(Disposition),决定是放行(Release)、报废(Scrap)还是重工(Rework)。

-

>>> OOC / OOS (Out of Control / Out of Spec)

解释:OOC指SPC图上的数据点超出了控制线(UCL/LCL),表明过程发生波动,但结果可能仍在规格内。OOS指测量结果超出了工程规格(USL/LSL),意味着产品已经不合格。

要点:OOC是预警,需要调查原因。OOS是事故,通常需要立即Hold Lot。

8. 其他 oth

-

>>> port 前台

指机台上货的一个平台,晶圆在加工之前先放在Port上,机台在加工时会用自动手臂一片一片提取在内仓进行加工

-

>>> stocker 仓库

存放晶盒(Cassette,是用来装晶圆的盒子,是一个个分离的插槽组成;一般一个晶盒可插入25片晶圆;晶圆在加工时都是以晶盒为单位进行的)的仓库,这种仓库有自动控制系统,可以自动存取。

-

>>> particle 含尘量/微尘粒子

-

>>> wip (work in process 在制品)

晶片从投入到晶片产出,FAB内各站积存了相当数量的晶片,统称FAB内的wip

-

>>> dummy wafer 挡片(假片)

挡片的两种用途:① 暖机 ② 补足机台内应摆晶片而未摆的空位置

-

>>> spec 规格(specification)

产品在加工机台过程中,每一站均设定规格。机台加工后,产品或控片经由量测,量测该产品加工后是否在规格内。若超出规格(out of spec),必须通知将产品hold,并同时通知制程工程师来处理,必要时机台要停工,重新monitor,确定量测规格,以提升制程能力

-

>>> wafer id

每一片晶片自己的晶片刻号(一般都刻在notch处)

-

>>> lot id

每一批晶片自己的批号

-

>>> product id

各个独立的批号可共用同一个型号

-

>>> notch 缺口

四、封装领域的常见专业术语

1. 封装类型

-

>>> DIP (Dual In-line Package) - 双列直插封装

特点:引脚从封装两侧伸出,呈两排平行排列,可直接插入PCB孔中

优点:易于手工焊接和更换,机械强度高

缺点:体积大,不适合高密度装配

应用:早期微处理器、存储器,现多用于原型开发

-

>>> SOP/SOIC (Small Outline Package/IC) - 小外形封装

特点:引脚从两侧伸出并向外弯曲,贴装在PCB表面

引脚间距:典型1.27mm

优点:比DIP体积小50-70%,适合自动化生产

应用:模拟IC、小规模数字IC

-

>>> QFP (Quad Flat Package) - 四边引脚扁平封装

特点:四边都有引脚,呈鸥翼型向外伸展

引脚数:32-304不等

引脚间距:0.8mm、0.65mm、0.5mm、0.4mm

应用:微控制器、DSP、FPGA

-

>>> QFN (Quad Flat No-lead) - 四边无引脚扁平封装

特点:引脚在封装底部,四周有裸露焊盘

优点:体积小、散热好、电气性能优良

中心焊盘:通常有大面积散热焊盘

应用:射频IC、电源管理IC

-

>>> BGA (Ball Grid Array) - 球栅阵列封装

特点:底部布满焊球,呈阵列排布

焊球间距:1.27mm、1.0mm、0.8mm、0.65mm、0.5mm等

优点:I/O密度高、电气性能好、散热性能好

缺点:需要专业设备焊接和检测

应用:CPU、GPU、FPGA、大规模ASIC

-

>>> CSP (Chip Scale Package) - 芯片级封装

定义:封装尺寸不超过芯片面积的1.2倍

特点:接近芯片实际大小

优点:最小化封装体积,优化电气性能

应用:手机、可穿戴设备等空间受限产品

-

>>> WLCSP (Wafer Level CSP) - 晶圆级芯片尺寸封装

特点:在晶圆状态完成封装,封装等于芯片大小

工艺:重布线→焊球植球→切割

优点:最小尺寸、最短互连、批量生产

应用:手机射频开关、电源管理IC

-

>>> SiP (System in Package) - 系统级封装

概念:将多个芯片、被动元件集成在一个封装内

优点:缩小体积、缩短互连、提高性能

技术:可结合引线键合、倒装、TSV等技术

应用:手机、物联网模块

-

>>> PoP (Package on Package) - 堆叠封装

结构:上下两个封装垂直堆叠

典型组合:上层Memory + 下层Logic

优点:节省PCB面积、缩短信号路径

应用:智能手机AP+DRAM组合

-

>>> FC-BGA (Flip Chip BGA) - 倒装芯片球栅阵列封装

特点:芯片倒装连接到基板,底部BGA焊球

优点:最短互连路径、最佳电气性能、良好散热

应用:高性能CPU、GPU、AI芯片

2. 封装工艺术语

-

>>> Die Attach - 芯片贴装

定义:将芯片固定到引线框架或基板上的工艺

材料:导电胶(银胶)、绝缘胶、焊料、DAF(Die Attach Film)

要求:良好的粘接强度、导热性、应力缓冲

设备:Die Bonder

-

>>> Wire Bonding - 引线键合

定义:用金属线连接芯片焊盘与封装引脚

材料:金线(15-50μm)、铜线、铝线

方法:球焊、楔焊

参数:键合力、超声功率、温度、时间

-

>>> Flip Chip - 倒装芯片技术

原理:芯片正面朝下,通过凸点直接连接基板

凸点类型:焊料凸点、铜柱凸点、金凸点

优势:最短互连、高I/O密度、良好散热

挑战:CTE匹配、底部填充工艺

-

>>> Molding - 塑封

目的:保护芯片和键合线免受机械损伤和环境影响

工艺:Transfer Molding(传递模塑)、Compression Molding(压缩模塑)

温度:175°C左右

关键:避免金线变形、减少应力

-

>>> Lead Frame - 引线框架

材料:铜合金(C194、C7025)、Alloy42

工艺:冲压或蚀刻

表面处理:镀银、镀NiPdAu、镀锡

作用:支撑芯片、电气连接、散热

-

>>> Substrate - 基板

类型:有机基板:BT树脂、FR4;陶瓷基板:氧化铝、氮化铝;金属基板:铝基、铜基;

层数:2层到16层以上

功能:电气互连、机械支撑、散热

-

>>> Underfill - 底部填充

目的:增强倒装芯片焊点可靠性

材料:环氧树脂+填料

工艺:毛细管流动、预成型、模塑底充

作用:应力缓冲、防潮、增强结合力

-

>>> Die Saw/Dicing - 晶圆切割

方法:机械切割、激光切割、等离子切割

刀片:金刚石刀片,厚度20-35μm

要求:避免崩边、裂纹、污染

新技术:Stealth Dicing(隐形切割)

-

>>> Solder Ball - 焊球

材料:有铅:Sn63Pb37,无铅:SAC305(Sn96.5Ag3.0Cu0.5)、SAC405

直径:0.1mm-0.76mm

工艺:植球、印刷、电镀

检验:共面性、球径、缺失

-

>>> Reflow - 回流焊接

温度曲线:预热→保温→回流→冷却

峰值温度:有铅220°C,无铅250°C

气氛:氮气保护减少氧化

关键:防止温度冲击、控制升温速率

3. 材料相关术语

-

>>> EMC (Epoxy Molding Compound) - 环氧塑封料

成分:环氧树脂+固化剂+填料(二氧化硅)+添加剂

特性:低应力、低吸湿、高玻璃化温度(Tg)

填料含量:85-92%

发展趋势:Green EMC(无卤无锑)

-

>>> Die Attach Adhesive - 芯片贴装胶

类型:导电胶:银填充环氧胶,绝缘胶:纯环氧胶,焊料:AuSn、SnAgCu

性能要求:低应力、高导热、长期可靠性

-

>>> Solder Mask - 阻焊层

作用:保护PCB线路、防止焊接短路

颜色:绿色最常见,也有黑、白、蓝、红等

工艺:丝印、光成像

厚度:20-30μm

-

>>> TIM (Thermal Interface Material) - 导热界面材料

类型:导热膏、导热垫、相变材料、液态金属

导热系数:1-10 W/m·K不等

应用:芯片与散热器之间

要求:低热阻、长期稳定性

-

>>> Cu Pillar - 铜柱

结构:铜柱+焊帽(SnAg)

高度:40-100μm

优点:更细间距、更好电气性能、电迁移抗性

应用:先进CPU、GPU倒装封装

-

>>> RDL (Redistribution Layer) - 重布线层

功能:重新布局I/O位置,实现扇入/扇出

材料:铜线路+聚酰亚胺绝缘层

线宽/间距:2-20μm

应用:WLCSP、Fanout封装

-

>>> TSV (Through Silicon Via) - 硅通孔

定义:贯穿硅片的垂直电气连接

直径:5-50μm

深宽比:10:1到20:1

应用:3D IC、CMOS图像传感器、HBM

-

>>> Interposer - 中介层

材料:硅、玻璃、有机材料

功能:连接不同芯片,实现高密度互连

特点:含有TSV和RDL

应用:2.5D封装、异构集成

4. 测试与可靠性术语

-

>>> MSL (Moisture Sensitivity Level) - 湿度敏感等级

等级:MSL1(无限期)到MSL6(必须6小时内使用)

标准:J-STD-020

存储:MSL2以上需要干燥包装

烘烤:超期需要125°C烘烤去湿

-

>>> Delamination - 分层

定义:材料界面分离

位置:芯片/EMC、EMC/引线框架、EMC/基板

原因:湿气、热应力、污染

检测:SAT(超声扫描)

-

>>> Wire Sweep - 金线偏移

原因:塑封时树脂流动造成金线移位

后果:短路、断路

预防:优化金线弧度、控制塑封参数

标准:偏移量 <金线间距的1 < pan>

-

>>> Die Crack - 芯片裂纹

类型:正面裂纹、背面裂纹、边缘裂纹

原因:机械应力、热应力、ESD

检测:光学显微镜、SAT

影响:功能失效、可靠性降低

-

>>> Solder Joint - 焊点

质量指标:润湿角度、填充高度、IMC厚度

缺陷类型:冷焊、虚焊、枕头效应、空洞

可靠性:温度循环、跌落测试

失效模式:疲劳裂纹、脆性断裂

-

>>> Thermal Resistance - 热阻

θJA:结到环境热阻(°C/W)

θJC:结到壳热阻(°C/W)

θJB:结到板热阻(°C/W)

测量标准:JEDEC JESD51系列

应用:计算结温,评估散热方案

-

>>> CTE (Coefficient of Thermal Expansion) - 热膨胀系数

单位:ppm/°C

典型值:硅:2.6 ppm/°C,铜:17 ppm/°C,FR4:15-17 ppm/°C,EMC:8-20 ppm/°C

影响:CTE失配导致应力和翘曲

-

>>> Void - 空洞

位置:焊点、底充、贴片胶

标准:一般要求<25%焊点面积

原因:助焊剂挥发、湿气、工艺控制

检测:X-ray检查

5. 尺寸参数术语

-

>>> Pitch - 间距

定义:相邻引脚或焊球中心距离

趋势:1.27mm→1.0mm→0.8mm→0.5mm→0.4mm→更细

挑战:PCB加工能力、焊接工艺

影响:决定封装I/O密度

-

>>> Stand-off Height - 离板高度

定义:BGA/CSP封装底部到PCB距离

典型值:0.1-0.5mm

影响:底充工艺、清洗、检查

趋势:越来越低,挑战增大

-

>>> Package Body Size - 封装体尺寸

表示:长×宽×高(mm)

公差:±0.1-0.2mm

趋势:持续小型化

标准:JEDEC定义标准尺寸

-

>>> Die Size - 芯片尺寸

表示:长×宽(mm或mil)

趋势:工艺进步使芯片面积缩小

Pad Pitch:焊盘间距,影响封装选择

Scribe Line:切割道宽度,60-120μm

6. 先进封装术语

-

>>> 2.5D/3D IC - 2.5维/3维集成电路

2.5D:芯片并排放置在interposer上

3D:芯片垂直堆叠,通过TSV连接

优势:高带宽、低功耗、小尺寸

挑战:散热、测试、成本

-

>>> Fanout - 扇出型封装

FOWLP:扇出晶圆级封装

FOPLP:扇出面板级封装

特点:RDL延伸到芯片外部

优势:无需基板、设计灵活

-

>>> Embedded Die - 嵌入式芯片封装

概念:芯片嵌入PCB或基板内部

优点:极短互连、良好屏蔽、节省空间

工艺:激光开槽、芯片埋入、层压

应用:高频模块、功率模块

-

>>> Heterogeneous Integration - 异构集成

定义:集成不同工艺、功能、材料的芯片

例子:Logic + Memory + RF + MEMS

驱动力:摩尔定律放缓、系统需求

技术:Chiplet、3D集成、SiP

-

>>> Chiplet - 小芯片

概念:将大芯片分解为多个小芯片

优势:提高良率、设计复用、混合工艺

互连:UCIe等标准化接口

趋势:未来主流架构之一

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?