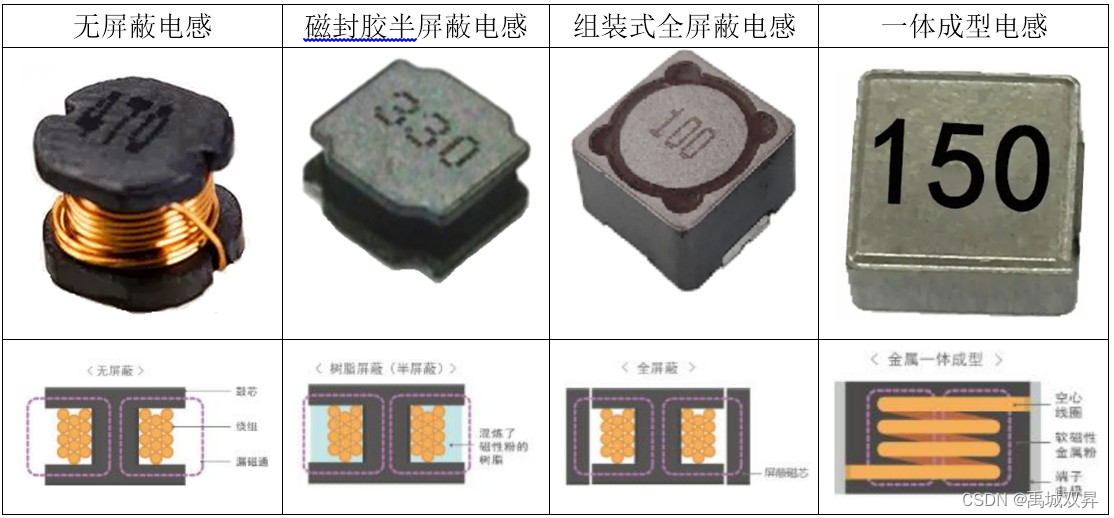

一.DC-DC电路常用功率电感类型

DC-DC电路中的电感下方该不该挖空?

在回答这个问题之前,先来了解一下DC-DC电路中常见的功率电感类型

这四种类型电感,按照无屏蔽电感→磁封胶半屏蔽电感→组装式全屏蔽电感→一体成型电感的顺序,磁屏蔽效果越来越好。

- 非屏蔽电感的磁力线完全暴露在空气中,漏磁比较大;

- 半屏蔽电感和全屏蔽电感相比非屏蔽电感,在电感外围加了一层磁屏蔽材料,由于导磁材料的磁阻小,磁力线基本被锁定在材料中,只有一小部分漏磁;

- 一体成型电感将绕组和磁性材料一次浇筑而成,只在内部留下一个很小的气隙以防止电感饱和,基本上没有磁力线溢出。

因此脱离电感类型来讨论电感下方该不该挖空并不恰当,而实际应用场合中对EMC和电感性能的要求也并不一致。因此要具体问题具体分析,根据预期目标来取舍。

二. 电感下方铺铜和挖空的利弊

1. 铺铜影响

1) 不利影响

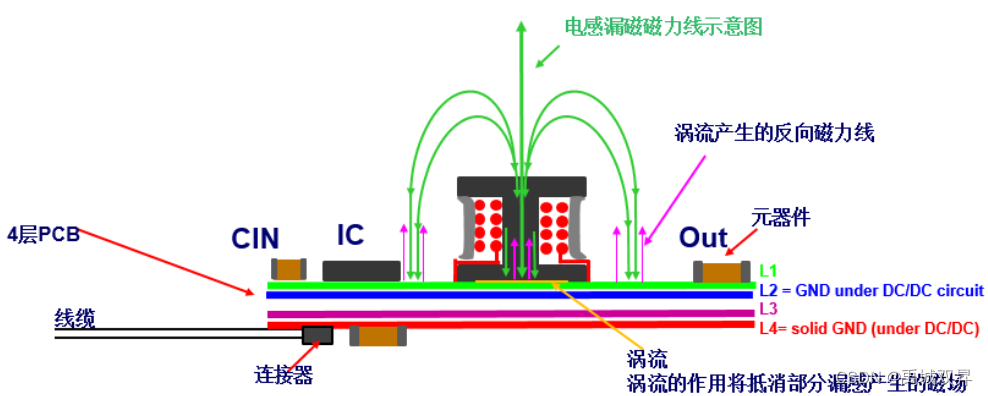

在电感底部铺铜,对于非屏蔽电感而言,存在大量漏磁,会作用在电感附近的铜皮上产生涡流损耗,进而造成以下不利影响,影响程度大致如下:

- 电感量减小(约8%);

- 效率下降(约0.5%)

- 电感电流峰值增大(约8%)

如果这种影响程度不会造成你的硬件电路设计指标失效的话,也完全不用考虑是否需要挖空。

2) 铺铜好处

在电感底部铺铜后,电感及其高频回路产生的磁场会与铺铜区产生涡流,涡流会使得原磁力线被削弱,阻断磁场向下传播,减小高频磁场对空间内其他电子器件的影响,有利于EMI的测试。

三. 如何抉择

了解了电感下方铺铜的利弊,再来做选择就比较容易了。

如果采用的是非屏蔽电感,其漏磁还是蛮大的,那么电感下方不挖空的影响还是比较大的;如果是磁封胶半屏蔽电感、组装式全屏蔽电感或者一体成型电感,其漏磁很小,尤其是一体成型电感,完全没必要考虑漏磁的影响。

如果采用的是非屏蔽电感,恰巧对电路的噪声要求又很高,那么电感下方挖空就势在必行;如果电路对EMC的要求高,对噪声要求不高的话,那么就得另做打算。对于多层线路板,可以考虑只挖离电感最近的一层,保留最远的一层铜皮,在EMC防护和降噪之间做个平衡。

四. 参考资料

1. DC/DC 电感下方到底要不要铺铜?_电感底下可以覆铜吗?-CSDN博客

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?