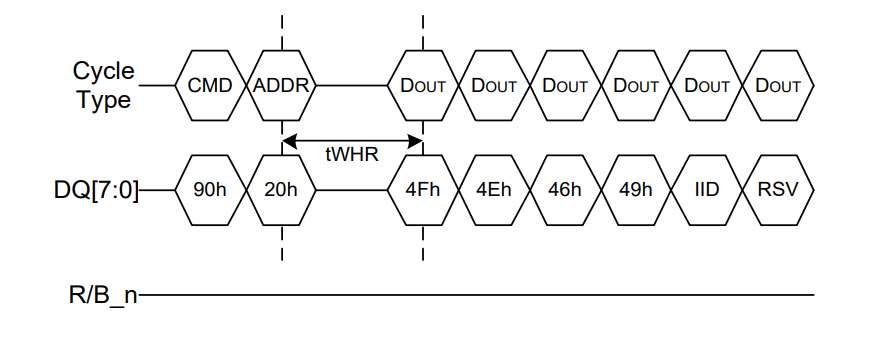

读取ID命令:

1、读取闪存签名:

ONFI(Open NAND Flash Interface):一种规范/标准

1、Cycle Type(操作周期)

- CMD(命令):第一个六边形表示命令周期,用于发送读取ONFI签名的命令。

- ADDR(地址):第二个六边形表示地址周期,用于发送特定的地址以触发签名读取操作。

- Dout(数据输出):后续的多个六边形表示数据输出周期,用于从NAND闪存中读取签名数据。

2、数据总线(DQ[7:0])

- 8位数据总线,用于传输命令、地址和数据。

- 命令周期:发送90h,这是读取ONFI签名的标准命令。

- 地址周期:发送20h,这是触发签名读取操作的特定地址。

- 数据输出周期:依次输出4Fh、4Eh、46h、49h、IID、RSV。

- 4Fh、4Eh、46h、49h是ONFI签名的ASCII码,对应字母“ONFI”。

3、“tWHR”,表示从写周期(如命令或地址写入)到读周期(数据输出)之间的时间间隔。

4、就绪/忙信号(R/B_n)

5、注释(Notes)

- IID(Interface ID):表示接口ID,对于NV-DDR3接口,其值为01h。

- RSV(Reserved):保留值,用于未来的扩展。

整个操作流程大致如下:

发送读取命令90h,发送读取地址20h,经过tWHR时间后,NAND闪存开始输出签名数据,依次为4Fh(O)、4Eh(N)、46h(F)、49h(I)、IID(接口ID)、RSV(保留值)。

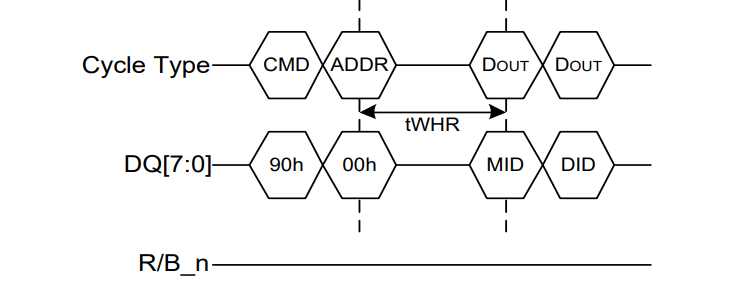

2、读制造商ID

下图是用于读取制造商ID的ID读取序列:

可以看到应该时序周期同样是包括了命令周期,地址周期、加上数据输出周期,用于从NAND闪存中读取制造商ID和其他相关信息。

数据总线(DQ[7:0]):

- 命令周期:发送90h,这是读取制造商ID的标准命令。

- 地址周期:发送00h,这是触发制造商ID读取操作的特定地址。

- 数据输出周期:依次输出MID(Manufacturer ID,制造商ID)、DID(Device ID,设备ID)。在MID和DID之前,图中还标注了90h和00h,但实际数据输出阶段是从MID开始的。

DID:设备ID,用于标识具体的设备型号或其他特性。

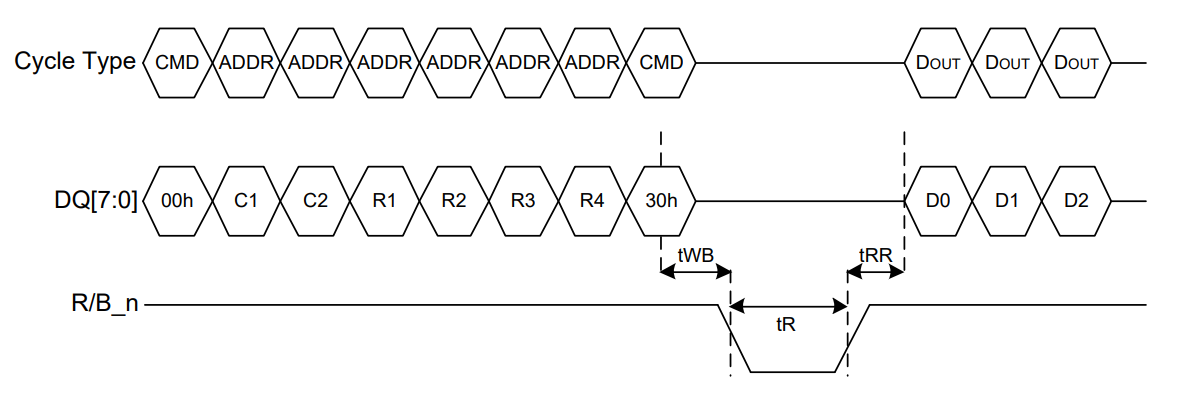

页面读取(Page Read)命令:

1、Cycle Type(操作周期)

CMD(命令):命令周期,用于发送读取页面命令。

ADDR(地址):地址周期,用于发送特定的地址以读取对应页面。

ADDR(地址):地址周期,用于发送特定的地址以读取对应页面。

CMD:在地址周期之后,再次发送一个命令(通常是确认命令)。

Dout(数据输出):数据输出周期,用于从NAND闪存的页面寄存器中读取数据。

Dout(数据输出):数据输出周期,用于从NAND闪存的页面寄存器中读取数据。

2、数据总线(DQ[7:0])

8位数据总线,用于传输命令、地址和数据。

命令周期:发送00h,表示开始页面读取操作。

地址周期:依次发送多个地址字节,例如C1、C2、R1、R2、R3、R4,用于指定页面的行地址。图中30h可能是最后一个地址字节或确认命令的一部分。

数据输出周期:输出页面数据,例如D0、D1、D2,表示从页面寄存器中读取的实际数据。

地址周期:依次发送多个地址字节,例如C1、C2、R1、R2、R3、R4,用于指定页面的行地址。图中30h可能是最后一个地址字节或确认命令的一部分。

数据输出周期:输出页面数据,例如D0、D1、D2,表示从页面寄存器中读取的实际数据。

3、“tWHR”,表示从写周期(如命令或地址写入)到读周期(数据输出)之间的时间间隔。

4、就绪/忙信号(R/B_n)

表示NAND闪存的就绪/忙信号。该信号为低电平时(忙状态),表示NAND闪存正在执行操作;为高电平时(就绪状态),表示NAND闪存可以接受新的命令。

- tWB(Write to Busy):从发送最后一个地址字节到R/B_n信号变为低电平的时间间隔,表示闪存开始忙于内部操作。

- tR(Busy to Ready):R/B_n信号从低电平变为高电平的时间间隔,表示闪存完成内部操作并进入就绪状态。

- tRR(Ready to Read):从R/B_n信号变为高电平到可以开始读取数据的时间间隔。

整个操作流程大致如下:

- 发送命令:主机发送页面读取命令

00h。 - 发送地址:主机依次发送多个地址字节(

C1、C2、R1、R2、R3、R4),指定要读取的页面。 - 确认命令:主机发送确认命令(图中

30h可能是确认命令的一部分)。 - 等待操作完成:闪存开始忙于内部操作(R/B_n变为低电平),经过

tWB时间后,闪存完成数据从闪存阵列到页面寄存器的传输。 - 检测就绪状态:主机通过检查R/B_n信号或发送读取状态命令来确认闪存是否完成操作(R/B_n变为高电平,经过

tR时间)。 - 读取数据:在闪存就绪后,主机可以开始从页面寄存器中读取数据(经过

tRR时间)。

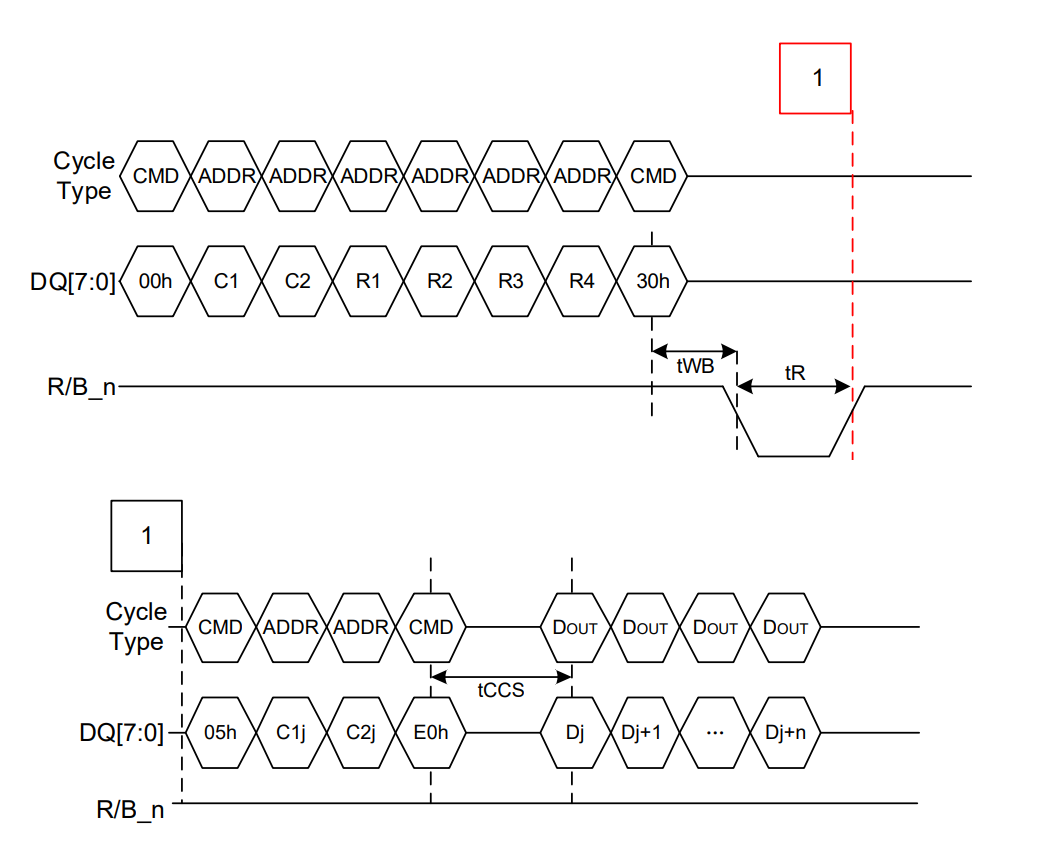

从NAND闪存中随机读取数据:

时序周期(Cycle Type)

- 命令周期:发送05h,这是“Change Read Column”命令,用于指定随机数据输出的起始列地址。

- 地址周期:依次发送C1j、C2j,这是具体的列地址字节,用于定义随机数据输出的起始位置。

- 确认命令:发送E0h,可能是与“Change Read Column”命令相关的确认或补充命令。

- 数据输出周期:输出随机数据,例如Dj、Dj+1、...、Dj+n,表示从页面中随机位置读取的数据。

操作流程总结

- 发送页面读取命令:主机发送

05h命令,启动随机数据读取操作。 - 发送地址:主机发送

C1j、C2j,指定随机数据输出的起始列地址。 - 发送确认命令:主机发送

E0h,确认随机数据读取操作。 - 等待数据准备:闪存内部准备随机数据(R/B_n信号可能变为低电平,图中未明确标注,但通常存在此过程)。

- 读取随机数据:经过

tCCS时间后,闪存开始从指定位置输出随机数据(Dj、Dj+1、...)。

写入:

页写入命令:

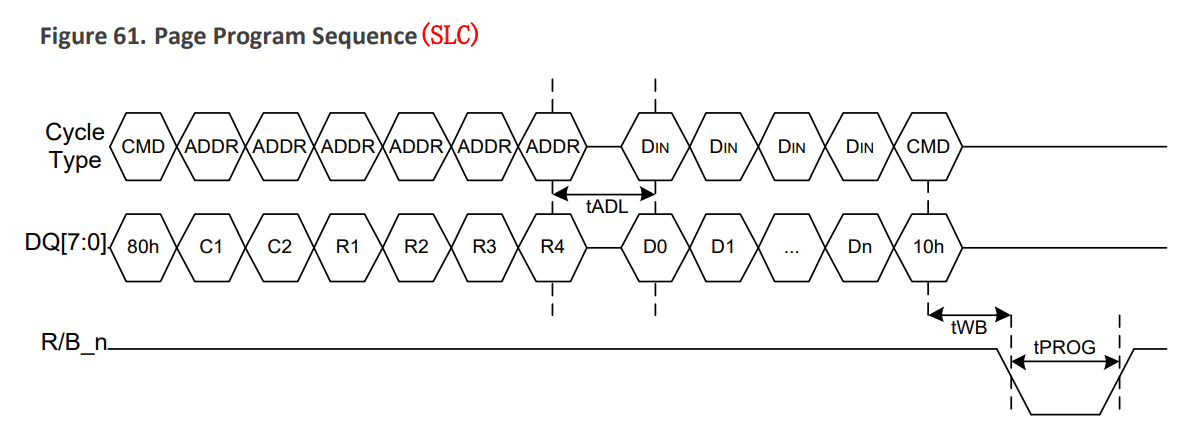

2.1 Cycle Type(周期类型)

这一行展示了在页编程过程中不同阶段的命令和操作类型,依次为:

- CMD:命令周期,用于发送操作命令。

- ADDR:地址周期,用于发送目标地址。

- DIN:数据输入周期,用于将数据加载到页寄存器中。

- 具体序列为:CMD -> ADDR -> ADDR -> ADDR -> ADDR -> ADDR -> ADDR -> DIN -> DIN -> ... -> CMD。

2.2 DQ[7:0](数据总线)

这一行展示了在数据总线DQ[7:0]上传输的具体数据和命令,依次为:

- 80h:页编程命令的开始,用于启动数据加载过程。

- C1, C2:列地址的低两位,用于指定数据在页内的起始列位置。

- R1, R2, R3, R4:行地址,用于指定目标页的地址。

- D0, D1, ..., Dn:要编程到闪存中的实际数据。

- 10h:确认命令,用于启动实际的编程操作。

2.3 R/B_n(就绪/忙信号)

这一行展示了闪存的就绪/忙信号(R/B_n)的状态变化:

- 在数据加载阶段(tADL),信号保持就绪状态。

- 当发出确认命令(10h)后,信号变为忙状态(低电平),表示编程操作正在进行。

- 编程操作完成后,信号恢复为就绪状态(高电平),持续时间分别为tWB(写忙时间)和tPROG(编程时间)。

3. 时间参数

图中标注了几个重要的时间参数:

- tADL:地址到数据加载时间,即从发送地址到开始加载数据的时间间隔。

- tWB:写忙时间,即从发出确认命令到闪存变为忙状态的时间。

- tPROG:编程时间,即实际完成编程操作所需的时间。

4. 操作流程总结

- 发送页编程命令(80h):启动页编程操作。

- 发送地址:包括列地址(C1, C2)和行地址(R1, R2, R3, R4),指定目标页和数据在页内的位置。

- 加载数据(D0, D1, ..., Dn):将数据加载到页寄存器中。

- 发送确认命令(10h):启动实际的编程操作,闪存进入忙状态。

- 等待编程完成:监控R/B_n信号,直到编程操作完成,闪存恢复为就绪状态。

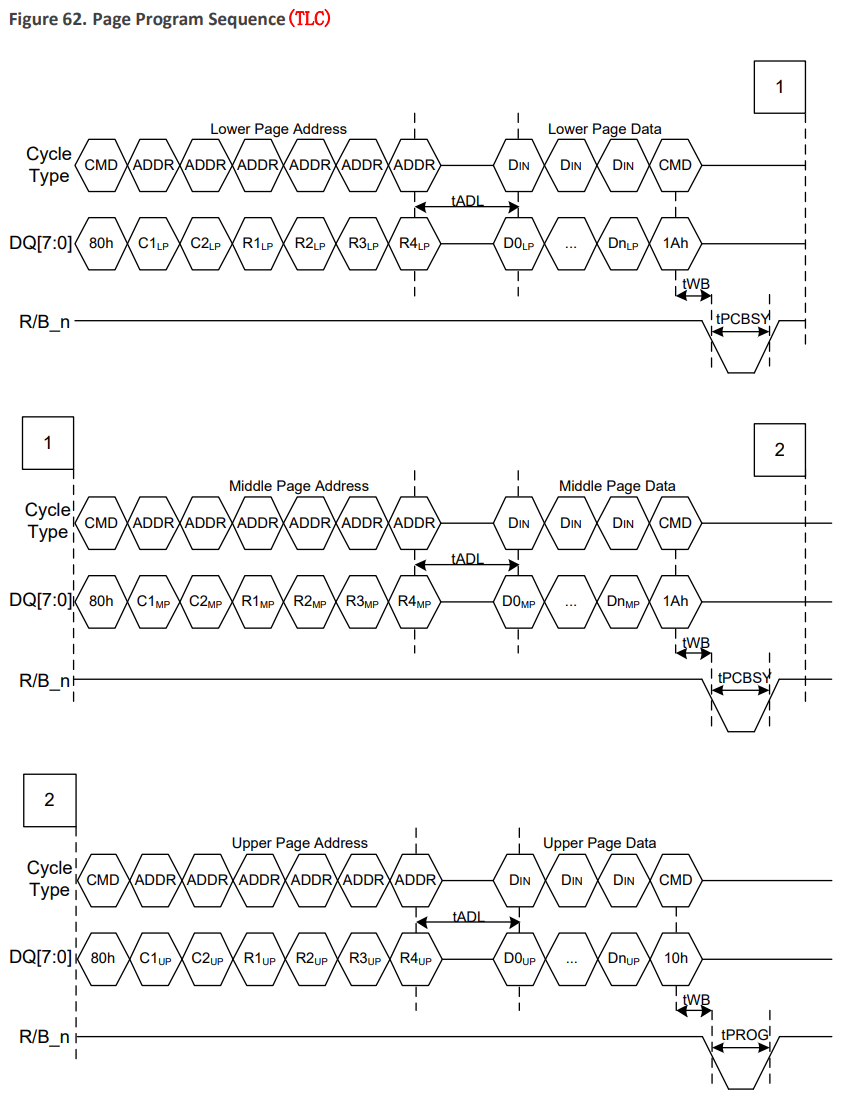

TLC同理,但是分成LP,MP,UP三页,连续擦除,三段之间时间为tPCBSY。

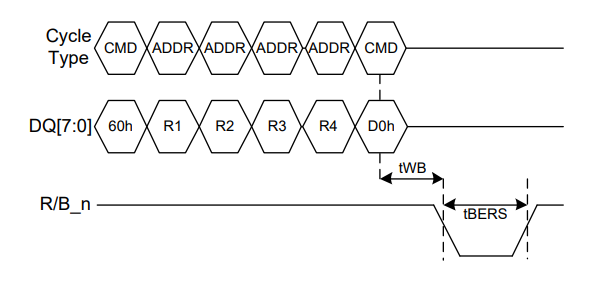

擦除:

1、单块擦除:

两个重要的时间参数:

- tWB:写忙时间,即从发出确认命令到闪存变为忙状态的时间。

- tBERS:块擦除时间,即实际完成块擦除操作所需的时间。

操作流程总结:

- 发送块擦除命令(60h):启动块擦除操作。

- 发送地址(R1, R2, R3, R4):指定要擦除的块地址。

- 发送确认命令(D0h):启动实际的擦除操作,闪存进入忙状态。

- 等待擦除完成:监控R/B_n信号,直到擦除操作完成,闪存恢复为就绪状态。

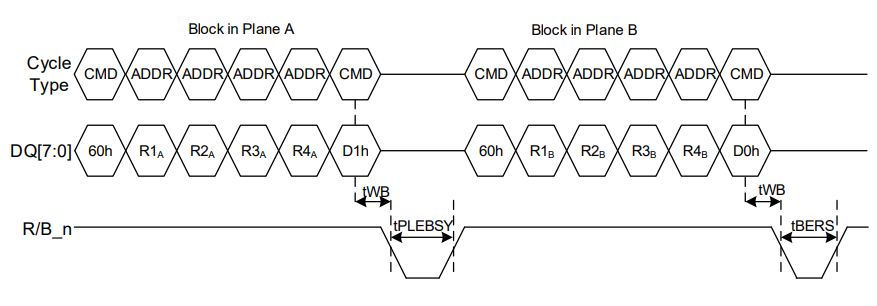

2、多块擦除:

- tPLEBSY:多平面擦除忙时间,即从开始多平面擦除操作到闪存忙状态结束的时间。

操作流程总结:

- 发送平面A的块擦除命令(60h):启动平面A的块擦除操作。

- 发送平面A的地址(R1_A, R2_A, R3_A, R4_A):指定平面A中要擦除的块地址。

- 发送平面A的确认命令(D1h):启动平面A的实际擦除操作。

- 发送平面B的块擦除命令(60h):启动平面B的块擦除操作。

- 发送平面B的地址(R1_B, R2_B, R3_B, R4_B):指定平面B中要擦除的块地址。

- 发送平面B的确认命令(D0h):启动平面B的实际擦除操作,此时两个平面的擦除操作同时进行,闪存进入忙状态。

- 等待擦除完成:监控R/B_n信号,直到擦除操作完成,闪存恢复为就绪状态。

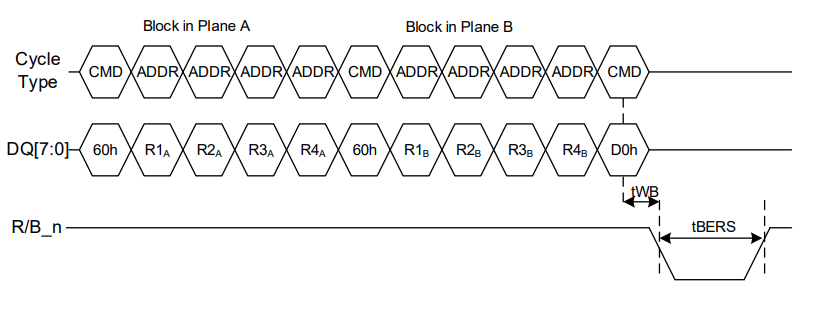

3、多平面块擦除:

同时擦除闪存中不同平面(Plane A和Plane B)的块。

两个重要的时间参数:

- tWB:写忙时间,即从发出确认命令到闪存变为忙状态的时间。这个时间间隔确保闪存有足够的时间进入忙状态并开始执行擦除操作。

- tBERS:块擦除时间,即实际完成块擦除操作所需的时间。在这个时间之后,闪存完成擦除操作并恢复到就绪状态。

操作流程总结:

- 发送平面A的块擦除命令(60h):启动平面A的块擦除操作。

- 发送平面A的地址(R1_A, R2_A, R3_A, R4_A):指定平面A中要擦除的块地址。

- 发送平面B的块擦除命令(60h):启动平面B的块擦除操作。

- 发送平面B的地址(R1_B, R2_B, R3_B, R4_B):指定平面B中要擦除的块地址。

- 发送确认命令(D0h):启动平面A和平面B的实际擦除操作,此时两个平面的擦除操作同时进行,闪存进入忙状态。

- 等待擦除完成:监控R/B_n信号,直到擦除操作完成,闪存恢复为就绪状态

1602

1602

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?