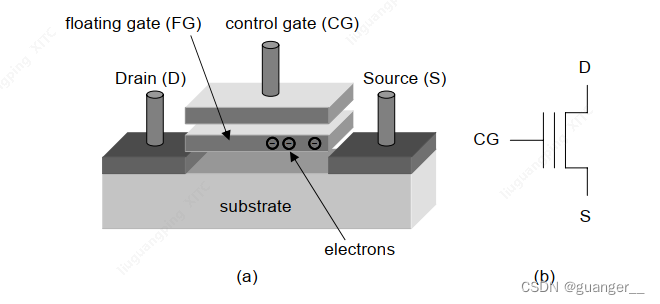

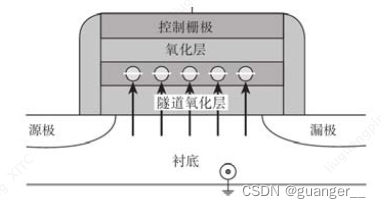

nand基本存储单元和结构

nand内部有大量MOS管,nand的基本存储单元是一种类NMOS的双层浮栅MOS管,如图一所示,其中包含控制极、源极、漏极、底衬和浮栅层(floating gate)。电子存储在floating gate中,floating gate上下的氧化层可以防止电子的溢出,所以断电时里面的电子不会消失,所以有“记忆”功能。

图1 浮栅晶体管结构

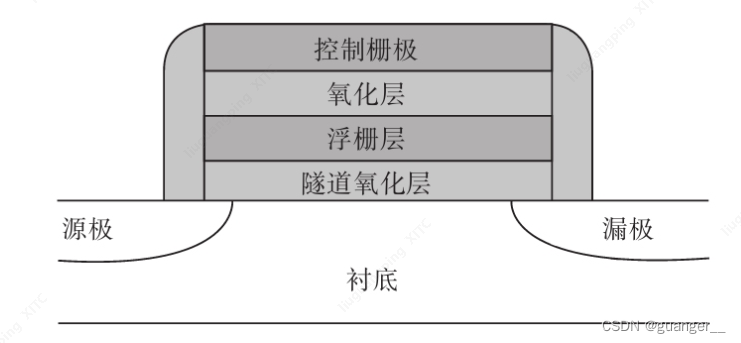

PN结

在一块完整的硅片上,用不同的掺杂工艺使其一边形成N型半导体,另一边形成P型半导体,我们称两种半导体的交界面附近的区域为PN结,如图2所示。PN结类似于单向导通的二极管,源极和漏极间有两个方向相反的PN结,所以当控制极不施加电压的情况下,内部不会导通。

图2: PN结

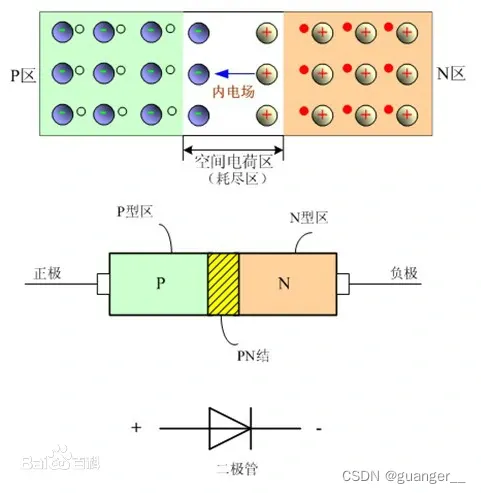

量子隧穿效应原理

量子力学中,由于粒子具有不确定性,即使粒子能量低于势垒能量,它也有一定概率出现在势垒之外。而粒子能量越大,出现在势垒之外的概率越高。具体原理请参考量子隧穿原理。

擦操作原理

如图3所示,擦操作是在底衬上施加高电压(+20V),经过足够长的时间,由于量子隧道效应,会把电子从floating gate中吸到沟道。擦操作执行的对象是整个block,同一lun的所有存储单元共用一个底衬,但不执行擦操作的block的控制极会浮空。执行完擦操作后,floating gate中无电子,都表现为‘1’,每个存储单元的VT(导通电压)为负值,即擦操作后控制极施加0V电压时会导通。

写操作原理

如图3所示,写操作是把底衬接地,把要写'0'的bitline施加0V,控制极施加高电压(+18 ~ +20V),由于量子隧道效应,使电子通过氧化层进入floating gate中,表现为‘0’,‘0’存储单元的VT(导通电压)值大于0V。不写的bitline(需写'1'的存储单元不用写,擦除后就已经是‘1’了,不用再写了)施加3V,此时源极和漏极导通,阻碍了量子隧道效应的发生。

图3: 左:擦原理 右:写原理

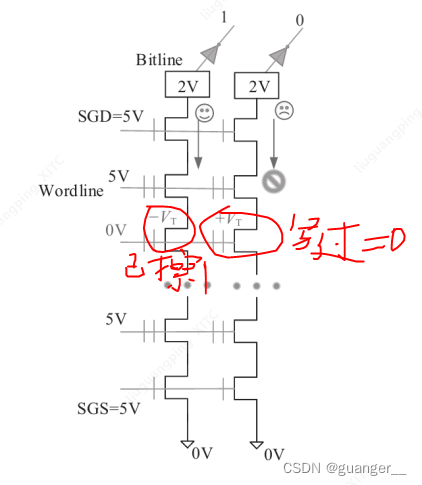

读操作原理

如图4所示,不读的WL施加VreadPass电压(+5V),VreadPass电压大于Vt值,可以这个让WL上的存储单元都导通。要读的存储单元在WL(控制极)施加0V电压,阈值电压为负(状态‘1’)的存储单元可以导通,传感器读出值为‘1’;阈值电压为正(状态‘0’)的存储单元不会导通,传感器读出值为‘0’。

图4: 读原理图

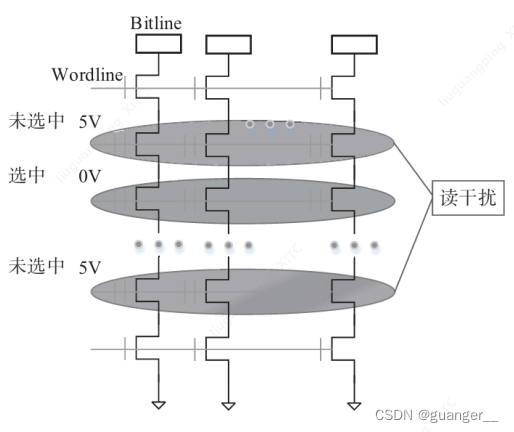

read disturb原理

当读一个page时,未被选择的page会在其WL上施加VreadPass电压,以保证未被选中的MOS管导通。这样频繁的往一个MOS管的WL上施加VreadPass电压,就会导致有电子被吸入floating gate,形成轻微的写,最终导致比特翻转,如图5所示。读干扰带来的影响不是永久性的,重新擦除后可以正常使用。读干扰影响的是同一闪存块的其他page,读取页自身不受影响。

图5: 读干扰原理图

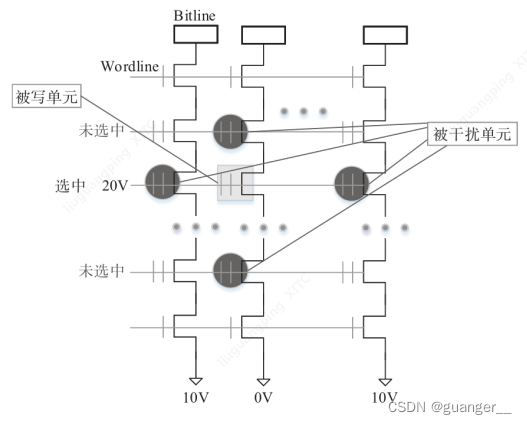

write disturb原理

由于擦除后的存储单元是‘1’,只有写‘0’的时候才会真正的去写。如图6所示,方框中的存储单元要写‘0’,即需要写的,方框存储单元左右两个存储单元写‘1’,即不需要写的。在写操作的过程中,被选中的WL会被施加高电压(+20V),未被选择的WL会被施加Vppass电压,需要编程的bitline会被施加0V电压,不用编程的bitline会被施加(+8V ~ +10v)电压来抑制编程。

写干扰主要分为program disturb和pass disturb两钟情况。program disturb是影响选中WL上写‘1’(不用真实写)的存储单元,WL会被施加高电压(+20V),虽然这些存储单元的bitline会被施加(+8V ~ +10v)电压,但不可避免的还是有电子进入floating gate,形成轻微的写。pass disturb是影响未被选中的WL上bitline为0V的存储单元,WL被施加Vppass电压,bitline为0V,会形成轻微的写。写干扰影响的不仅是闪存块未被选择的闪存页,自身闪存页写‘1’的存储单元也会受影响。

图6: 写干扰图

data retention原理

存储在floating gate中的电荷,如果长期不使用,会发生电荷泄露。这样会导致‘1’变成‘0’的现象,形成轻微的擦。这是非永久性损伤,擦除后闪存块可以继续使用。

闪存寿命

随着闪存块擦写次数的增加,晶体管氧化层会变薄或者老化,电子会更容易通过氧化层进出浮栅,同时电子也会吸附在氧化层上,使电子真正存储在floating gate里的数量不是预期的。每个闪存块的擦写次数都有一个阈值,达到阈值使闪存块将达到生命末期,甚至变成数据不可靠的坏块。我们在做SSD时需要使用磨损均衡策略(wear leveling),目标是时SSD中所有闪存块的磨损均衡分布,最终让所有闪存块一起达到生命末期。

2082

2082

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?