术语:

• AHB: advanced high-performance bus.

• APB: advanced peripheral bus.

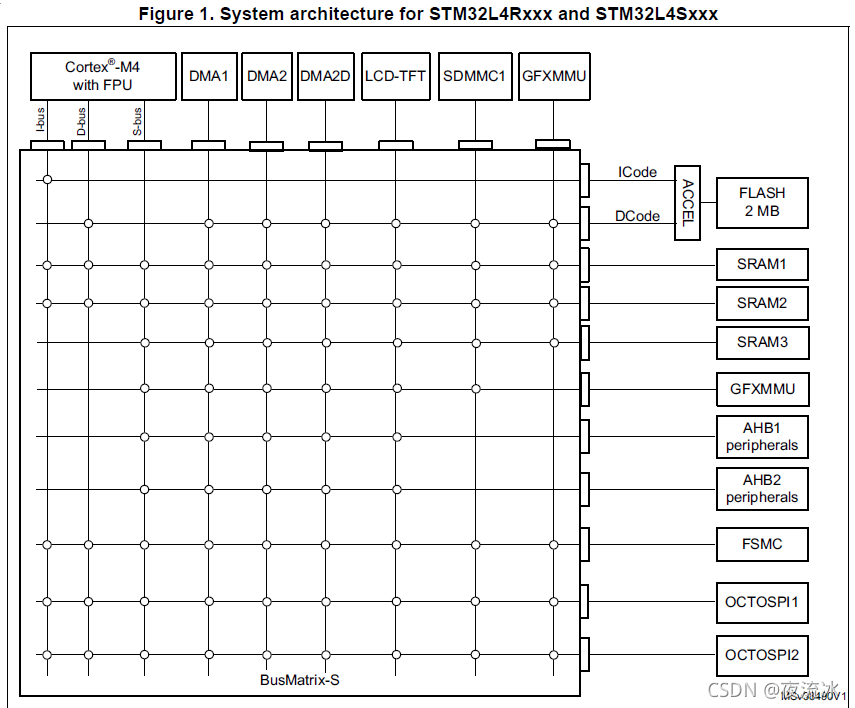

STM32L4芯片主系统包含了32位的多层AHB互联的总线矩阵模型。

包含多达9个总线主控制器:

– Cortex® -M4 with FPU core I-bus

– Cortex® -M4 with FPU core D-bus

– Cortex® -M4 with FPU core S-bus

– DMA1

– DMA2

– DMA2D (Chrom-Art Accelerator™) memory bus

– LCD-TFT controller DMA-bus

– SDMMC1 bus

– GFXMMU (Chrom-GRC™) bus (only for STM32L4Sxxx and STM32L4R5xxx devices)

多达11个从设备:

– Internal Flash memory on the I-Code bus

– Internal Flash memory on D-Code bus

– Internal SRAM1

(192 Kbytes for STM32L4Rxxx and STM32Sxxx devices and

128 Kbytes for STM32L4P5xx and STM32Q5xx devices)

– Internal SRAM2 (64 Kbytes)

– Internal SRAM3

(384 Kbytes for STM32L4Rxxx and STM32L4Sxxx devices and

128 Kbytes for STM32L4P5xx and STM32L4Q5xx devices)

– GFXMMU (Chrom-GRC™)

(only for STM32L4Rxxx and STM32L4Sxxx devices)

– AHB1 peripherals including AHB to APB bridges and APB peripherals (connected

to APB1 and APB2)

– AHB2 peripherals

– Flexible memory controller (FMC)

– OCTOSPI1

– OCTOSPI2

总线矩阵提供了从主控制器到从设备的访问,即使在几个高速外设同时工作的情况下,也能实现并发访问和高效运行。架构图如下所示:

BusMatrix负责管理主控制器之间的访问仲裁。该仲裁使用Round Robin算法。

AHB/APB桥:

两个AHB/APB桥接器在AHB和两个APB总线之间提供完全同步的连接,并允许灵活选择外设频率。

在内存映射图上,可以查看连接到这个桥接器的外设的寄存器的地址。

每当外设复位后,所有的外设时钟都被禁用(除了SRAM1/2和闪存接口除外)。在使用一个外设之前,你必须先设置RCC_AHBxENR和RCC_APBxENR寄存器来启用其时钟。

注意:当对APB寄存器进行16位或8位访问时,访问会被转化为32位的访问:桥接器会复制16位或8位的数据以提供32位的向量。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?