目录

1 light sleep的时间补偿

IDF使用芯片的sys timer外设来计时,作为上层时间管理功能的基础。但在sleep期间,sys timer的计数会停止:

- C6以前,sys timer的时钟会被gate

- C6及以后的芯片,sys timer外设是可以配置掉电的

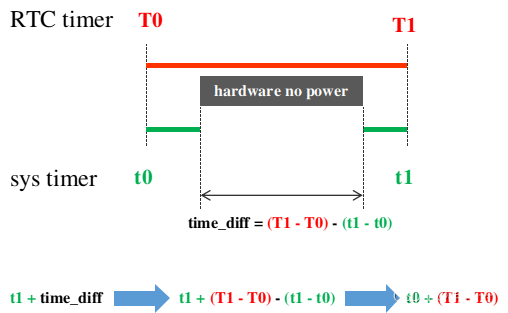

如果不做任何处理,就会导致sleep期间的时间会丢掉。对此,IDF使用RTC timer来补偿sys timer,补偿逻辑很简单:

2 light sleep前的时钟校准

由前文可知,RTC模块的时钟来源有多种,比如32K晶振、内部RC振荡器等。不同种类的时钟其精确度是不一样的,比如晶振就认为是比较准的,而内部振荡器的输出可能会随时间产生一定的漂移。因此如果使用内部RC振荡器来为RTC模块提供时钟,那么最好在sleep之前做一次时钟的校准,以确保预设的睡眠时间的准确性。时钟校准的原理很好理解:

- 待校准时钟运行时间T

- 40M主晶振运行同样的时间T

认为40M主晶振是准确的40M,那么就可以根据在时间T内,40M主晶振的cycle数及待校准时钟的cycle数算出待校准时钟的准确频率。

3 为什么Flash下电比较特殊

Flash下电存在一定的风险,这一点在官方的

订阅专栏 解锁全文

订阅专栏 解锁全文

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?