提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

前言

前面我们已经对静态时序分析的一些概念做了介绍,接下来我们以实际的时序报表来解读,vivado工具是如何进行时序分析的。

时序报表

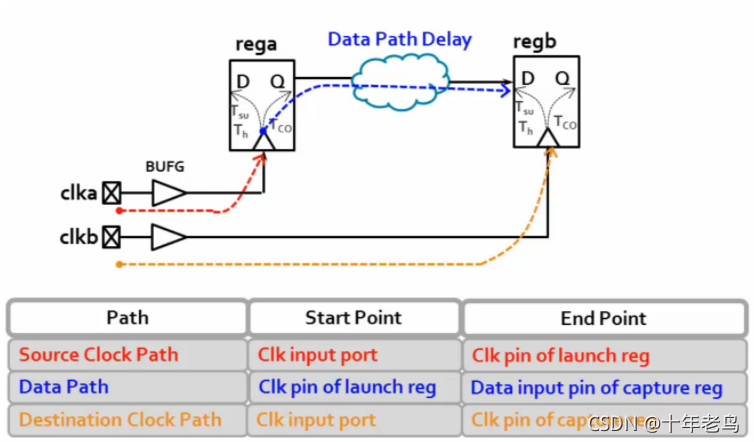

我们把静态时序分析(二)中的时序路径模型图贴到这里用于参考

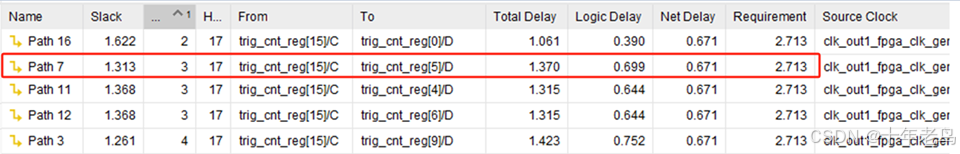

时序报表中,我们主要关注的是一个时钟域内的所有时钟路径是否还有余量,因此绝大部分路径都可以套用单周期时序分析模型,下面我们就摘取一条具体的路径进行解析。

首先我们打开时序报表,来看看Path 7这条路径的时序信息,这是一条建立时间的时序分析,如图所示

- 摘要

双击Path 7这条路径,会弹出时序路径的细节。首先,我们看摘要部分,如下图所示。

本文详细解读了Vivado工具中的时序报表,通过实例分析Path 65的时序信息,包括summary表、Source Clock Path、Data Path和Destination Clock Path,阐述了时序路径模型、时钟偏斜、时钟不确定性等关键概念,帮助理解FPGA静态时序分析。

本文详细解读了Vivado工具中的时序报表,通过实例分析Path 65的时序信息,包括summary表、Source Clock Path、Data Path和Destination Clock Path,阐述了时序路径模型、时钟偏斜、时钟不确定性等关键概念,帮助理解FPGA静态时序分析。

订阅专栏 解锁全文

订阅专栏 解锁全文

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?