基于FMC150的驱动代码(Verilog语言)

DDS代码设计

ID:68349637794109426

UncleJack

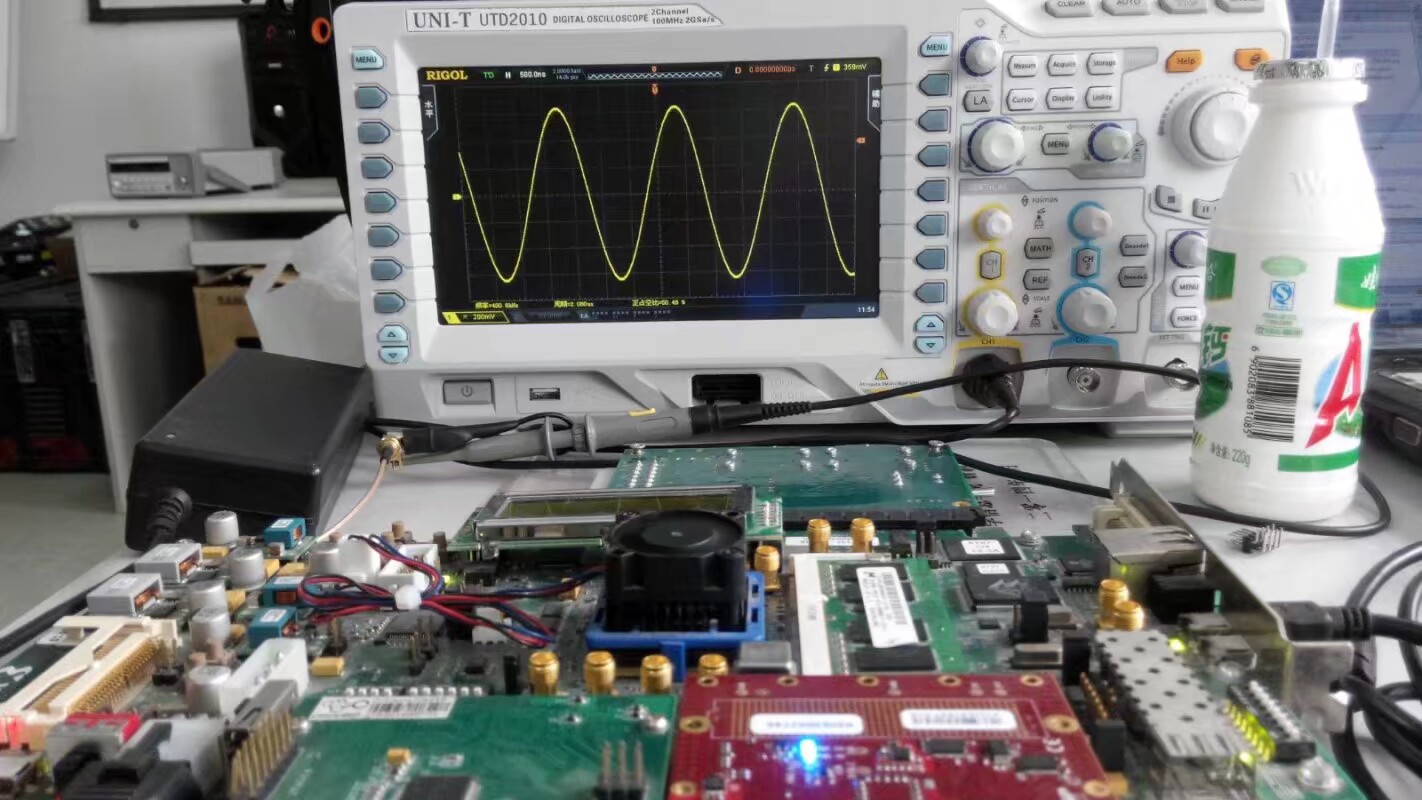

本文将针对基于FMC150的驱动代码(Verilog语言)中的DDS代码设计进行详细分析和探讨。DDS(Direct Digital Synthesis,直接数字合成)是一种常用于数字信号处理的技术,可以通过数字代码直接生成模拟信号,在通信、雷达、测量和仪器等领域具有广泛的应用。

DDS的核心思想是使用相位累加器和查表技术,通过对相位累加器的控制,按照预设的频率和相位差,从查表中读取相应的数值并输出,从而实现模拟信号的生成。而在FMC150驱动代码中的DDS代码设计,就是为了充分发挥FMC150这一高性能模块的功能,实现对DDS技术的灵活应用。

首先,我们需要了解FMC150是一款功能强大的FPGA Mezzanine Card,它提供了高速数据转换和数字信号处理的能力,可以与FPGA开发板进行连接并实现高性能的信号处理。在FMC150的驱动代码中,DDS代码设计起到了关键的作用,它可以通过FPGA实现对输入数据的处理和生成模拟输出信号。

在DDS代码设计中,我们需要考虑以下几个关键点:

-

相位累加器设计:相位累加器作为DDS的核心组成部分,用于实现频率和相位的控制。在设计相位累加器时,我们需要考虑其分辨率、相位精度,以及相位差的计算和累加方法等。通过合理的相位累加器设计,可以实现对模拟信号的高精度生成。

-

查表技术应用:DDS的查表技术是实现信号生成的关键,通过事先存储和查表,可以在需要的时候直接读取相应的数值并输出。在DDS代码设计中,我们需要考虑查表的大小、数据的存储方式,以及查表的访问方式等。通过合理的查表技术应用,可以大大提高DDS的计算效率和输出信号的质量。

-

频率和相位控制:DDS的一个重要功能是可以实现对输出信号的频率和相位的精确控制。在DDS代码设计中,我们需要考虑如何设计接口和参数,以便用户可以灵活地设置输出信号的频率和相位。通过合理的频率和相位控制设计,可以满足不同应用场景下对信号的要求。

-

系统性能和资源占用:DDS代码设计需要充分考虑系统的性能和资源占用情况。在FMC150驱动代码中,FPGA的资源是有限的,因此需要根据实际需求进行设计和优化,以实现高性能和高效的信号处理。同时,还需要考虑系统的稳定性和可靠性,确保DDS代码在各种复杂环境下正常运行。

综上所述,基于FMC150的驱动代码中的DDS代码设计是实现数字信号处理的重要一环。通过合理的相位累加器设计、查表技术应用、频率和相位控制,以及对系统性能和资源占用的优化,可以实现高性能和高效的信号处理。DDS技术的应用为通信、雷达、测量和仪器等领域带来了便利和创新,相信在FMC150驱动代码中的DDS代码设计的指导下,将能够更好地发挥FMC150的功能,实现更广泛的应用。

相关的代码,程序地址如下:http://imgcs.cn/637794109426.html

79

79

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?