创作时间:2021-08-18

1.一些说明:

generate循环的语法与for循环语句的语法很相似。

genvar只有在建模的时候才会出现,在仿真时就已经消失了。

但是在使用时必须先在genvar声明中声明循环中使用的索引变量名,然后才能使用它。

genvar声明的索引变量被用作整数用来判断generate循环。

genvar声明可以是generate结构的内部或外部区域,并且相同的循环索引变量可以在多个generate循环中,只要这些环不嵌套。

2.举个例子,一看就明了

1)代码

design file

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2021/08/17 17:46:44

// Design Name:

// Module Name: ex_generate

module ex_generate#(

parameter DW=16

)

(

iv_data ,

ov_data_channel_0 ,

ov_data_channel_1 ,

ov_data_channel_2 ,

ov_data_channel_3 ,

ov_data_channel_4 ,

ov_data_channel_5 ,

ov_data_channel_6 ,

ov_data_channel_7

);

input wire[DW-1:0]iv_data ;

output wire[ 1:0]ov_data_channel_0;

output wire[ 1:0]ov_data_channel_1;

output wire[ 1:0]ov_data_channel_2;

output wire[ 1:0]ov_data_channel_3;

output wire[ 1:0]ov_data_channel_4;

output wire[ 1:0]ov_data_channel_5;

output wire[ 1:0]ov_data_channel_6;

output wire[ 1:0]ov_data_channel_7;

wire[1:0] temp [7:0]; //注意[1:0]和[7:0]的顺序

genvar ii;

generate

for(ii=0;ii<=7;ii=ii+1)

begin: ex_gen//begin 后边这个命名一定要加

assign temp[ii]=iv_data[2*ii+1:2*ii];

end

endgenerate

assign ov_data_channel_0=temp[0];

assign ov_data_channel_1=temp[1];

assign ov_data_channel_2=temp[2];

assign ov_data_channel_3=temp[3];

assign ov_data_channel_4=temp[4];

assign ov_data_channel_5=temp[5];

assign ov_data_channel_6=temp[6];

assign ov_data_channel_7=temp[7];

endmodule

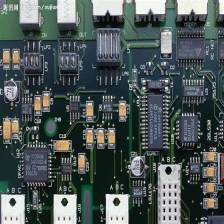

- RTL 电路

3)综合电路

4)仿真波形

testbench

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2021/08/18 10:32:32

// Design Name:

// Module Name: tb_ex_generate

module tb_ex_generate( );

parameter DW=16;

reg [DW-1:0]iv_data ;

wire [ 1:0]ov_data_channel_0;

wire [ 1:0]ov_data_channel_1;

wire [ 1:0]ov_data_channel_2;

wire [ 1:0]ov_data_channel_3;

wire [ 1:0]ov_data_channel_4;

wire [ 1:0]ov_data_channel_5;

wire [ 1:0]ov_data_channel_6;

wire [ 1:0]ov_data_channel_7;

initial begin

iv_data=16'b1100_0000_0000_0000;//(0)

#10;

iv_data=16'b0011_0000_0000_0000;//(1)

#10;

iv_data=16'b0000_1100_0000_0000;//(2)

#10;

iv_data=16'b0000_0011_0000_0000;//(3)

#10;

iv_data=16'b0000_0000_1100_0000;//(4)

#10;

iv_data=16'b0000_0000_0011_0000;//(5)

#10;

iv_data=16'b0000_0000_0000_1100;//(6)

#10;

iv_data=16'b0000_0000_0000_0011;//(7)

end

ex_generate #(

.DW(DW)

)

u_ex_generate(

.iv_data(iv_data),

.ov_data_channel_0(ov_data_channel_0),

.ov_data_channel_1(ov_data_channel_1),

.ov_data_channel_2(ov_data_channel_2),

.ov_data_channel_3(ov_data_channel_3),

.ov_data_channel_4(ov_data_channel_4),

.ov_data_channel_5(ov_data_channel_5),

.ov_data_channel_6(ov_data_channel_6),

.ov_data_channel_7(ov_data_channel_7)

) ;

endmodule

ok ,目标完成。

最后再说明下:

for(ii=0;ii<=7;ii=ii+1)//for 后边必须有begin end,哪怕是一句话

begin: ex_gen//begin 后边这个命名一定要加,我是随便加了个名字

assign temp[ii]=iv_data[2ii+1:2ii];

end

THE END~

【MATLAB-app】系列教程(含视频)00_csdn上第一套关于matlab appdesigner系列“视频课”来啦~~

4654

4654

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?