本文章以【凡亿】Cadence Allegro 17.4零基础入门66讲PCB Layout设计实战视频为基础

(一)创建文件

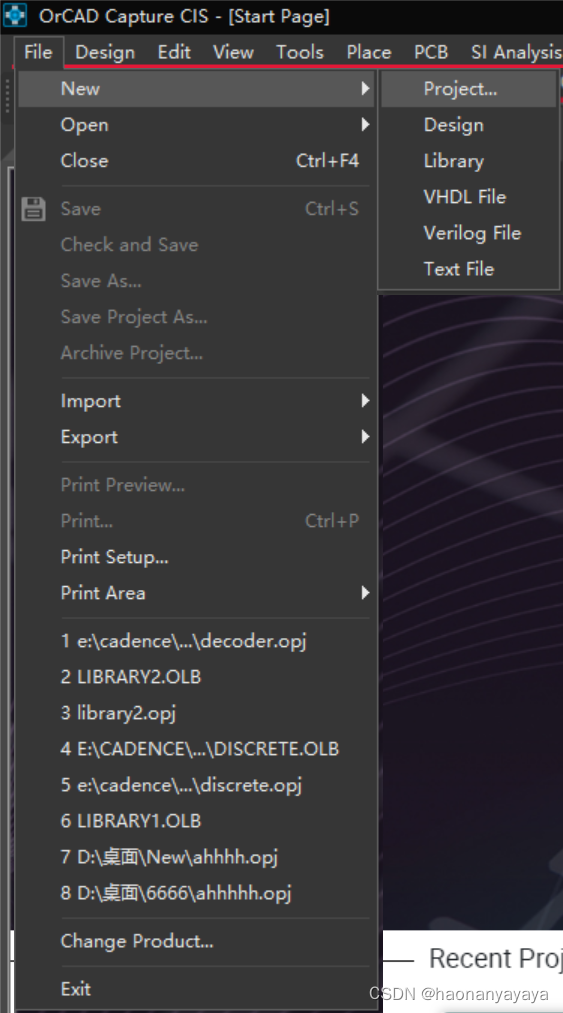

1,新建工程

(1)创建文件

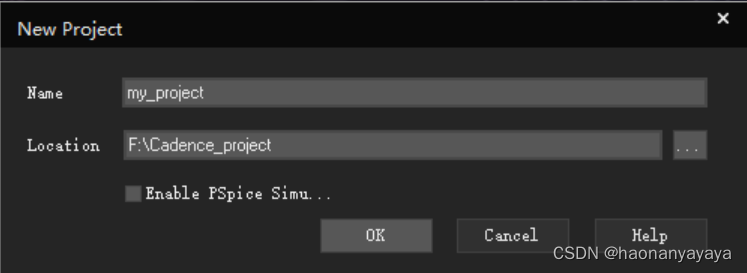

(2)输入名字与想放入的地址

注:不要放在带中文的路径中

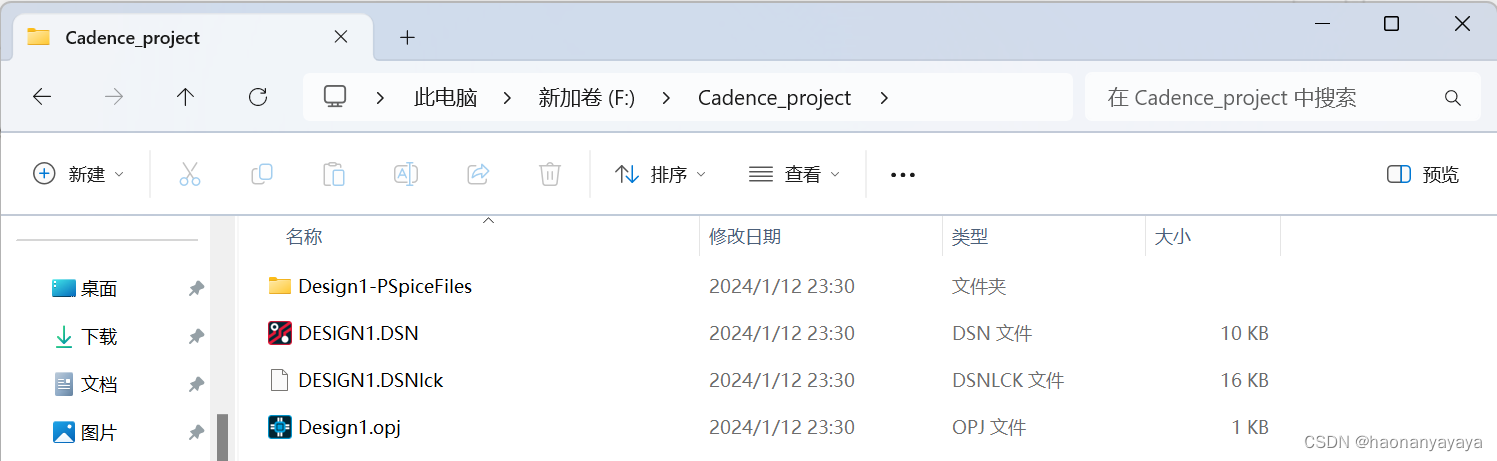

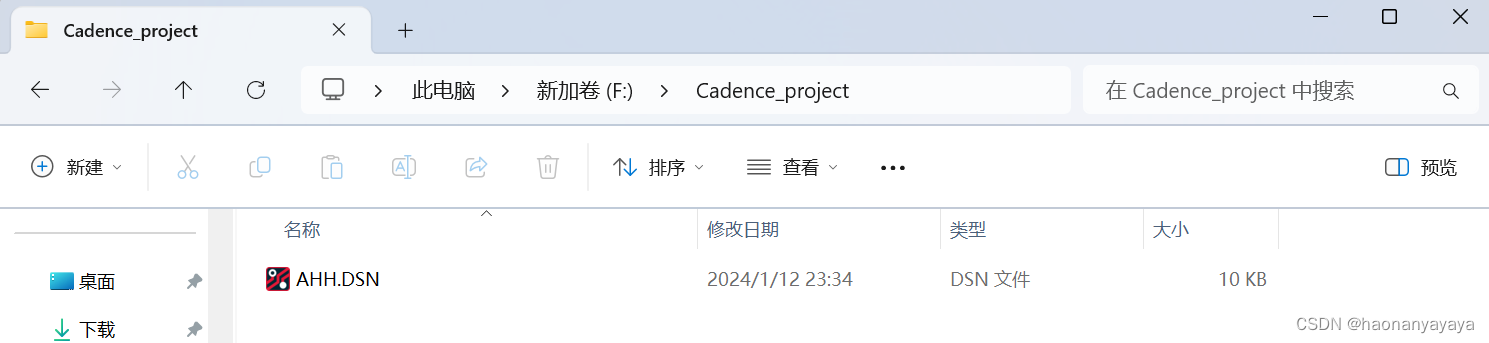

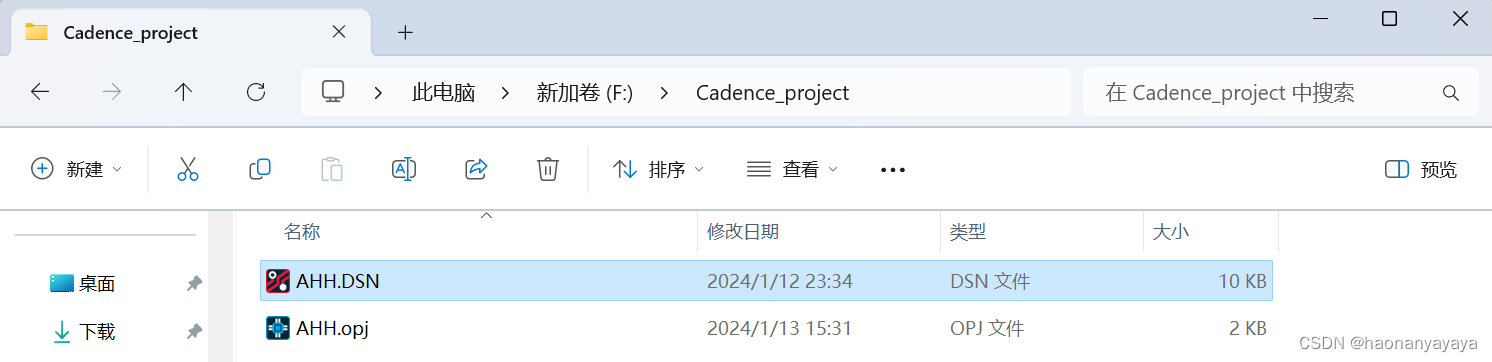

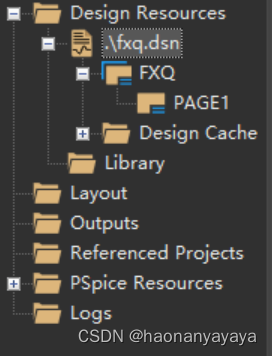

点击OK后打开这个文件夹,可以看见这几个文件,这个DSN就是原理图文件

(我们创建的是OPJ,DSN文件是自动生成)

注意:

工程原理图工具使用Capture CIS

PCB工具使用PBC Editor

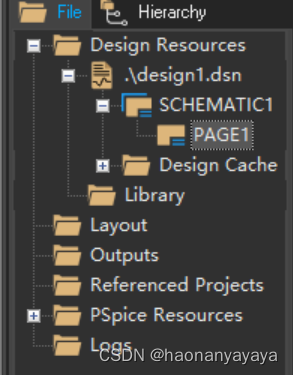

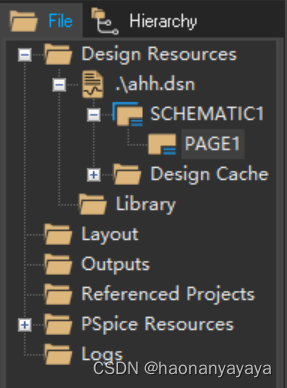

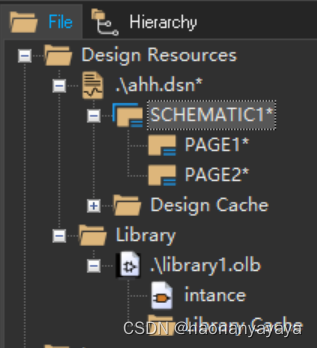

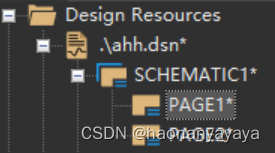

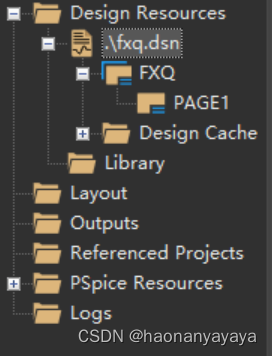

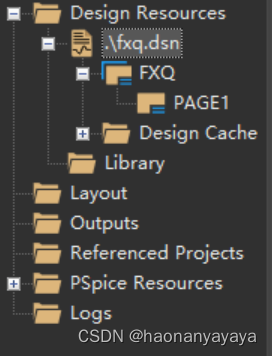

打开后可以看见下面几个文件

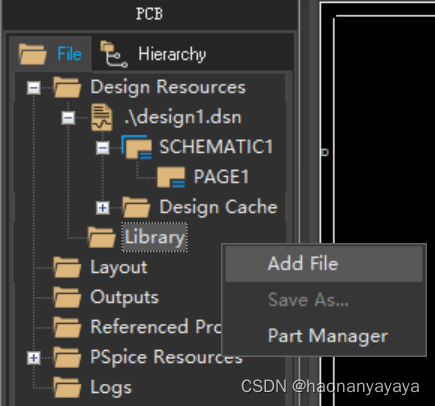

(3)右键Library,点击Add File

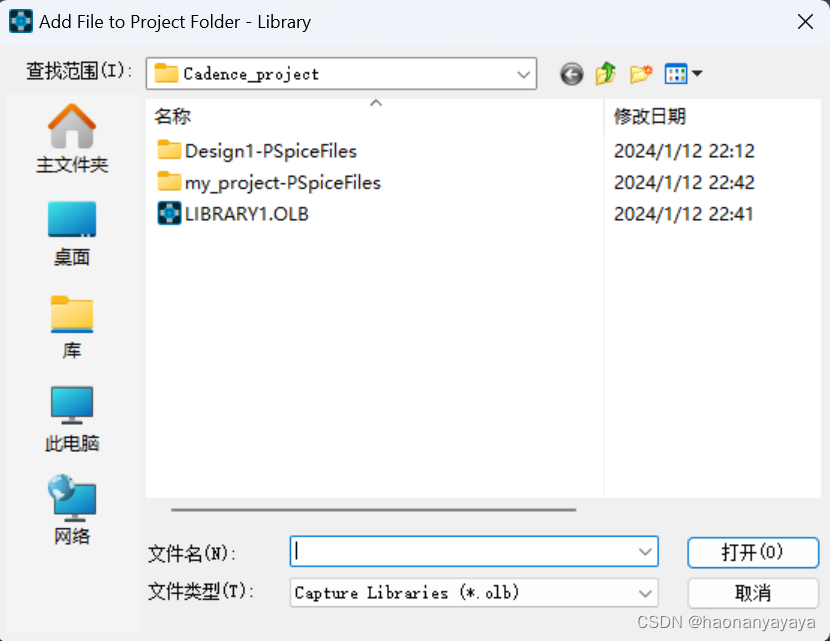

(4)找到自己要使用的库添加进去

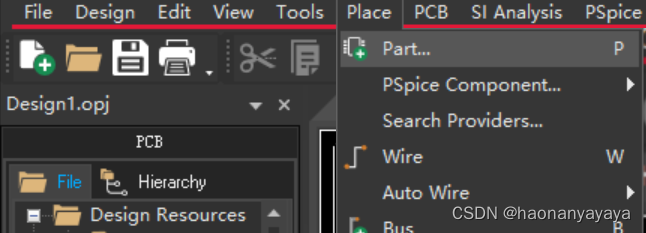

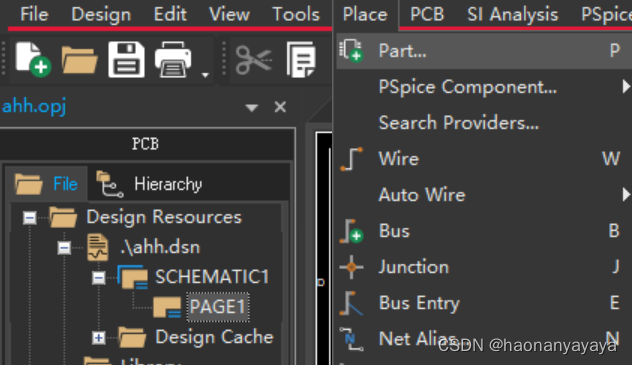

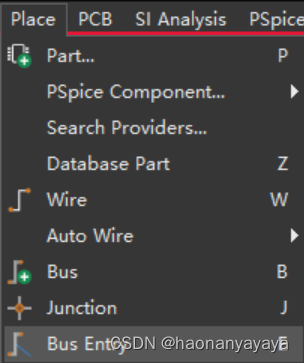

(5)点击Place,再点Part

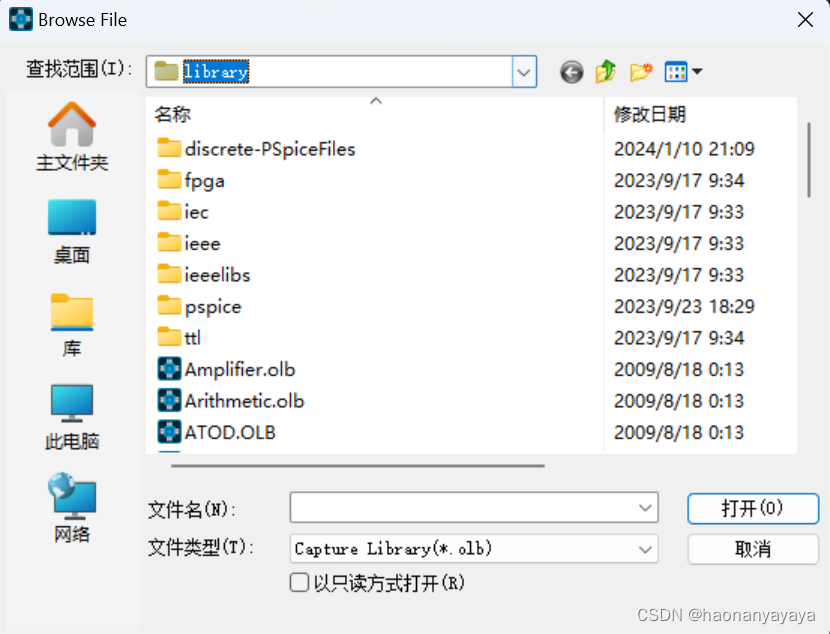

(6)打开需要的库文件

这个时候就可以看见自己添加进的文件,双击Part名称,就可以放置了

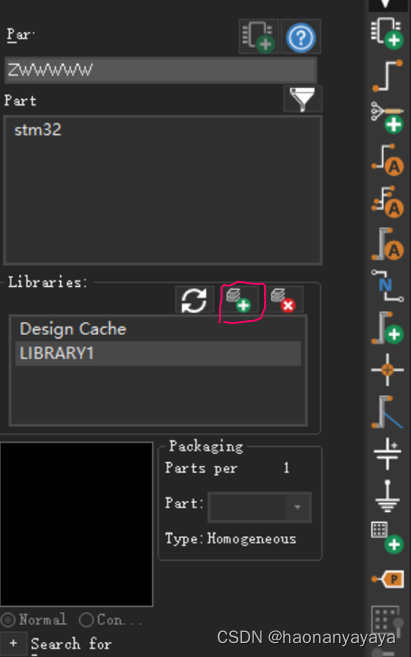

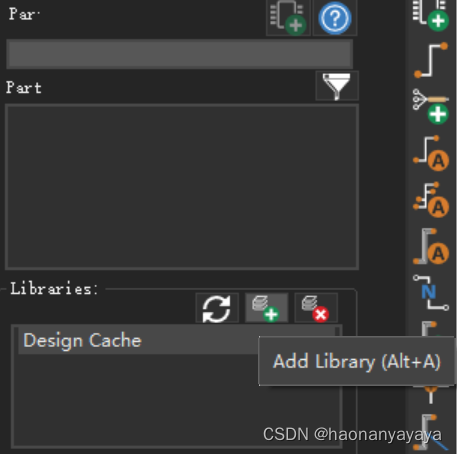

方法二:点击这个也可以添加库文件

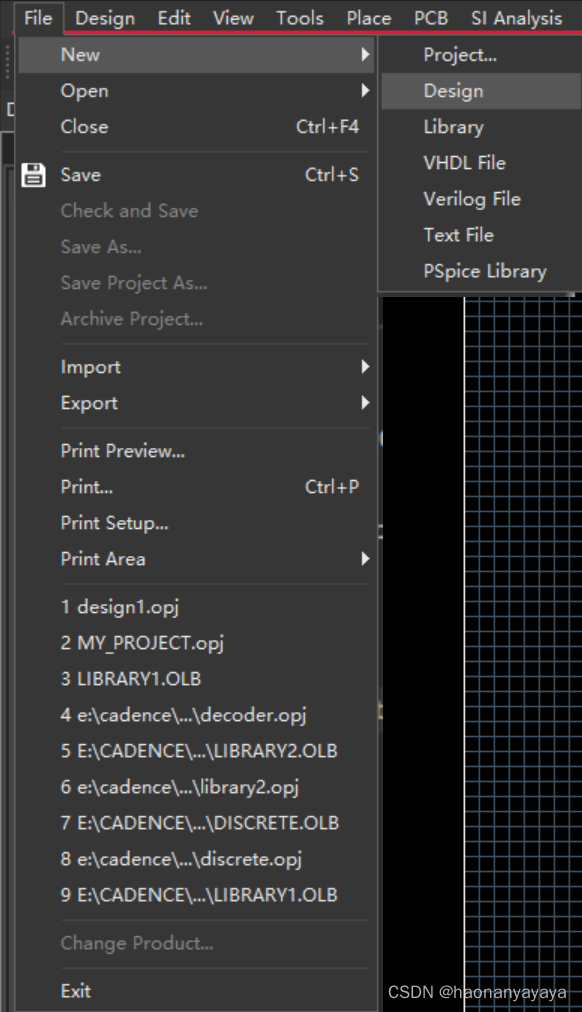

2,新建设计图

A,有工程的情况下创建设计图

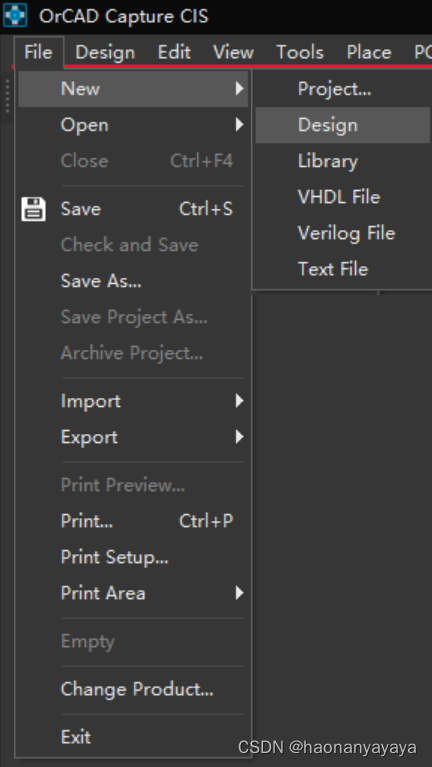

点击File,New,Design

这里不用选路径是因为之前创建了工程,默认把设计图和工程放在一起

改名:

(1)关闭Capture

(2)打开工程的路径,对DSN文件改名

B,在没有工程的情况下创建设计图

(1)点击File,New,Design

(2)选择要放入的文件夹

(3)你会惊奇的发现这和创建工程的东西是一样的

事实上,在打开设计图的时候,系统会生成一个opj文件

在给别人发送设计图的时候只用发送DSN文件就行

注:只发送opj文件别人打不开

C,接受原理图

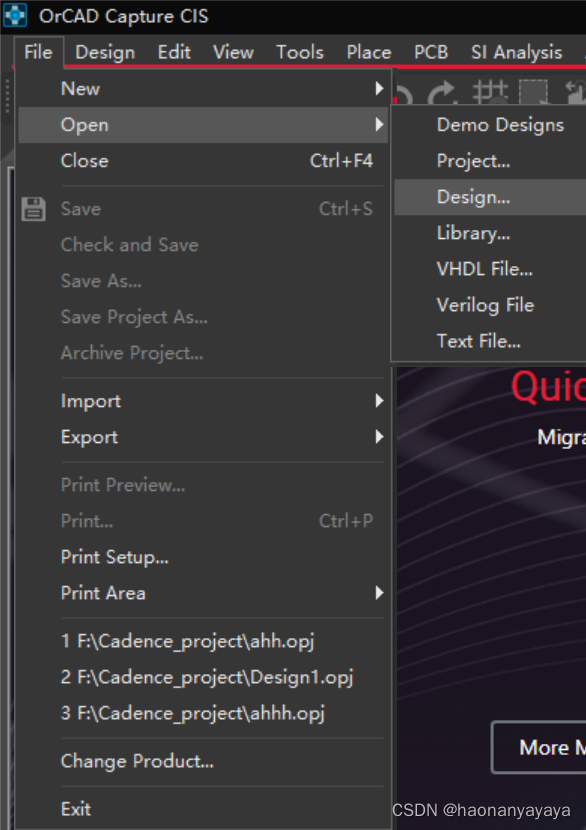

(1)点击File,Open,Design

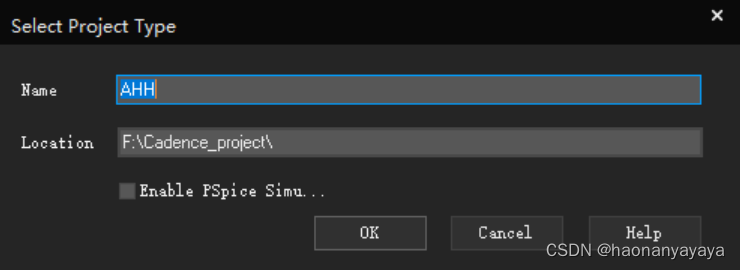

(2)输入名称与想放入的位置

(3)打开PAGE1就可以看见了

(二)修改原理图相关

1,修改原理图名称

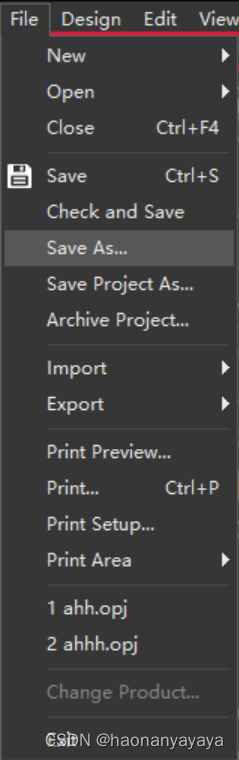

方法一:另存一个文件,将原理图名称修改

方法二:打开文件地址,修改文件名称(要关闭Capture)

2,修改原理图大小

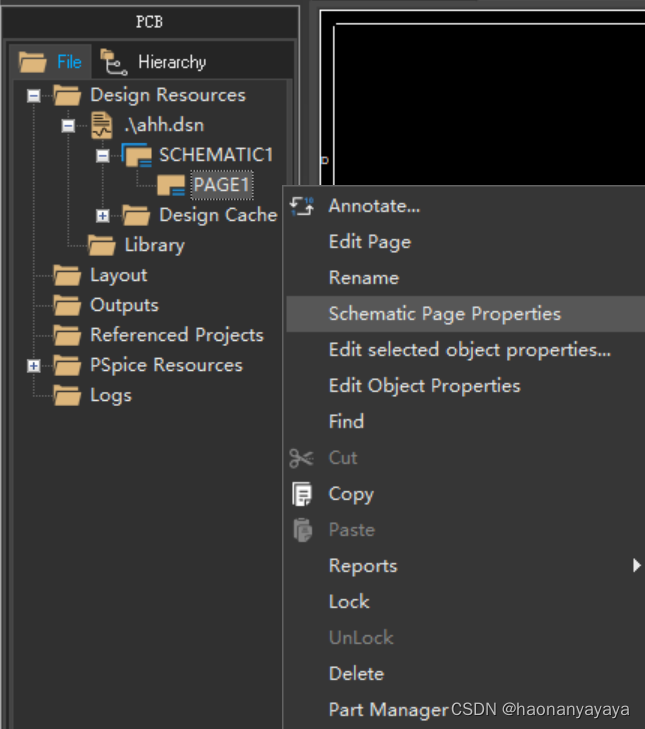

(1)右键原理图页,选择Schematic Page Properties

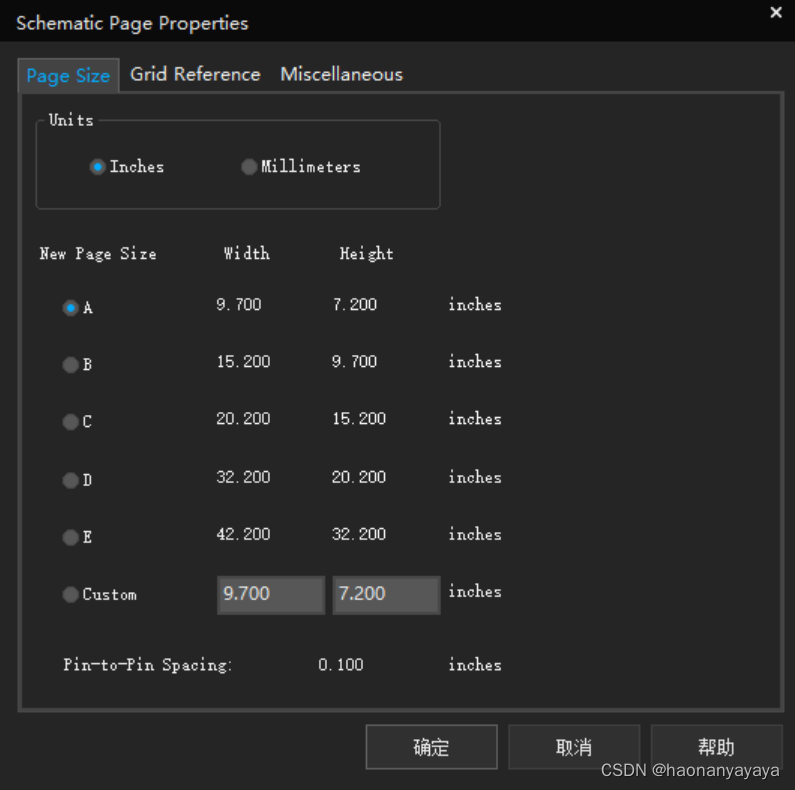

(2)选择需要的原理图大小(默认A4)

Inches以英尺为单位 Millimters以毫米为单位

(三)元器件联通相关

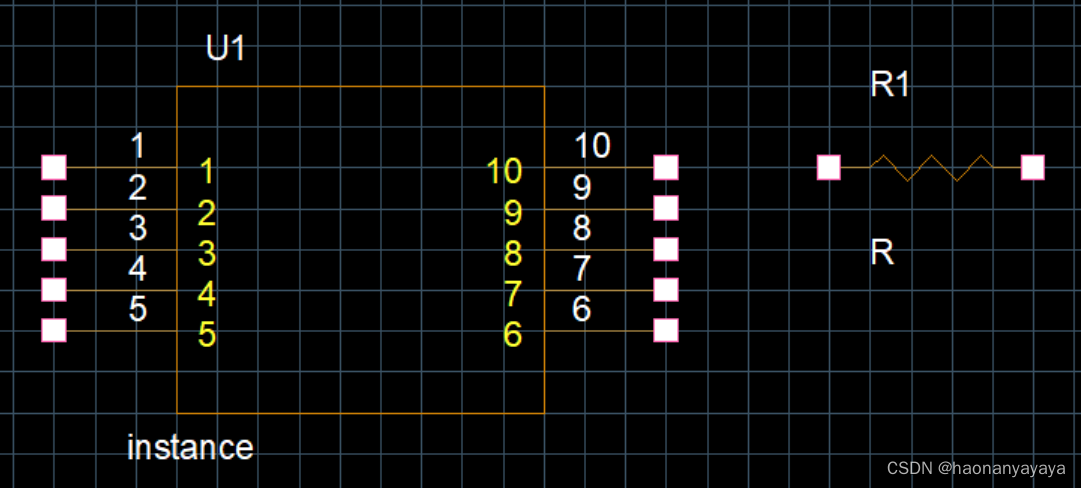

1,放置元器件

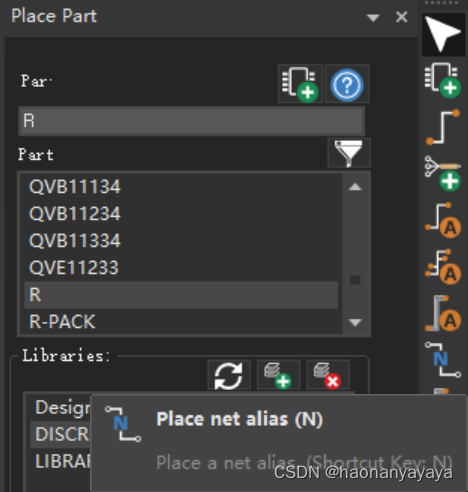

(1)先点击Place再点Part

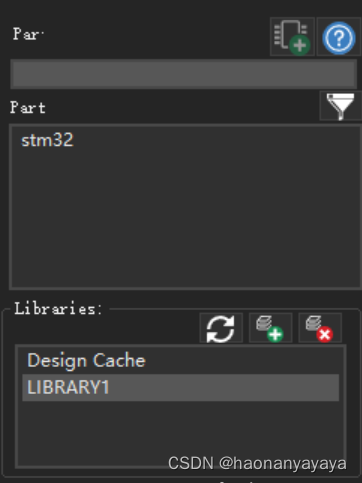

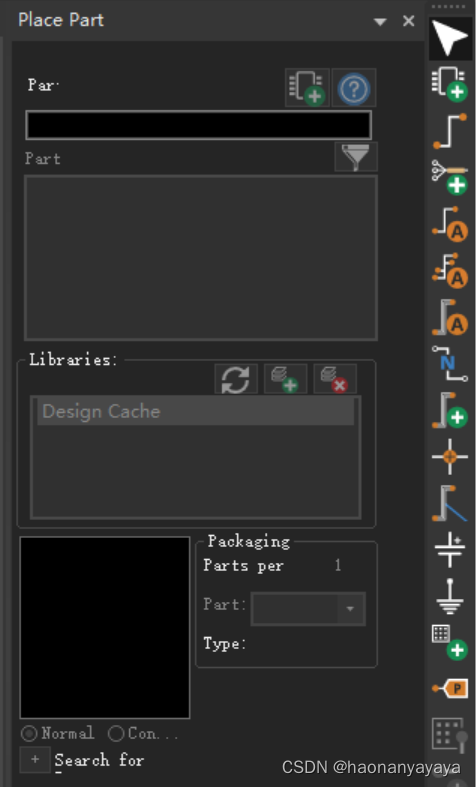

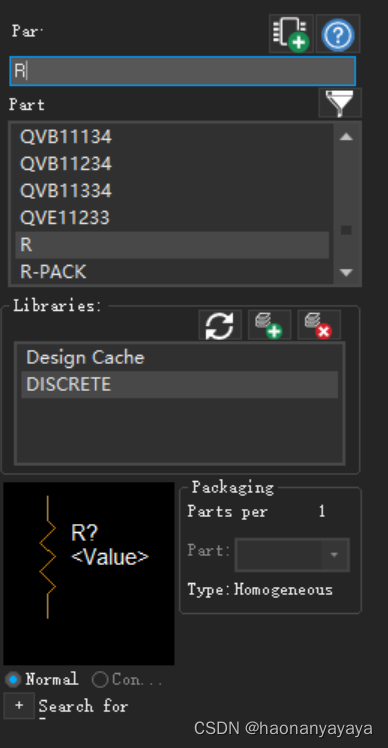

右边出现

(2)点击书籍和加号的按钮添加元器件

默认会跳到library库

(3)添加需要的库

这里以添加常规元器件库(Discrete)为例

电阻,电容等常规元器件都在这个库中

(4)找到需要的元器件

这里以电阻为例,如果要电阻,就在Par输入R,就会跳转

(5)双击元器件

(6)放置元器件

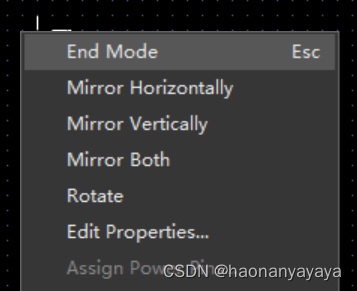

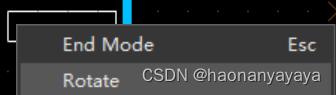

取消放置按Esc或者鼠标右键选择End Mode

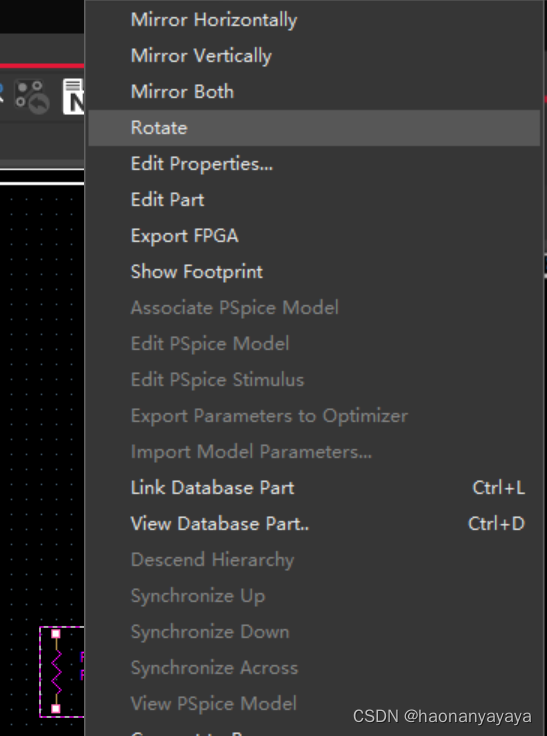

(7)旋转方向

方法一:选中元器件后右键点击Rotate

方法二:选中元器件后按:键盘R

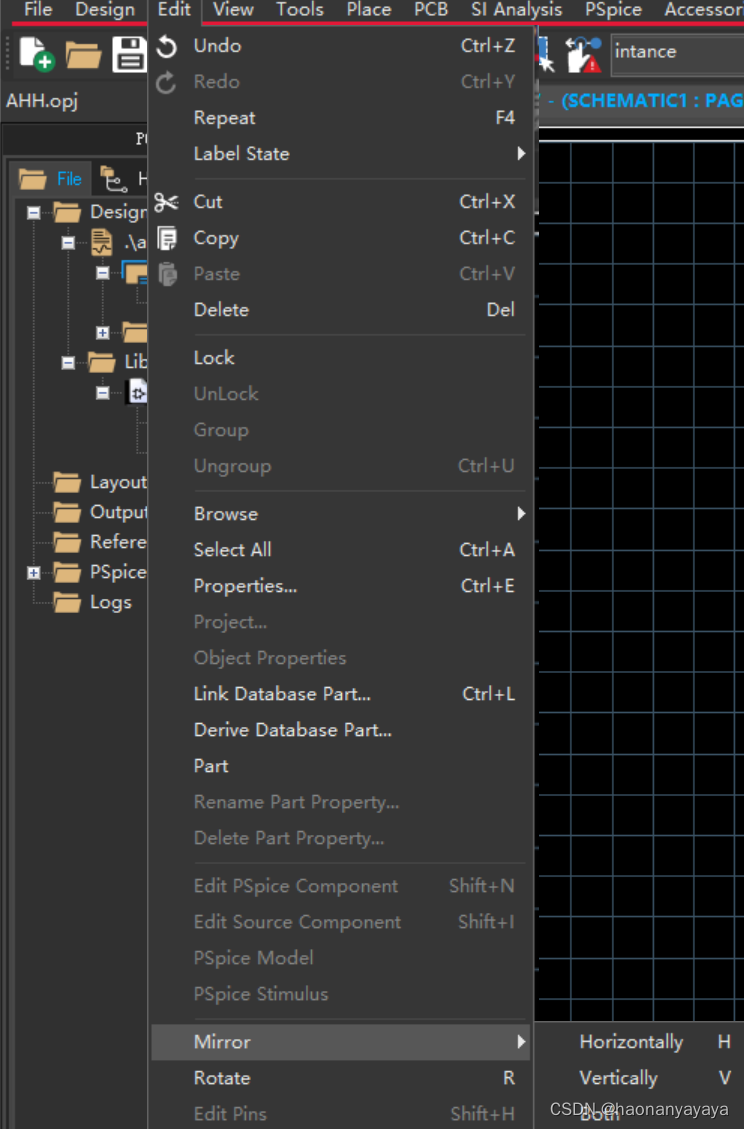

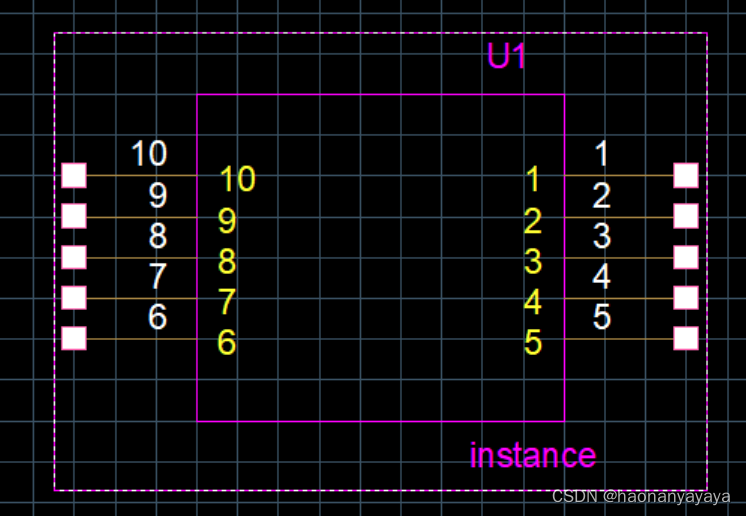

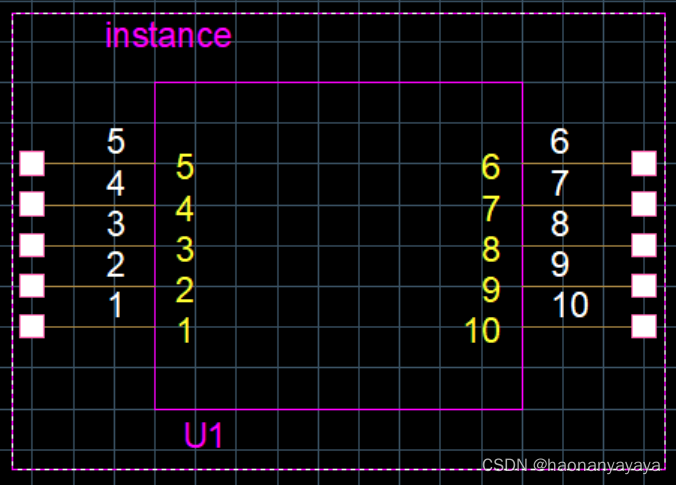

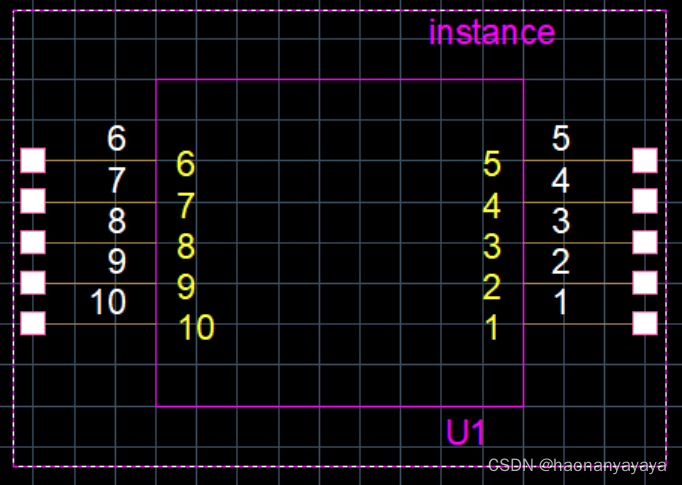

2,镜像功能

(1)选中元器件

(2)点击Edit,Mirror,选择要翻转的方式

Horizontally水平翻转

Vertically垂直翻转

both全部翻转

3,导线连接

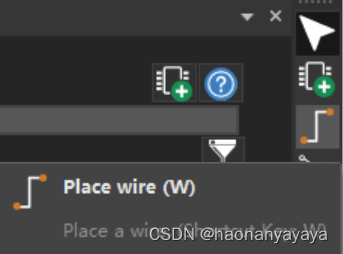

(1)点击有边框的Place wire按钮或者按快捷键W

(2)点击要连接的部分(白块)

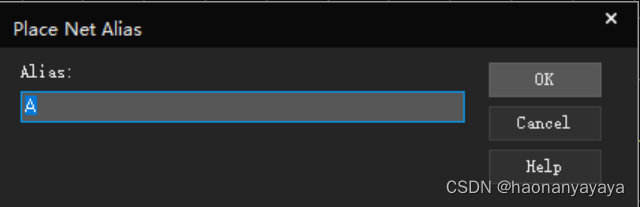

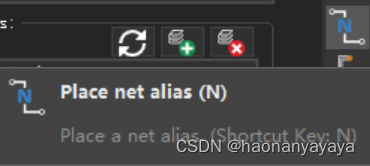

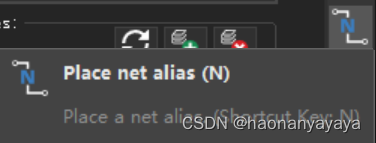

4,放置网络标号图标

作用:通过标识符匹配两端相互连接,将原理图导入PCB,这两个管脚就相互连接

好处:分块绘制原理图看的也非常清楚

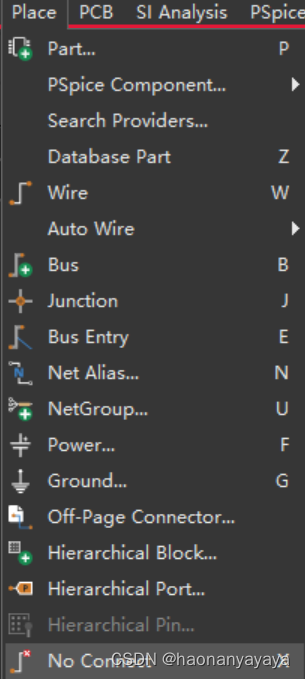

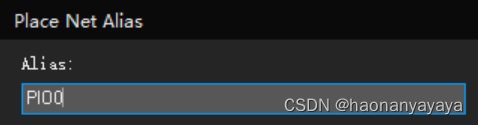

(1)点击右边Place net alias(N)

(2)输入想要的标号,点击OK

(3)选择要放的地方

注:放置在导线上,不论两端是否有连接

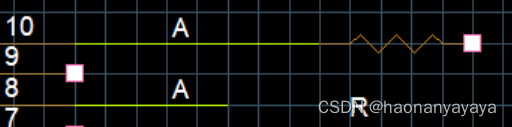

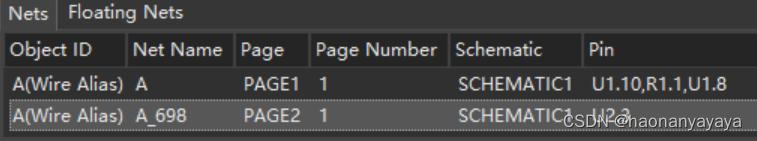

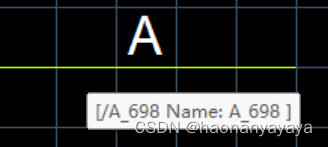

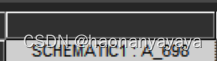

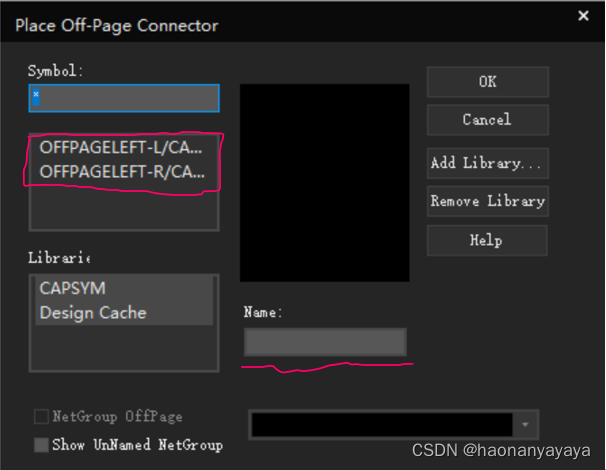

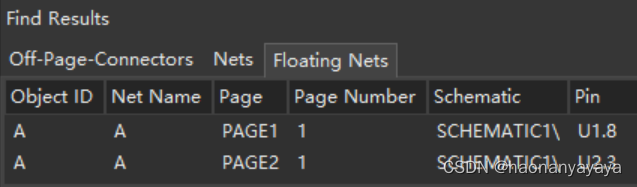

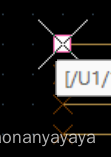

如果在两个页面使用了相同的字母,使用Ctrl+F会发现名字后加了东西,但是图上没有加,因为这是系统自己添加的,如果两根线名字不同就会导致两页间的线没有连接上

鼠标指着这个线或者双击这根线就会发现名字改了

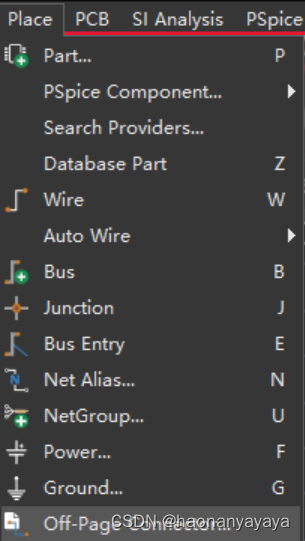

(4)点击PLACE和Off-Page Connector

(5)根据需要选择左边和右边,再修改名称

(6)放置分页符(在所有分页连接的地方都要放置)

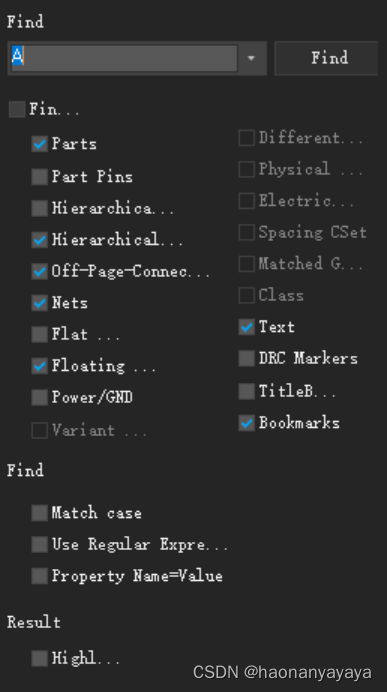

(7)使用Ctrl+F看是否名称一致

注意:不同的页面之间,不仅要添加网络名称,还要添加分页符才能将网络连上

注意:查找的时候不要选中单页

5,表示未连接

(1)点击Place和No Connect

(2)点击空白方框

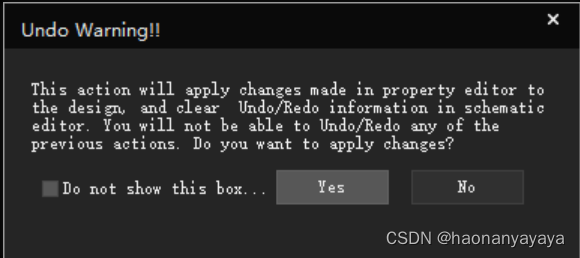

删除未连接方法:

(1)双击未连接的线

(2)将Is No Connect的勾去掉

(3)关闭页面

如果出现下图就点击Yes

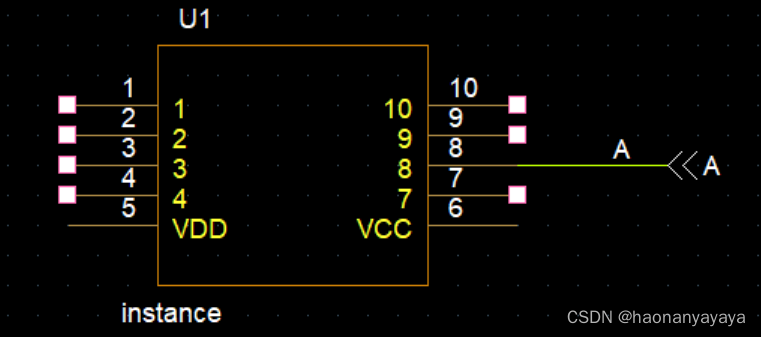

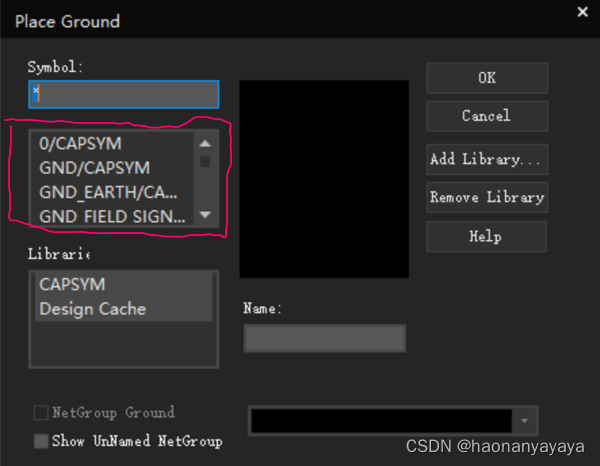

6,电源,地的联通

知识点(很重要):

1,系统自带电源/地连接符的库,不用添加,直接点击放置电源地的按钮放置

2,电源/地是全局变量,不同的页面也可以进行连接,不用添加分页符

3,自定义电源/地连接符的Name名称,即可将原理图上电源/地全部联通

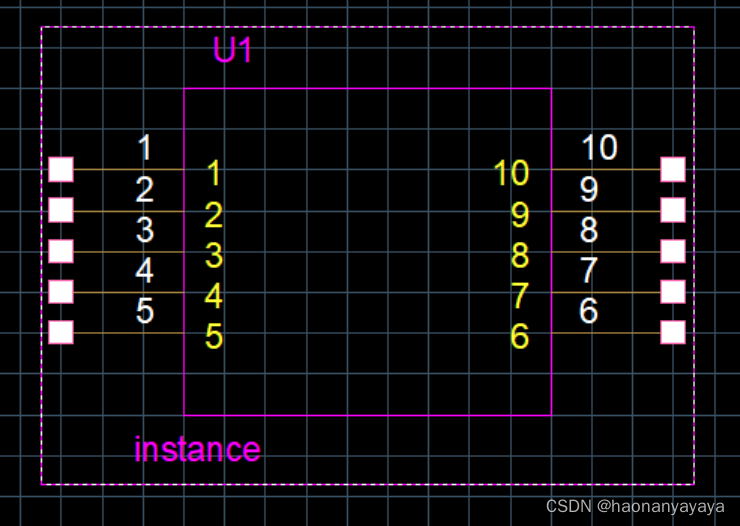

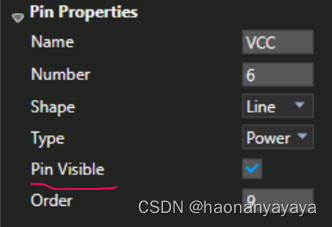

可以看到这里5脚和6脚是电源引脚,这里是没有方框的,这是为了区分

图是随意画的,仅仅用于演示

(1)找到图标

右侧边沿栏找到下面两个,白色是电源,黑色是地

(2)找到自己需要的样式并点击OK

打开后可以看见红色框内东西是一样的,这是因为他们都在CAPSYM这个库中

使用滚轮或者右边黑点向下拉,可找到VCC

(3)鼠标左键放置

(4)通过连线方式连上

注意:电源无法设置未连接(No Connect),即第五条

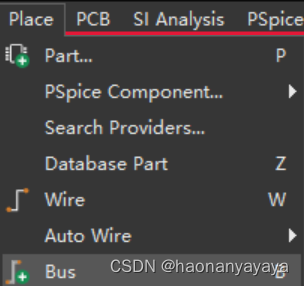

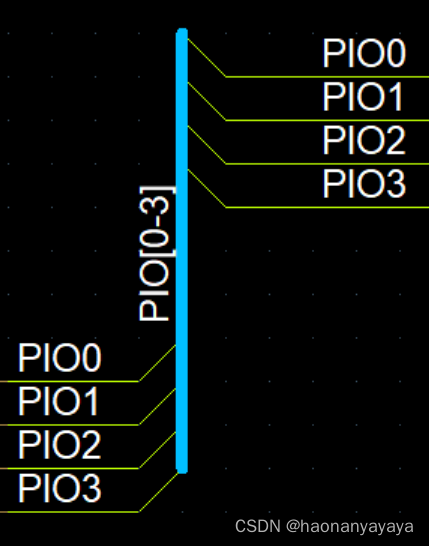

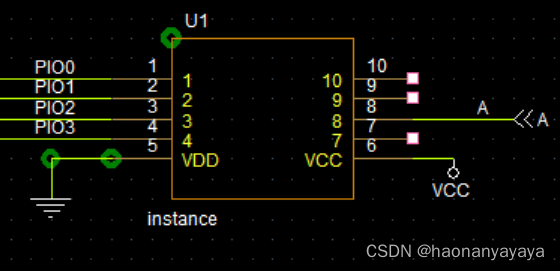

7,BUS总线放置

(1)点击Place和Bus

(2)绘制总线

(3)命名总线

方式和前面放置网络标号一样

注意:命名格式为名称+[x-y],例如 PIO[0-3] PIO为名称,[0-3]为线,这个中括号不要丢

(4)改变命名方向

可以看到,我的总线是竖直的,但是方框是横的

点击鼠标右键之后点击Rotate就可以旋转

(5)单机鼠标左键放置

(6)点击Place和Bus Entry

(7)放置总线入口

旋转方法为点击鼠标右键之后点击Rotate

(8)使用导线将引脚与入口相连

(9)放置网络标号

(10)将标号改为PIO+之前的设置x~y内的数字

最终如图

8,添加差分属性

(1)选中要添加差分属性的页面

(2)点击tools和Creat Different Pair

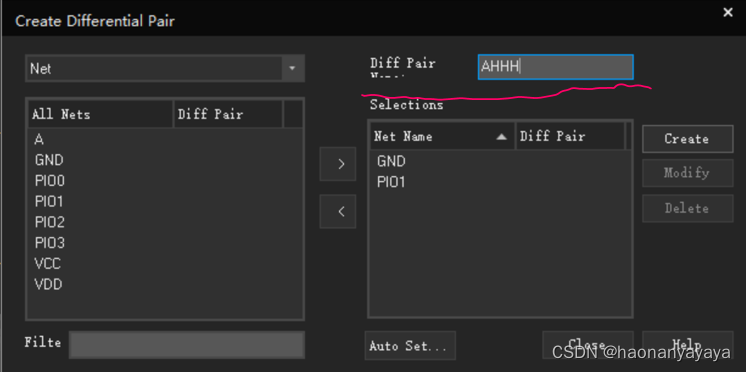

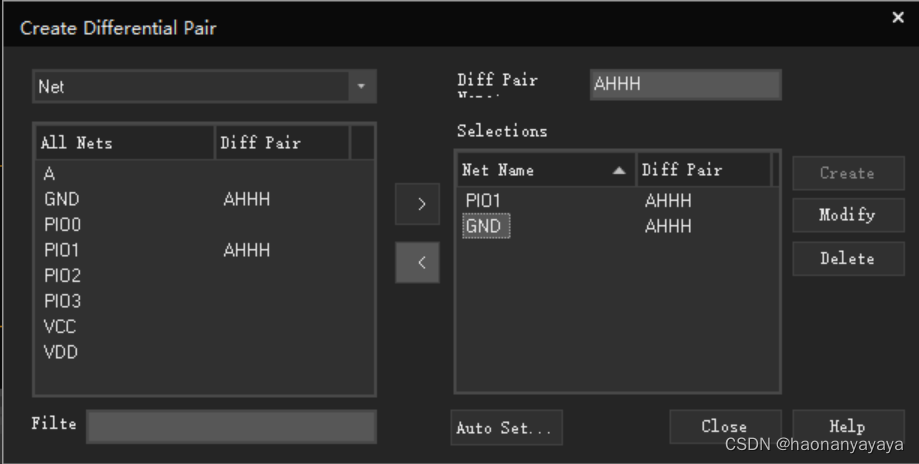

(3)找到需要改为差分信号的网络

查找:选中其中任意一个网络,输入要查找的网络名称首字母

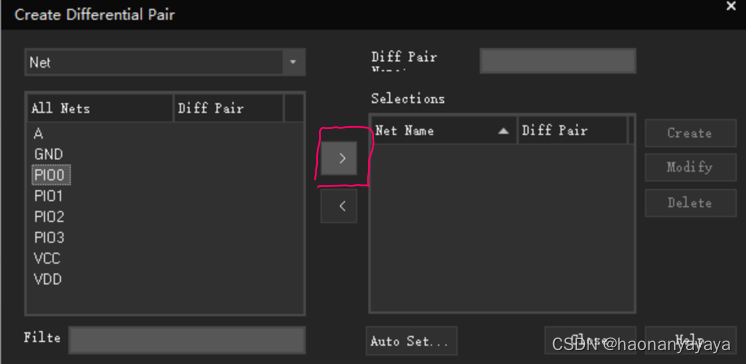

(4)双击网络名称或按下图方框内按钮

(5)修改名称(非必要)

(6)点击Create

如果要添加其他差分队就先将组内的移走再重复上面步骤

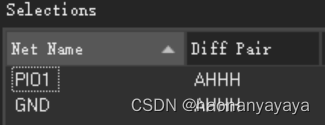

(7)双击设置的引脚可以看见出现了设置的名字

![]()

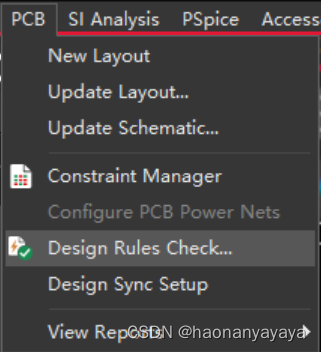

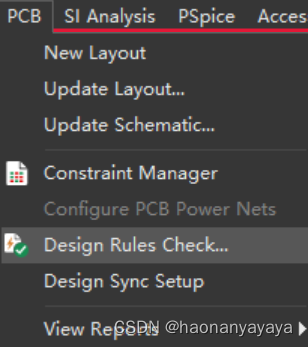

(四)设计规则检查(DRC)

首先点击PCB和Design Eules Check

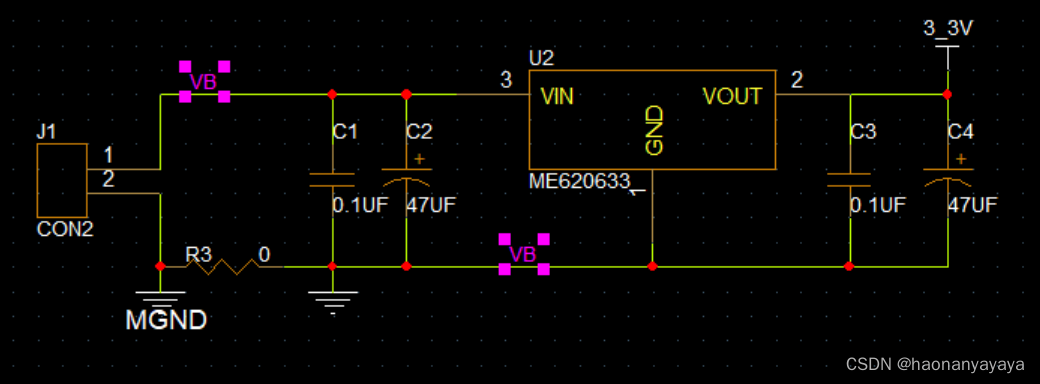

注意:这个机制不是万能的,例如下图的VB短路,不报错的原因是系统不知道VB是否需要和GND连接

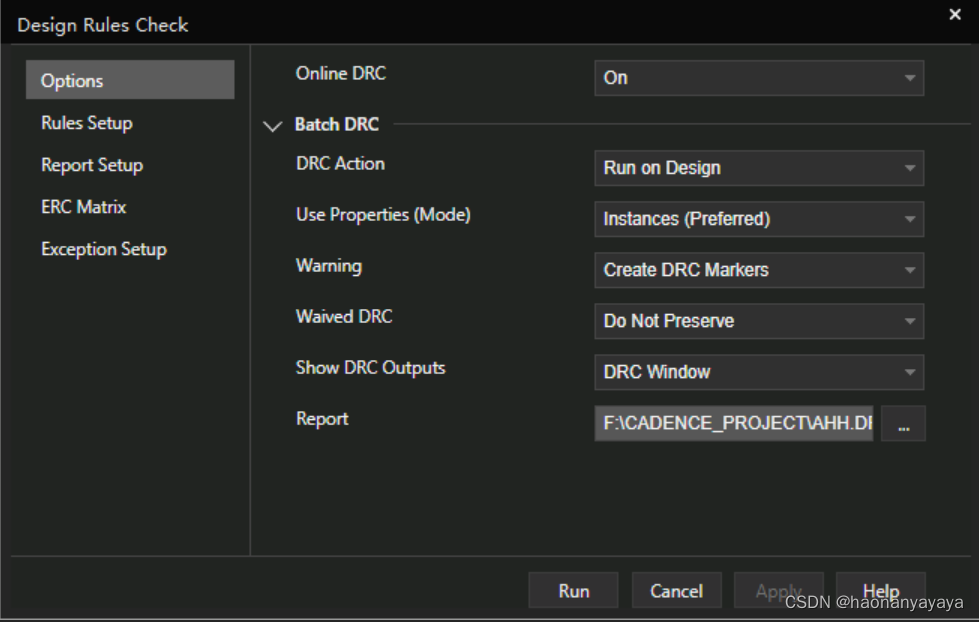

1,参数面板(Options)

(1)Online DRC:在线DRC是否开启,在绘制DRC的时候,有错误会在线显示

![]()

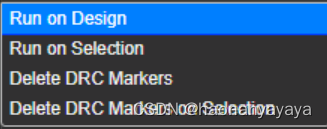

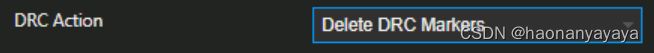

(2)DRC Action:DRC操作,有四个选项

![]()

第一个是在设计中使用

第二个是在选中的特定区域中使用

注:在DRC检测完后会对原理图做一个标记

第三个是删除DRC标记

第四个是删除选中的特定区域DRC标记

(3)Use Properties(Mode):用户DRC检测模型

![]()

分为平坦式Instances和层次式Occurrences,一般使用Instances

(4)warning:警告,是否创建DLC标记

![]()

一般情况是Crete DRC Markers

(5)Waived DRC:进行设计规则检查时,忽略或放宽这些规则的要求,并将其视为符合规定

![]()

一般情况是Do Not Preserve

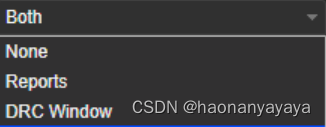

(6)Show DRC Outputs:显示DRC输出

第一个是全都显示

第二个是不显示

第三个是报告显示

第四个是Window显示

(7)报告产生路径

![]()

一般情况下放在原理图所在的路径下

注意:路径不能包含中文,否则报错

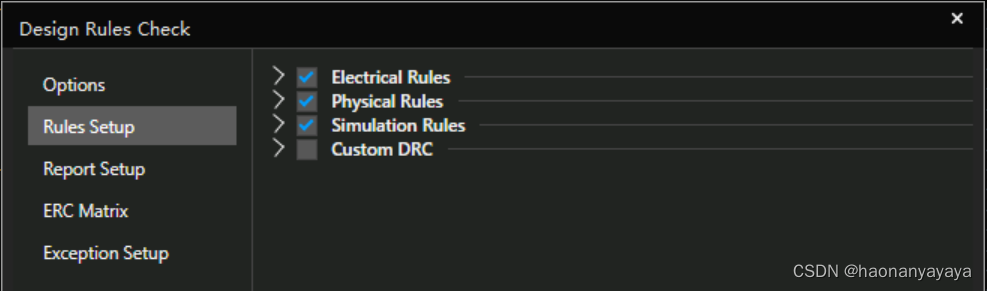

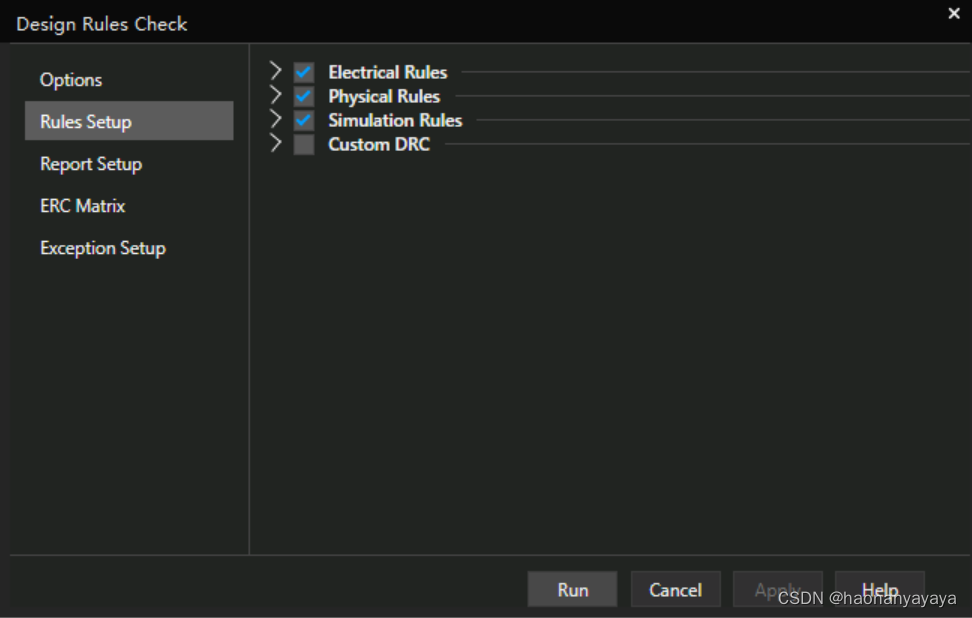

2,规则设置(Rules Setup)

首先可以看到方框和勾,打勾了就是检查,没打就是不检查

展开后可以看到分为了Batch和Online

前面这一项是使用DRC的时候检查,第二项是绘制原理图的时候能够将DRC在线显示

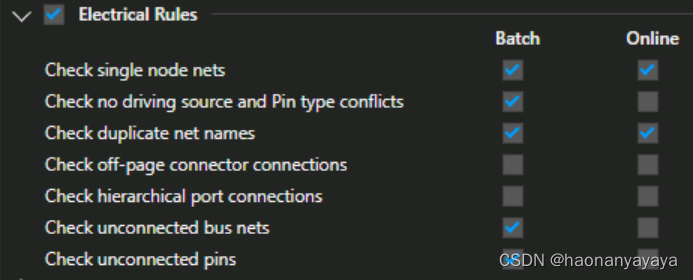

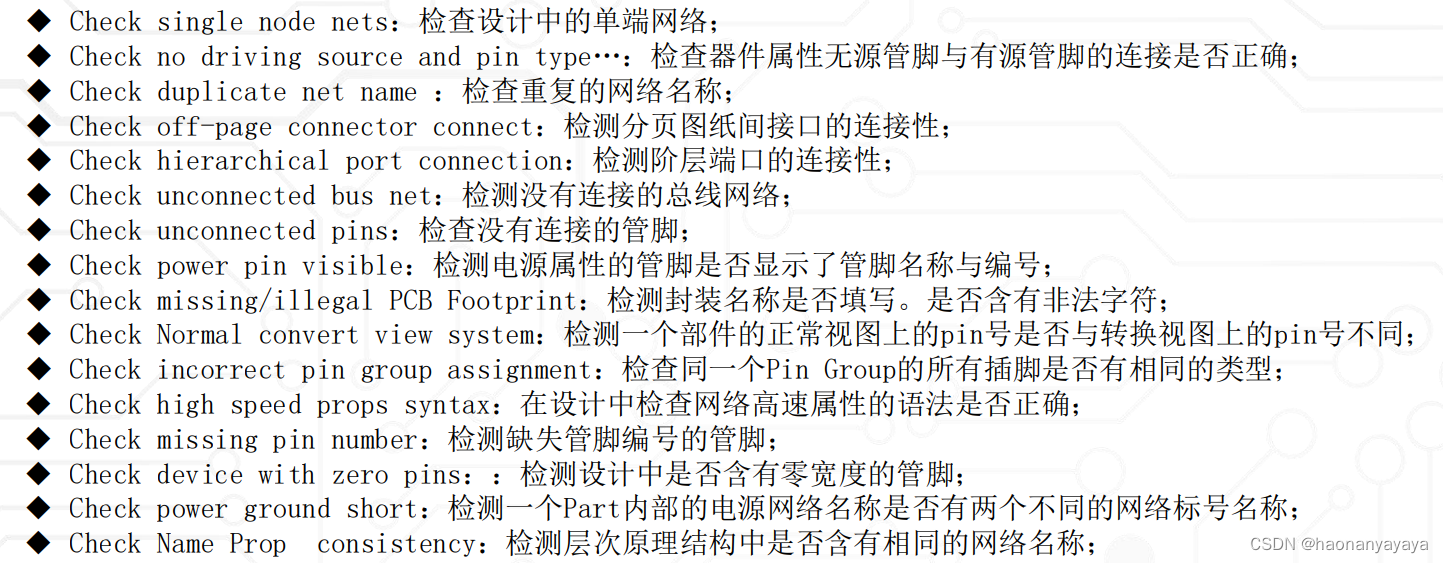

(1)电气规则检查(Electrical Rules)

a,Check single node nets:检查设计中的单端网络;

单端网络:一个点引出但并未与其他点连接

用于检查分页符问题,可以看(三)元器件联通相关的放置网络标号图标

b,Check no driving source and Pin type conflicts:检查器件属性无源管脚与有源管脚的连接正确;

引脚设置的是电源管脚,但是接的是信号脚,这个时候就会报出来,检查是否有问题,又或是电源管脚没有连接

c,Check duplicate net name :检查重复的网络名称;

有些名称重复,是否需要合并或者连接在一起,确认一下就行

d,Check off-page connector connect:检测分页图纸间接口的连接性;

自动检测分页图纸之间的接口连接性是否正确。它会比对每个页面上的接口,确保它们与其他页面上的相应接口连接一致,更多用于大型项目中,这里默认不勾选,按默认就行。

e,Check hierarchical port connection:检测阶层端口的连接性;

与上面那个差不多

f,Check unconnected bus net:检测没有连接的总线网络;

检查总线网络是否连接

g,Check unconnected pins:检查没有连接的管脚;

这里是提示是否需要连接而不是不连接就是错误的

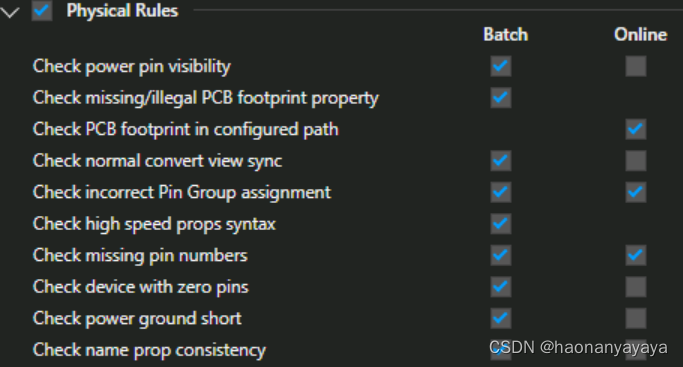

(2)物理规则检查(Physical Rules)

a,Check power pin visible:检测电源属性的管脚是否显示了管脚名称与编号;

下图为勾以后和勾以前,不勾也行,影响不大

![]()

目的是确保所有电源引脚在设计图中都是可见的,没有被遮挡或隐藏

这样可以确保电源引脚在布局和布线过程中能够被正确连接和处理,避免电源供应的问题。

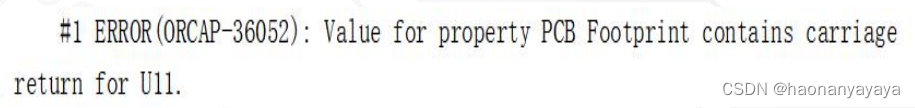

b,Check missing/illegal PCB Footprint:检测封装名称是否填写。是否含有非法字符;

这里有问题是肯定要改的,因为在后面网表输出的时候会报错

c,Check Normal convert view system:

检测一个部件的正常视图上的pin号是否与转换视图上的pin号不同;

这个是有的原理图不是OrCAD绘制,要别的工具转换,需要对应一些

d,Check incorrect pin group assignment:检查同一个Pin Group的所有插脚是否有相同的类型;

做FPGA的时候,如果添加了PIN Group组件,就可以在PCB中交换管脚,用于检测PIN Group类型是否相同,如果不同会导致交换管脚功能无法使用

e,Check high speed props syntax:在设计中检查网络高速属性的语法是否正确;

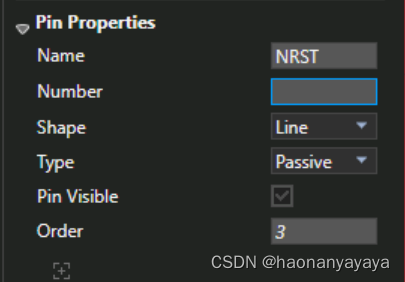

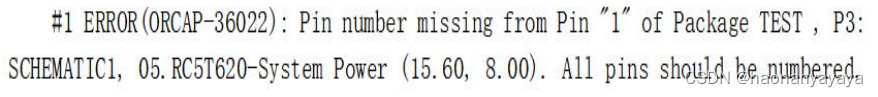

f,Check missing pin number:检测缺失管脚编号的管脚;

这个四号就是缺失编号的引脚

如果缺失的话,在后面输出网表的时候会报错,因为要和PCB封装对应

g,Check device with zero pins:检测设计中是否含有零宽度的管脚;

这个影响不大,因为是原理图,只是为了表达电路之间关系

h,Check power ground short:检测一个Part内部的电源网络是否有两个不同的网络标号名称;

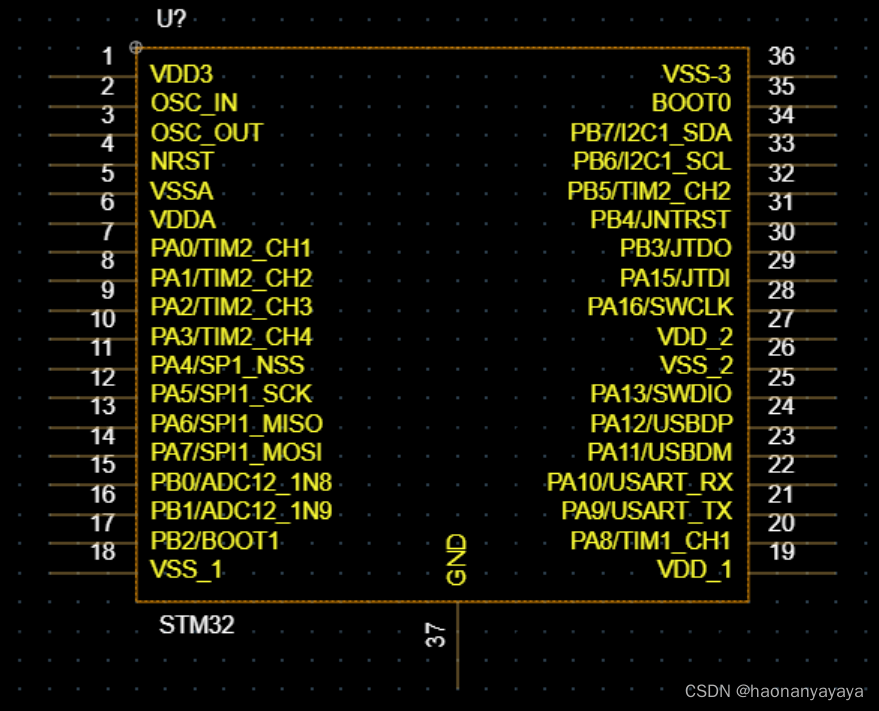

例如这个的VDD_1和VDD3,因为都是电源引脚,接的都是VDD,那么名称应该是一样的,如果名称不同就会提示,这个是可以接受的,比如一个接2.5V一个接3.3V,主要是用于确认

i,Check Name Prop consistency:检测层次原理结构中是否含有相同的网络名称;

如果相同就是有问题,需要修改

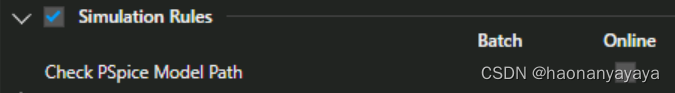

(3)模拟规则(Simulation Rules)

这个需要仿真工具

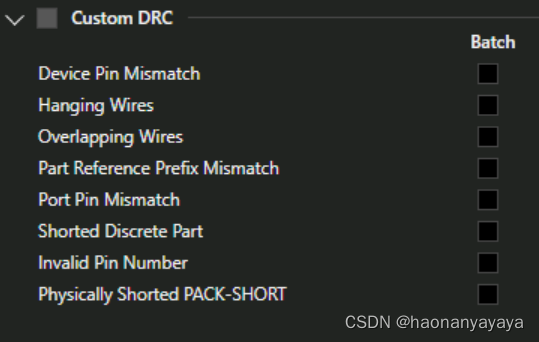

(4)定制设计规则(Custom DRC)

这个建议不要管

(5)总表

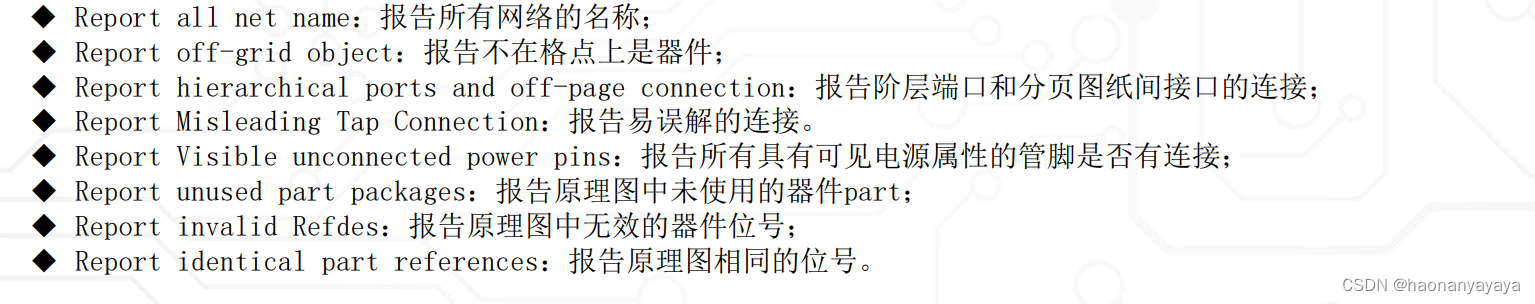

3,报告设置(Report Setup)

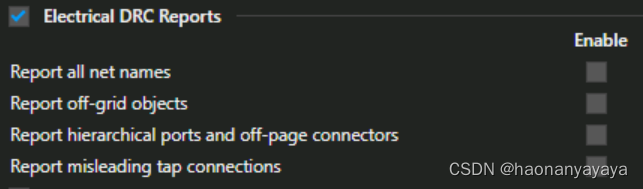

(1) 电气报告设置(Electrical DRC Reports)

a,Report all net name:报告所有网络的名称;

为了检查网络名称是否有非法字符

b,Report off-grid object:报告不在格点上是器件;

就算不在格点上也没关系,只是不符合规范

c,Report hierarchical ports and off-page connection:报告阶层端口和分页图纸间接口的连接;

这个和下面也没必要报告

d,Report Misleading Tap Connection:报告易误解的连接。

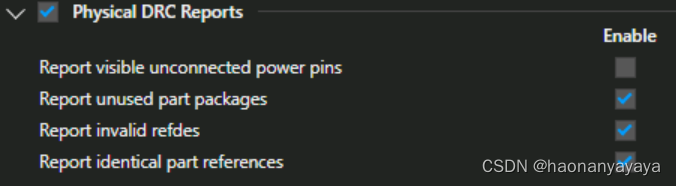

(2)物理报告设置

a,Report Visible unconnected power pins:报告所有具有可见电源属性的管脚是否有连接;

这个前面检查过了,就必要再勾选了

b,Report unused part packages:报告原理图中未使用的器件part;

元器件放在原理图上,但是什么都没有连接,报告一下,到时候删掉,不删就会导入到PCB中

c,Report invalid Refdes:报告原理图中无效的器件位号;

位号中含有非法字符,不识别,需要更改

d,Report identical part references:报告原理图相同的位号。

在原理图中,有两个相同的位号(例如U3),这个时候就需要修改重复的命名

(3)总表

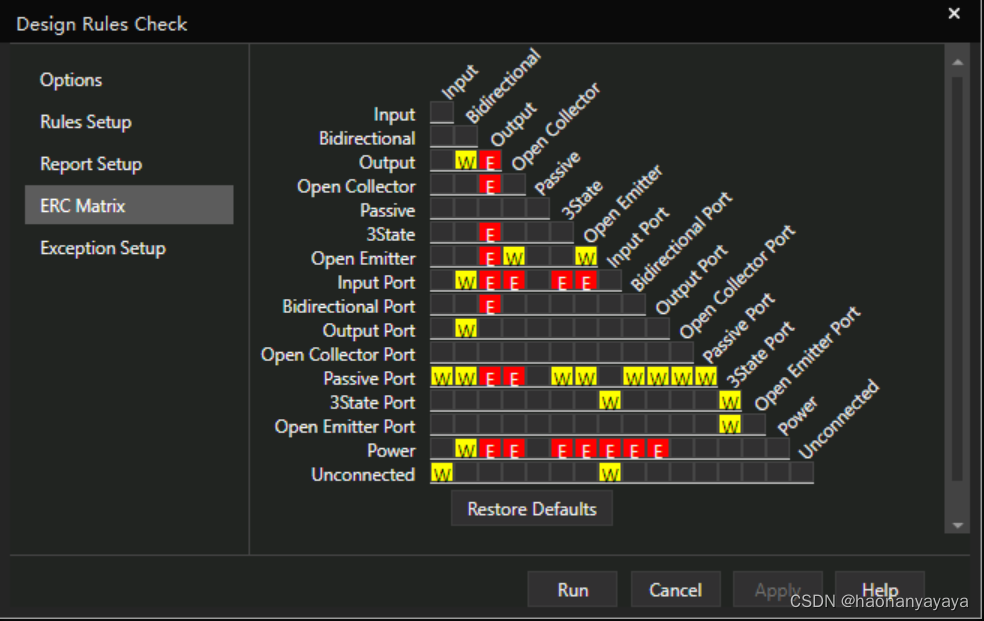

4,ERC矩阵(ERC Matrix)

用于看哪个是报错,哪个是经过,不要轻易去改,用默认就行,Restore Defaults是恢复默认值

5,异常设置(Exception Setup)

设定一个异常处理机制。这个机制可以帮助开发人员在程序运行过程中对可能发生的异常进行捕获和处理,以确保程序的稳定性和可靠性。

这个就不用管了

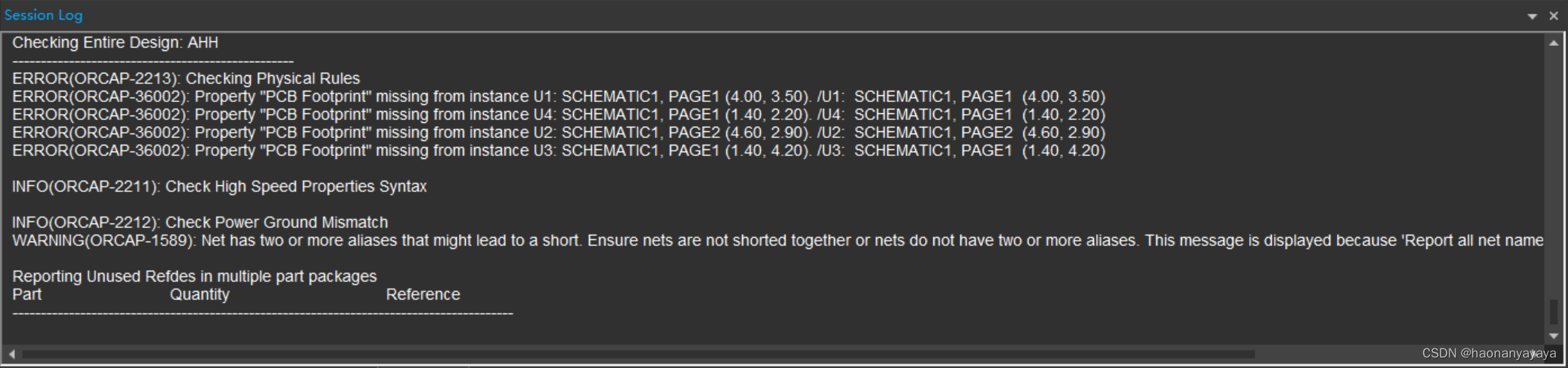

6,运行DRC

(1)点击RUN

(2)出现一个或者多个错误,询问是否要看错误消息,选择是(Y)

(3)查看错误信息

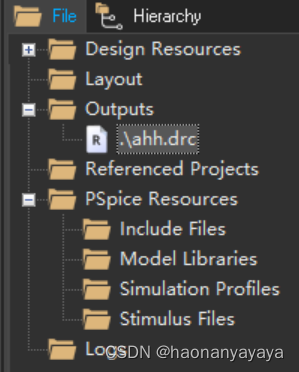

左下角出现错误信息

也可以在Output中的drc文件中查看

在有警告的位置,图中也会出现一些绿色圆圈

注:有些是没有问题,但是不符合设计规范

消除绿色圆圈:

(1)这个时候只需要点击PCB和Design Rules Check

(2)修改DRC Action为Delete DRC Markers再点击Run,这些圆圈就会消失

(五) PDF与BOM清单输出

1,PDF导出

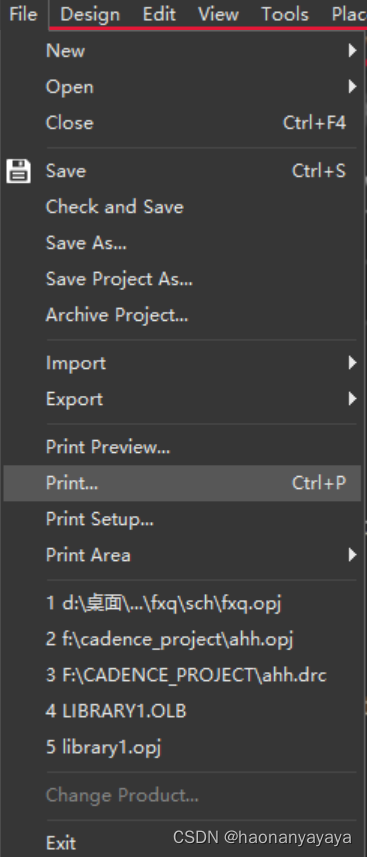

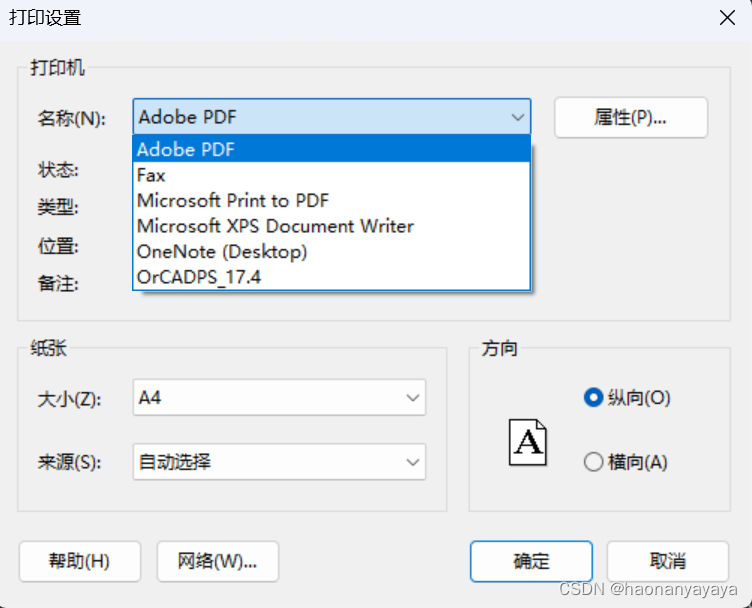

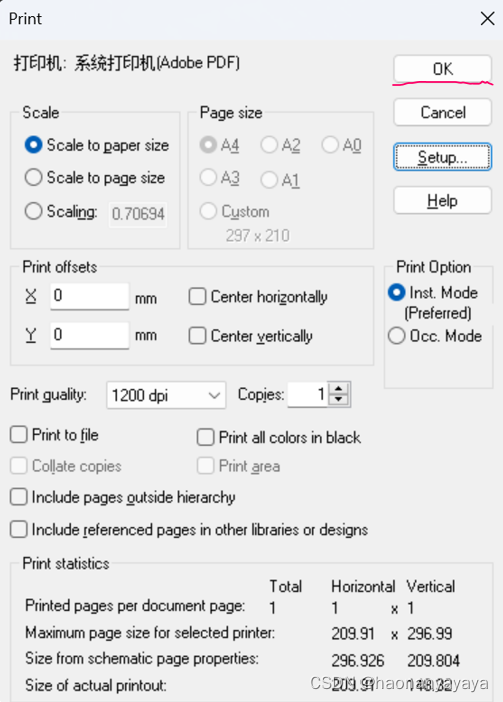

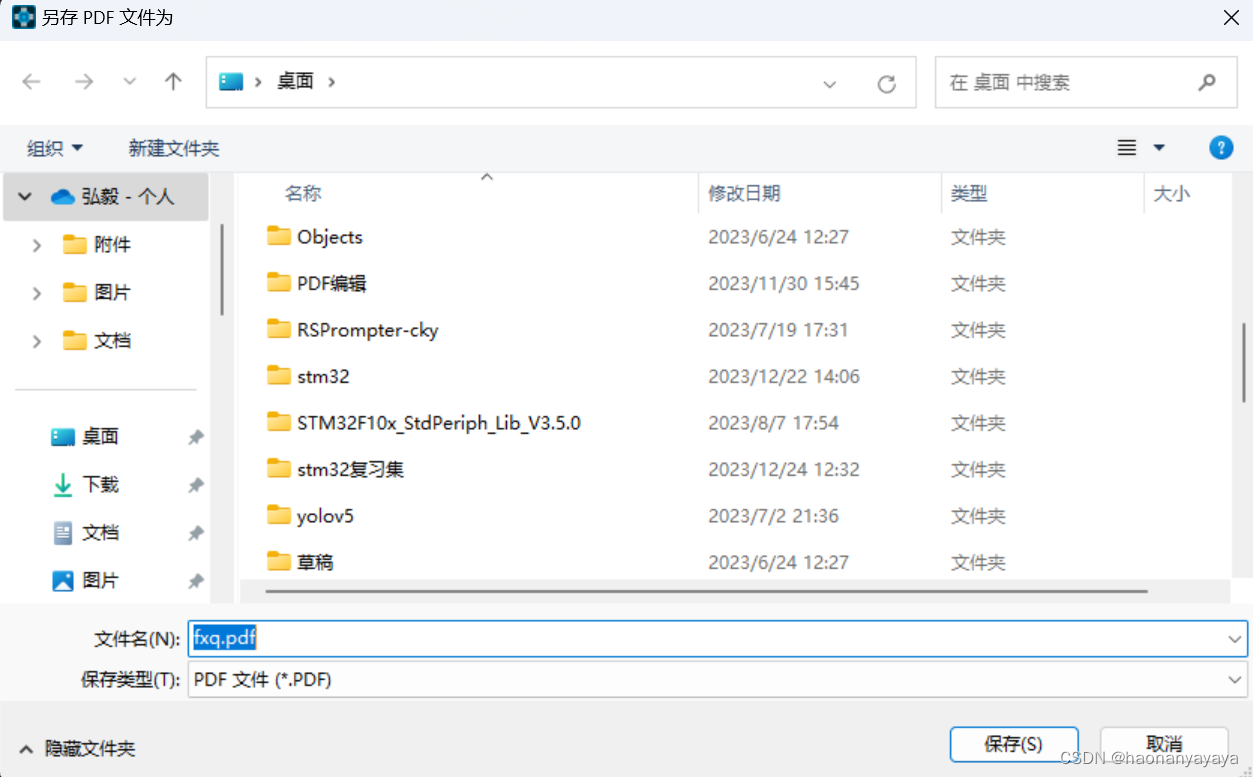

方法一

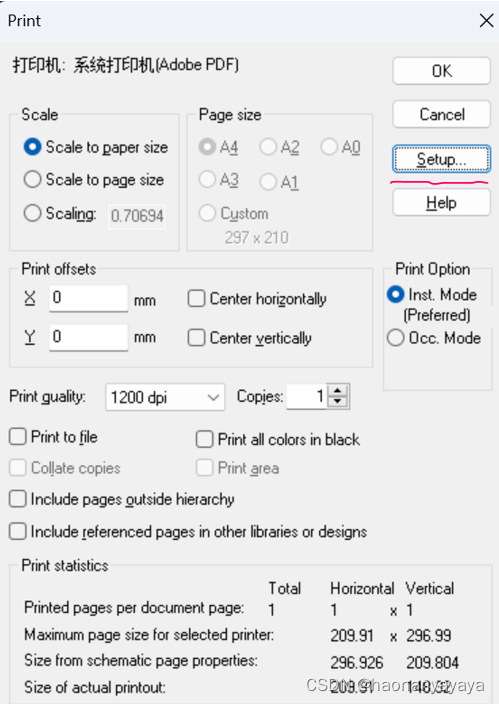

(1),选中根目录(dsn文件)

(2),点击File和Print

(3),点击Setup

(4),点击小箭头,选择虚拟打印机,我这里选择Adobe PDF

(5),点击OK

(6),选择要保存的地方后点击OK

(7),在刚刚保存的地方就可以找到pdf文件

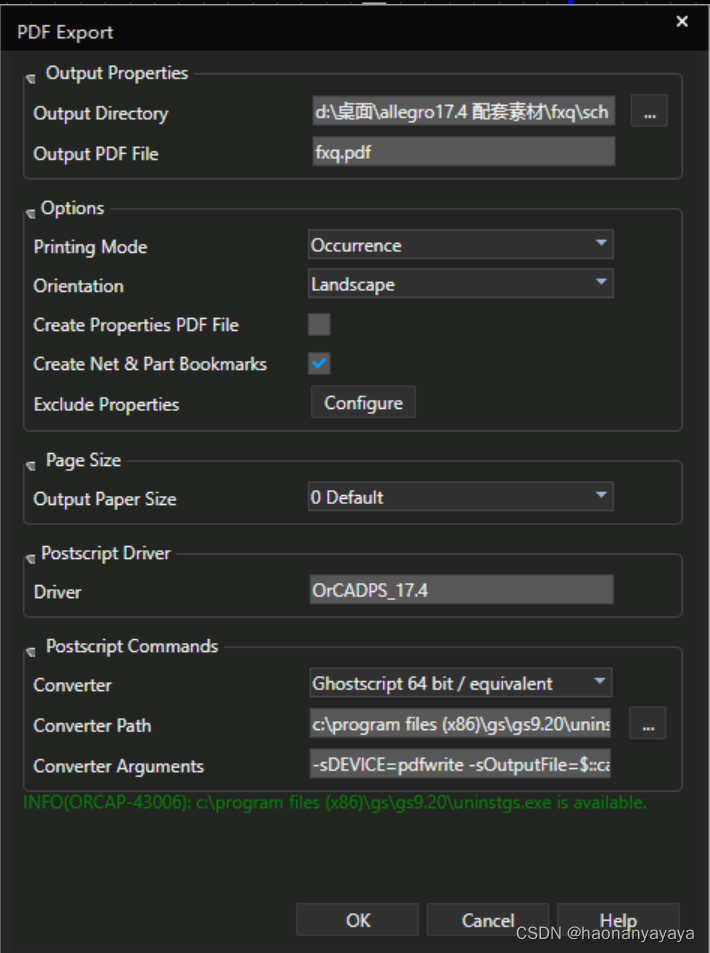

方法二(需要Ghostscript插件)

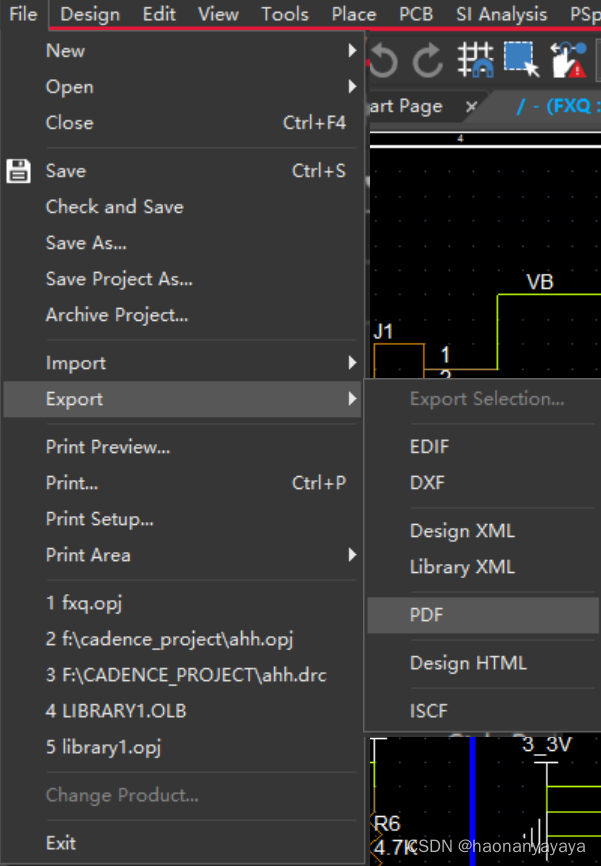

(1),选中根目录(dsn文件)

(2),点击File,Export和PDF

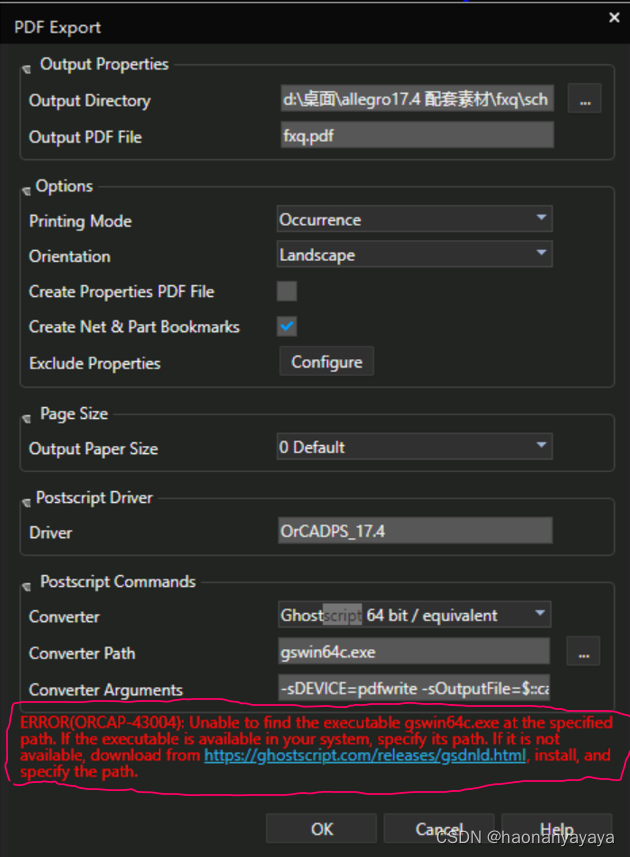

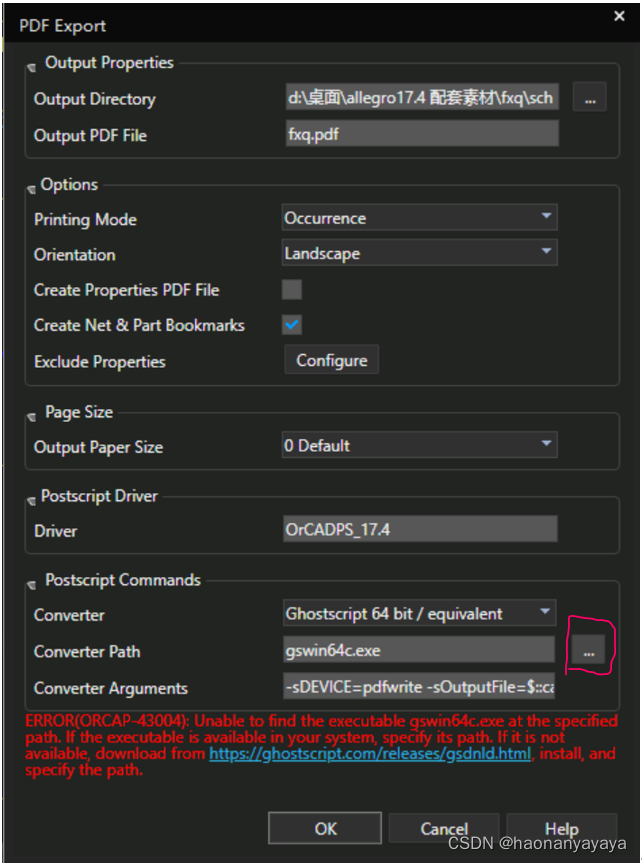

(3),看是否出现ERROR(ORCAR-43004)

如果出现了就是没有安装插件(查看后面补充部分)

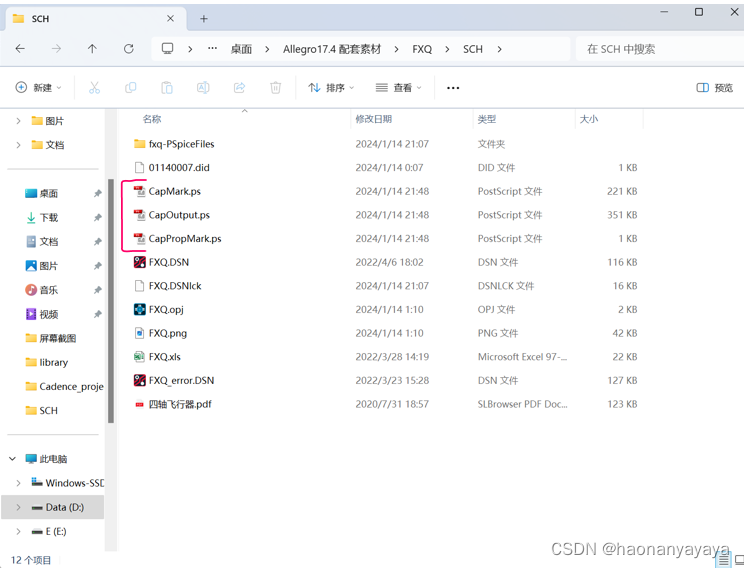

(4),点击OK

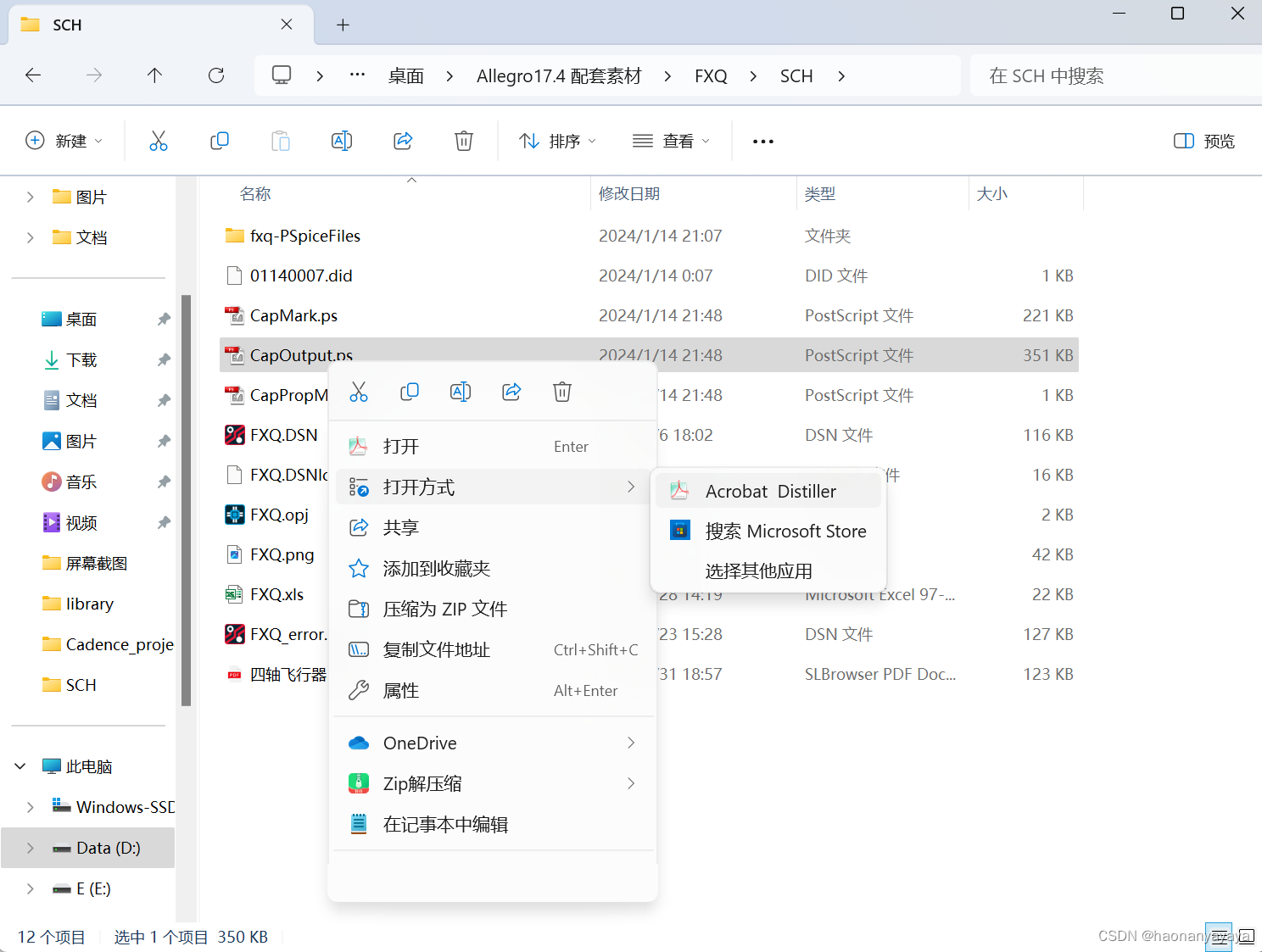

(5),出现三个后缀是PS文件(只有CapOutput.ps是需要的)

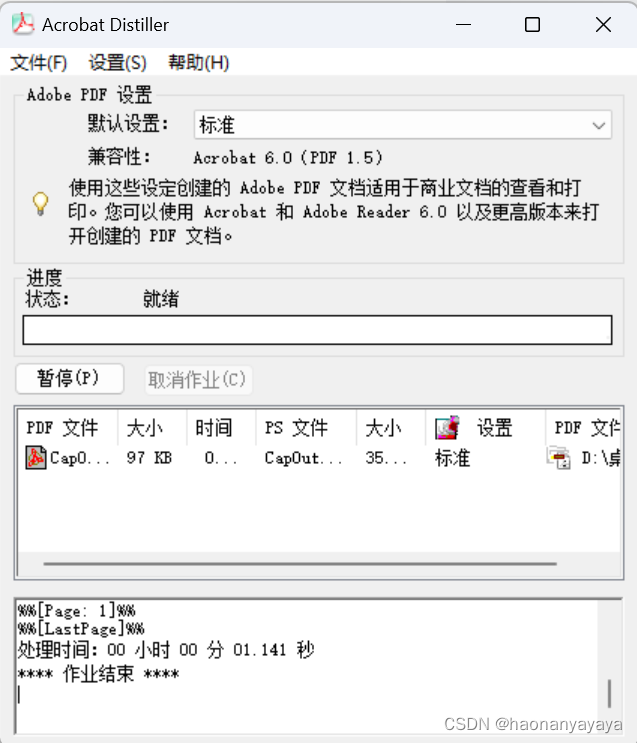

(6),点击CapOutput.ps,右键选择打开方式,选择Acrobat Distiller

(7),等待出现下面这个页面后

(8),返回文件夹就会发现出现下面的pdf文件

![]()

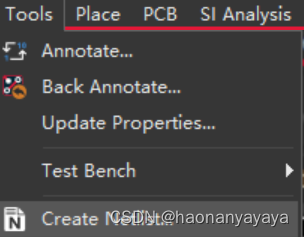

2,输出BOM清单

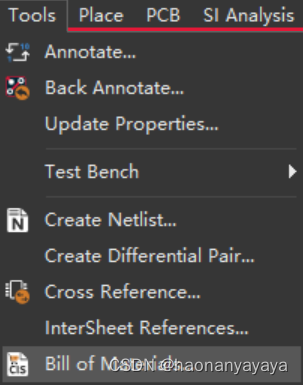

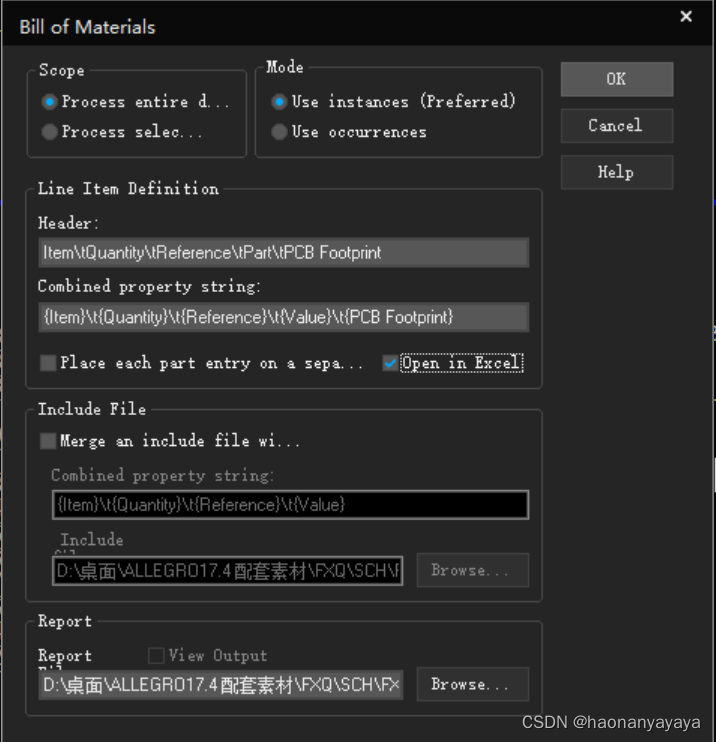

(1),选中根目录(dsn文件)

(2),点击Tools和Bill of Materials

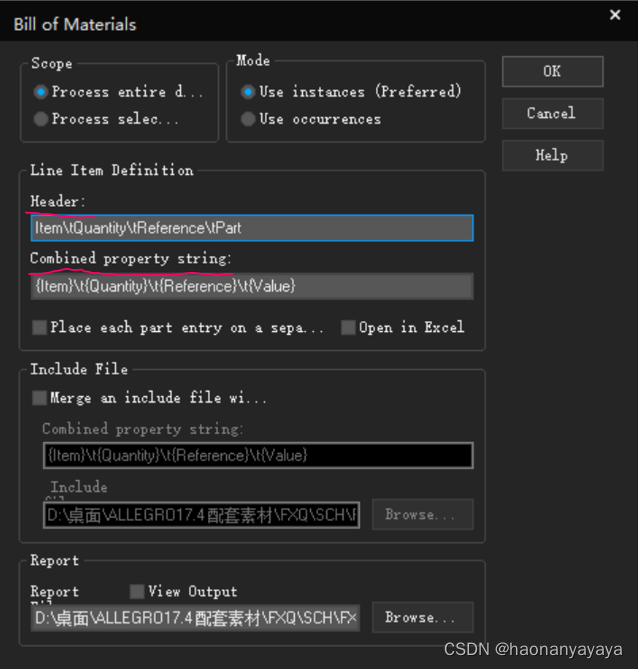

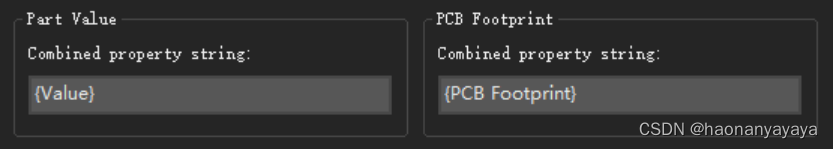

(3),打开后看到以下界面,这里是缺少了封装

(4),Header的格式是\t+名称,添加封装就是\tPCB Footprint

最终为Item\tQuantity\tReference\tPart\tPCB Footprint

Combined property string的格式是\t+{名称},添加封装就是\t{PCB Footprint}

最终为{Item}\t{Quantity}\t{Reference}\t{Value}\t{PCB Footprint}

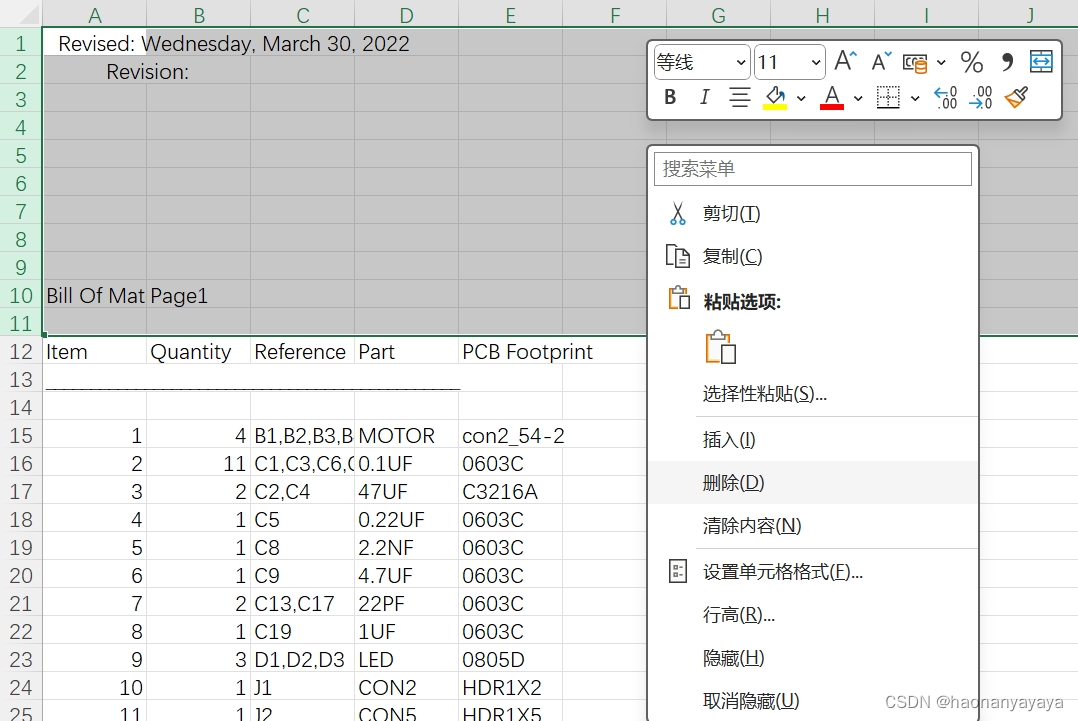

(5),将Open in Excel打上勾,再点击OK

(6),excel会打开生成一个表格,这个表格就是BOM清单(前几行可以删除)

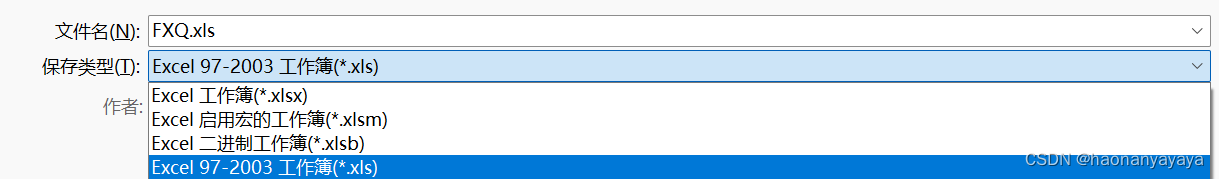

(7),可以将文件另存为放在原理图下面

注意:第一次保存类型默认为txt,记得换为xls格式

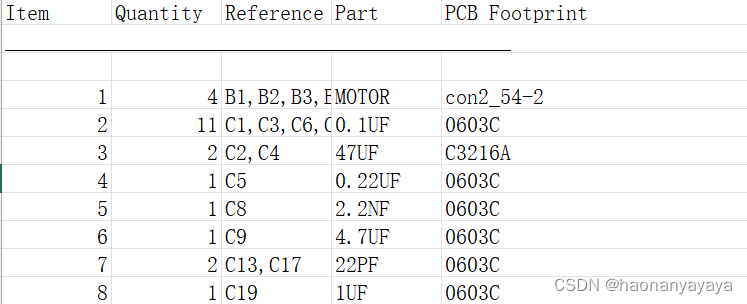

(8),可以看到有五类,分别为:顺序,数量,位号,属性值,封装

补充:安装Ghostscript插件

(1),打开下面连接,点击本地下载

Ghostscript下载-Ghostscript官方版下载[电脑版]-pc下载网

(2),选择电信下载

(3),双击下载好的exe文件

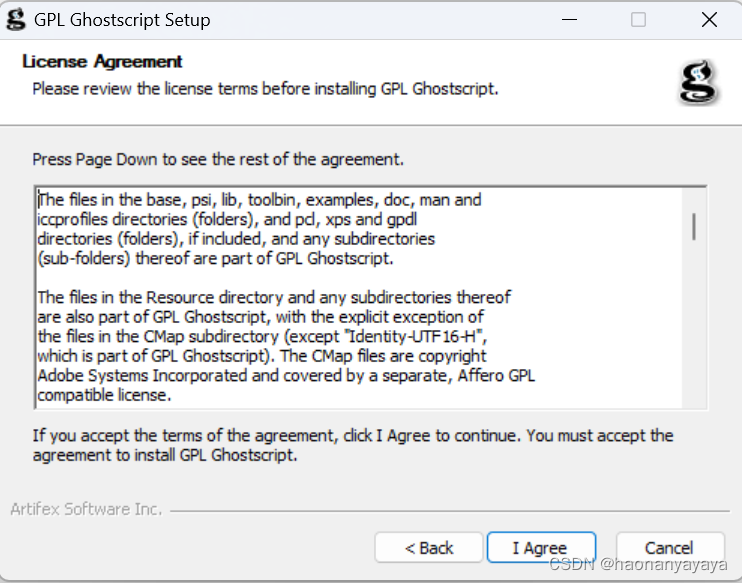

![]()

(4),将exe文件出来的压缩包解压

(5),得到gs920.xzzj.exe,s双击打开

(6),点击next和I Agree

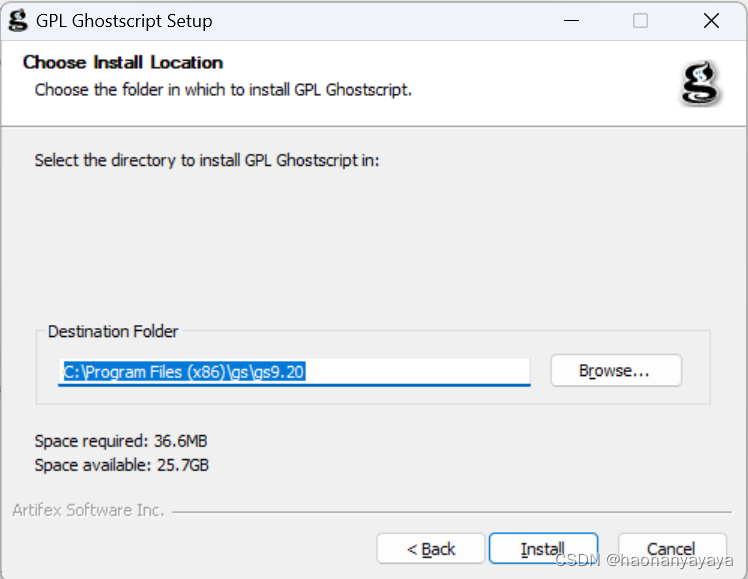

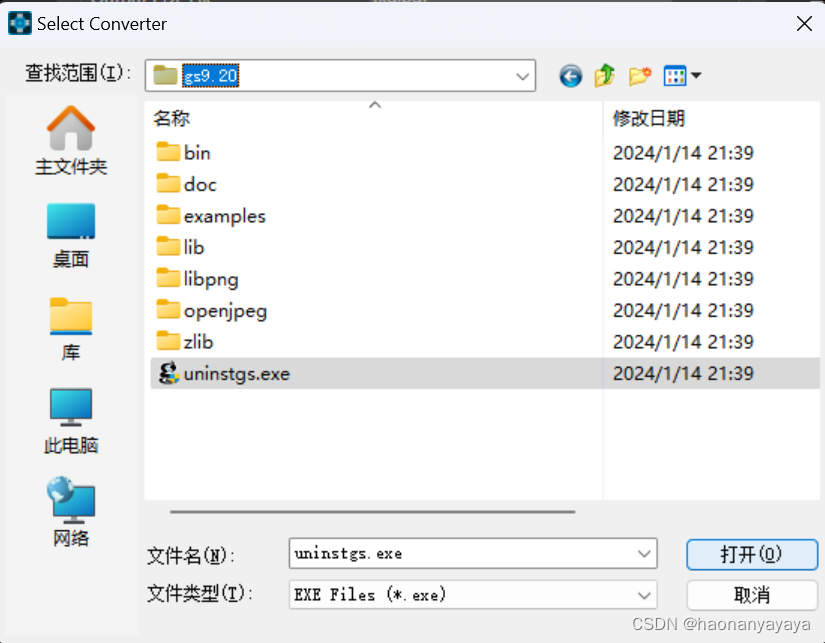

(7),记住这个路径,点击Install,我的路径是C:\Program Files (x86)\gs\gs9.20

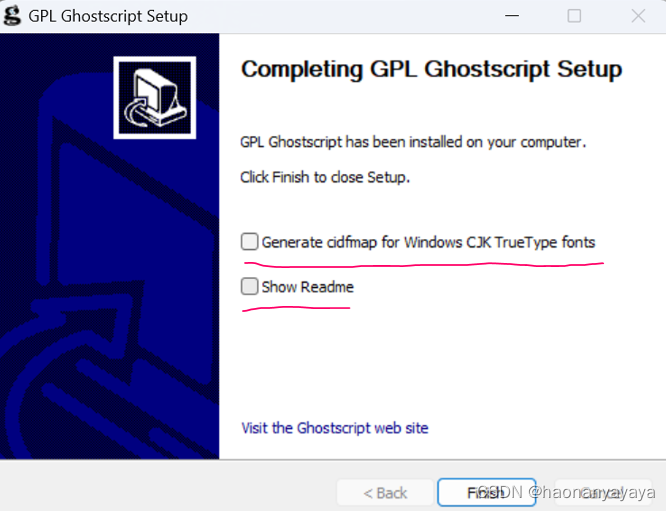

(8),将两个勾去掉,点击Finish

(9),返回Capture,点击被圈住的三个点

(10),找到刚刚的路径,选中uninstgs.exe,点击打开

(11),看下面红色字是不是变成了绿色字

注:有的人下载好后可能会多个WindSoul软件管家,这个可以直接卸载

(六)各类PCB网表

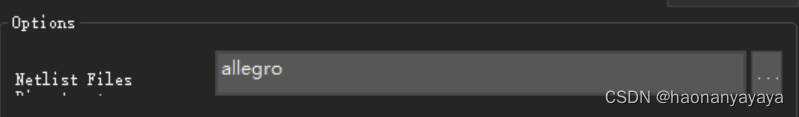

1,生成cadence allegro第一方网表

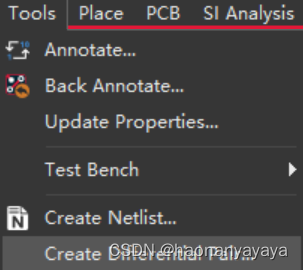

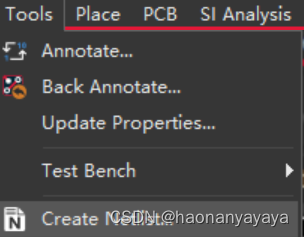

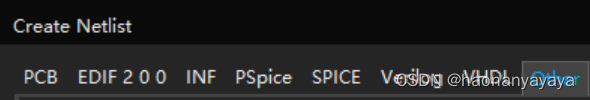

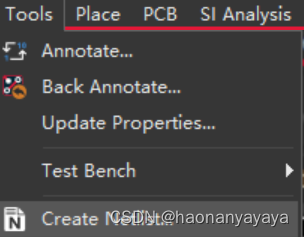

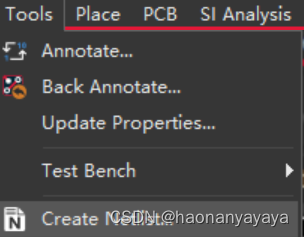

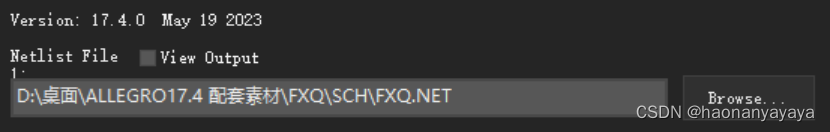

(1),点击Tools和Create Netlist

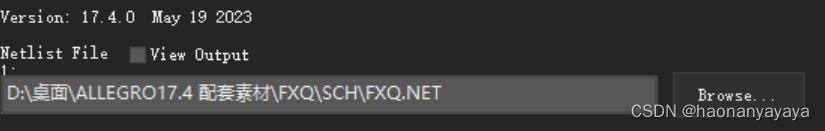

(2),选择输出路径(如果不选就生成在原理图当前路径下)

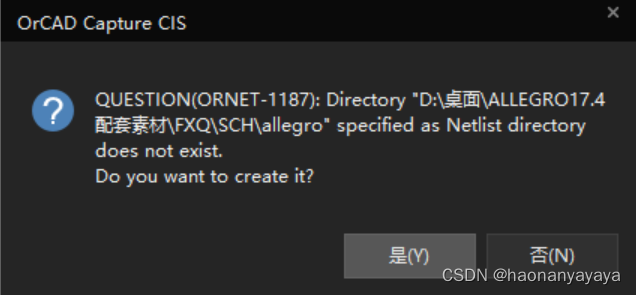

(3),点击确定

(4),询问是否创建一个名为allegro的文件夹存放,点击:是

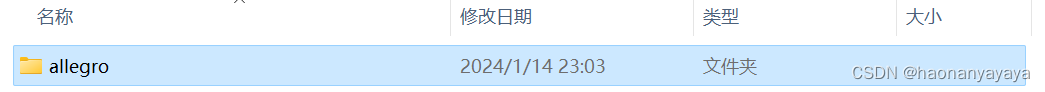

(5),打开设置的路径就会找到这个文件夹

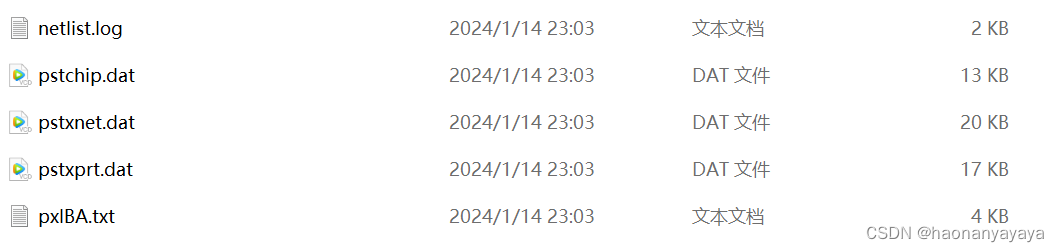

(6),这里面三个.dat文件就是网表,log和txt文件是配置文件

2,生成cadence allegro第三方网表

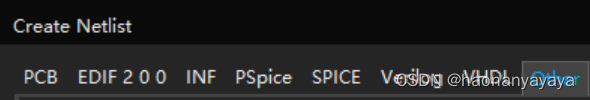

(1),点击Tools和Create Netlist

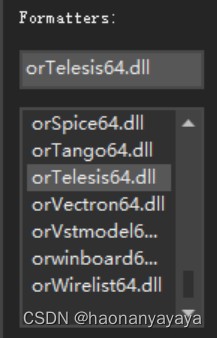

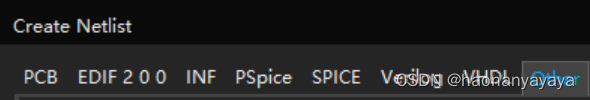

(2),点击Other

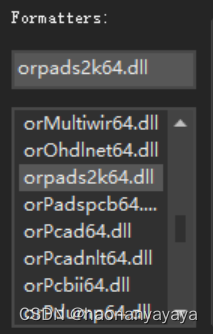

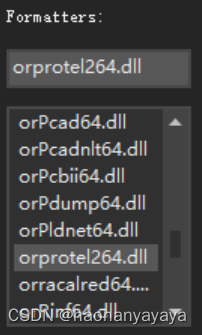

(3),将Formatters改为orTelesis64.dll

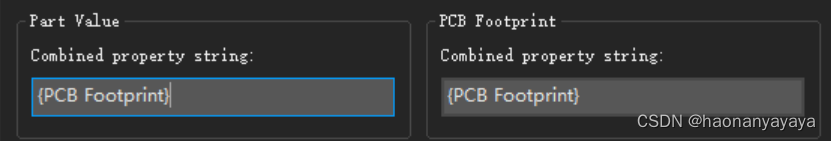

(4),修改名称,使用封装名替代

由于第三方网表导入到cadence allegro时无法识别小数点,井号,括号等字符,所以一般在导出第三方网表Value值一般使用封装名替代(把右边复制过来 )

注意:后面的PADS是可以识别的,所以创建PADS文件不需要这一步

(5),修改产生NET文件路径

(6),点击确定

(7),打开NET文件路径即可看到生成的文件

![]()

3,生成PADS文件

(1),点击Tools和Create Netlist

(2),点击Other

(3),将Formatters改为orpads2k64.dll

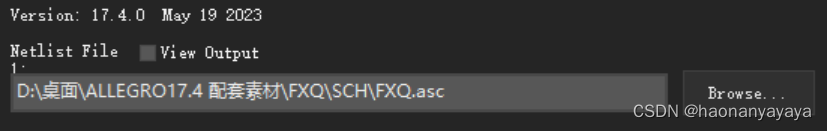

(4),修改产生asc文件路径

(5),点击确定

(6),打开asc文件路径即可看到生成的文件

![]()

4,生成AD文件

(1),点击Tools和Create Netlist

(2),点击Other

(3),将Formatters改为orprotel264.dll

(4),修改产生NET文件路径(这个生成的文件名后缀是和第三方网表一样的)

(5),点击确定

(6),打开文件路径即可看到生成的文件

![]()

5,常见错误解析

ERROR(ORNET-1193)

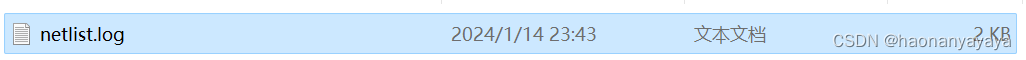

这个是创建失败,解决方法为找到netlist.log文件,原理图中存在的错误在这有详细的描述,这个文件一般存储于输出网表的文件夹下,用写字本文件打开此文件,将列表中所列的错误一一解决掉,即可输出网表文件

打开当前原理图存在的路径,里面有个allegro文件夹,打开后就会看见netlist.log文件,使用写字板打开就可以看见错误

注意:报的几个错误并不是只有几个错误,而是这个解决以后再报下一个错误

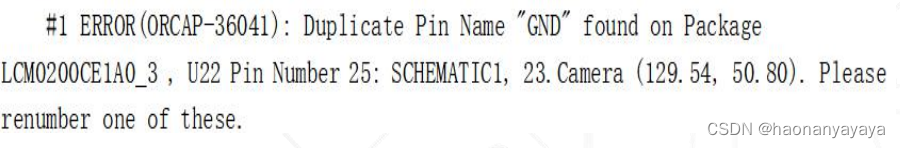

(1)重复网络名称

解决方法:将重复的名称改成不一样的,例如GND1,GND2

如果是电源管脚就将管脚设置为power类型

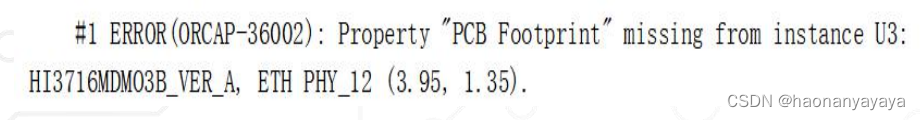

(2)封装名缺失

就算没有做PCB封装,在PCB Footprint这一栏名称也要填写

(3)管脚编号缺失

例如引脚为1,2,3,4,5,6,7,8,9,10,这个编号不能缺失

(4)属性名称中含有回车键

这里错误器件是U11,选择U11再选中属性(PCB Footprint)按删除,把回车键删除就行

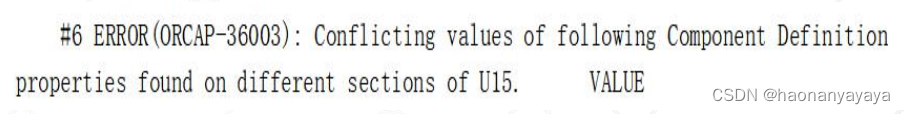

(5)多Part器件属性冲突

假设U1是四部分,分为APart,BPart,CPart,DPart,这四个Part属于同一器件,那么属性应该相同,只是管脚不同,同一个Part的Value值,封装名,来源路径等不同会导致这个冲突

解决方法:同一器件的属性改为一致

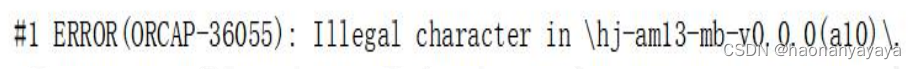

(6)非法字符

解决方法:重新创建一个库,放在没有非法字符的路径里,替换缓存就好

本文详细介绍了使用CadenceAllegro17.4进行PCB布局设计的基础步骤,包括创建文件、设计图管理、原理图修改、元器件连接、DRC规则检查、PDF和BOM清单输出,以及常见错误处理。

本文详细介绍了使用CadenceAllegro17.4进行PCB布局设计的基础步骤,包括创建文件、设计图管理、原理图修改、元器件连接、DRC规则检查、PDF和BOM清单输出,以及常见错误处理。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?