一,原理图部分

(1)路径设置

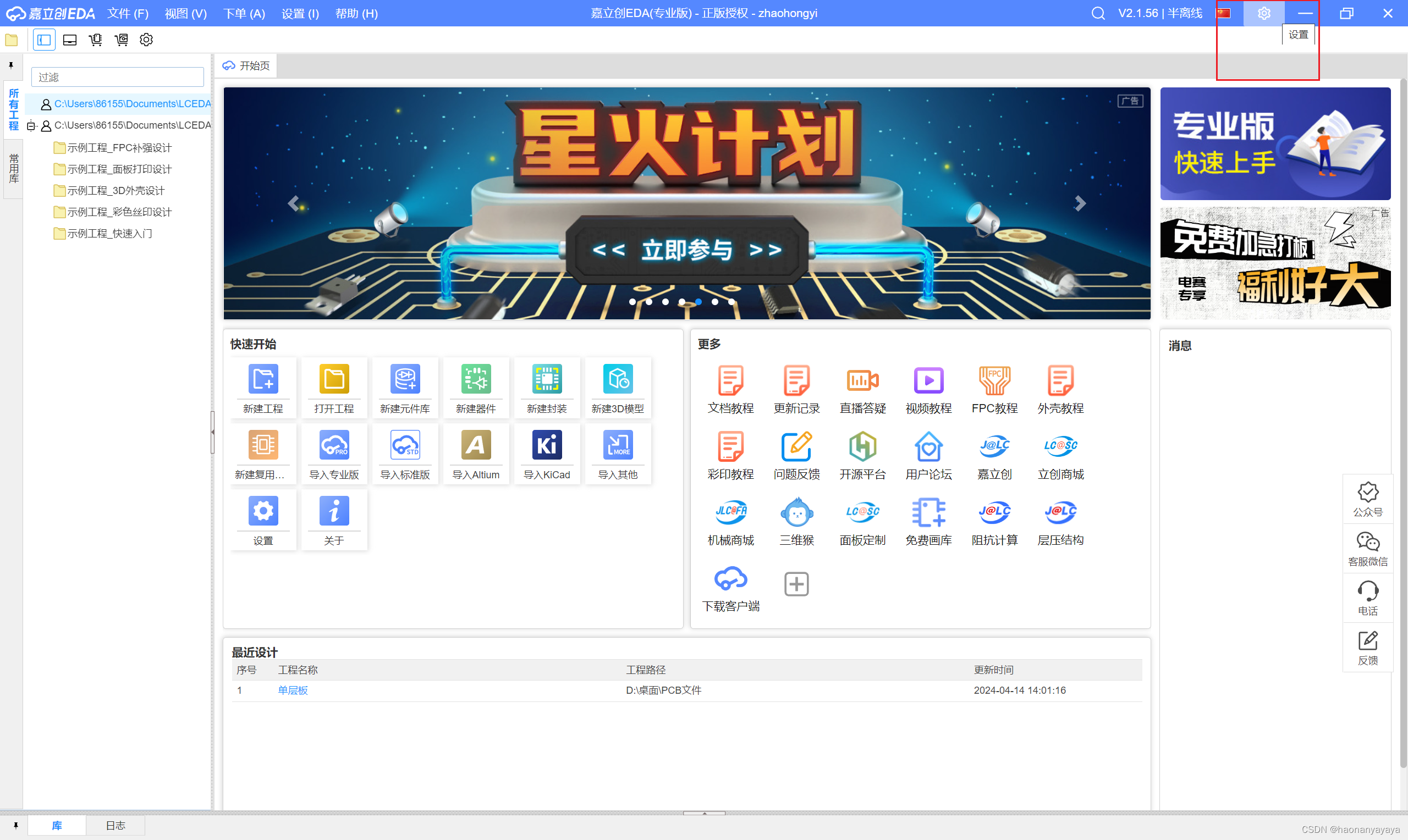

打开嘉立创以后,在右上角点击设置

可以看到下图

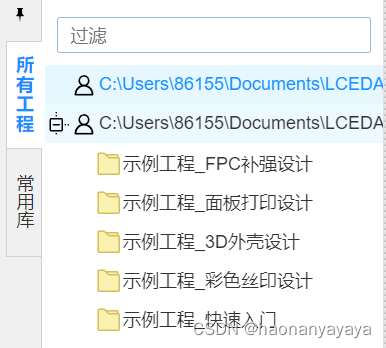

左边栏所有工程为工程路径,常用库为库路径

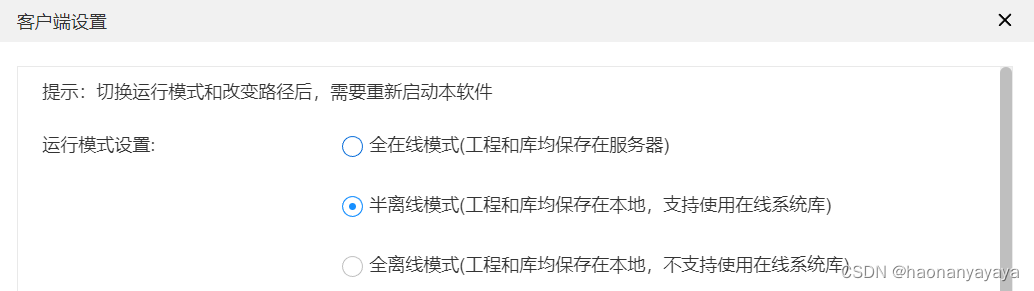

(2)模式设置

同样点击设置,可以看到下面界面

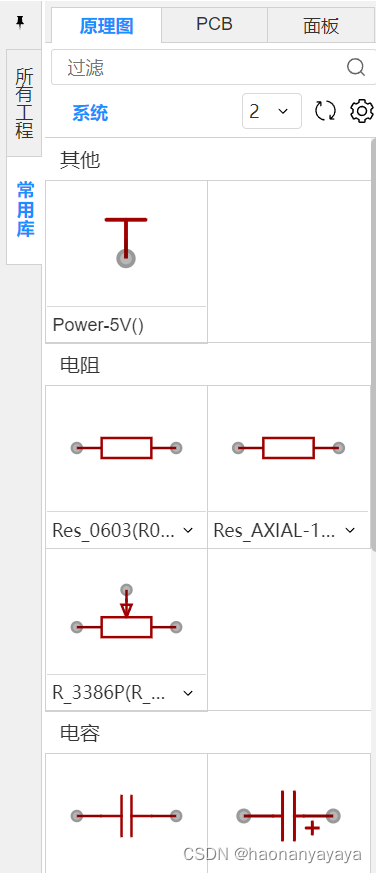

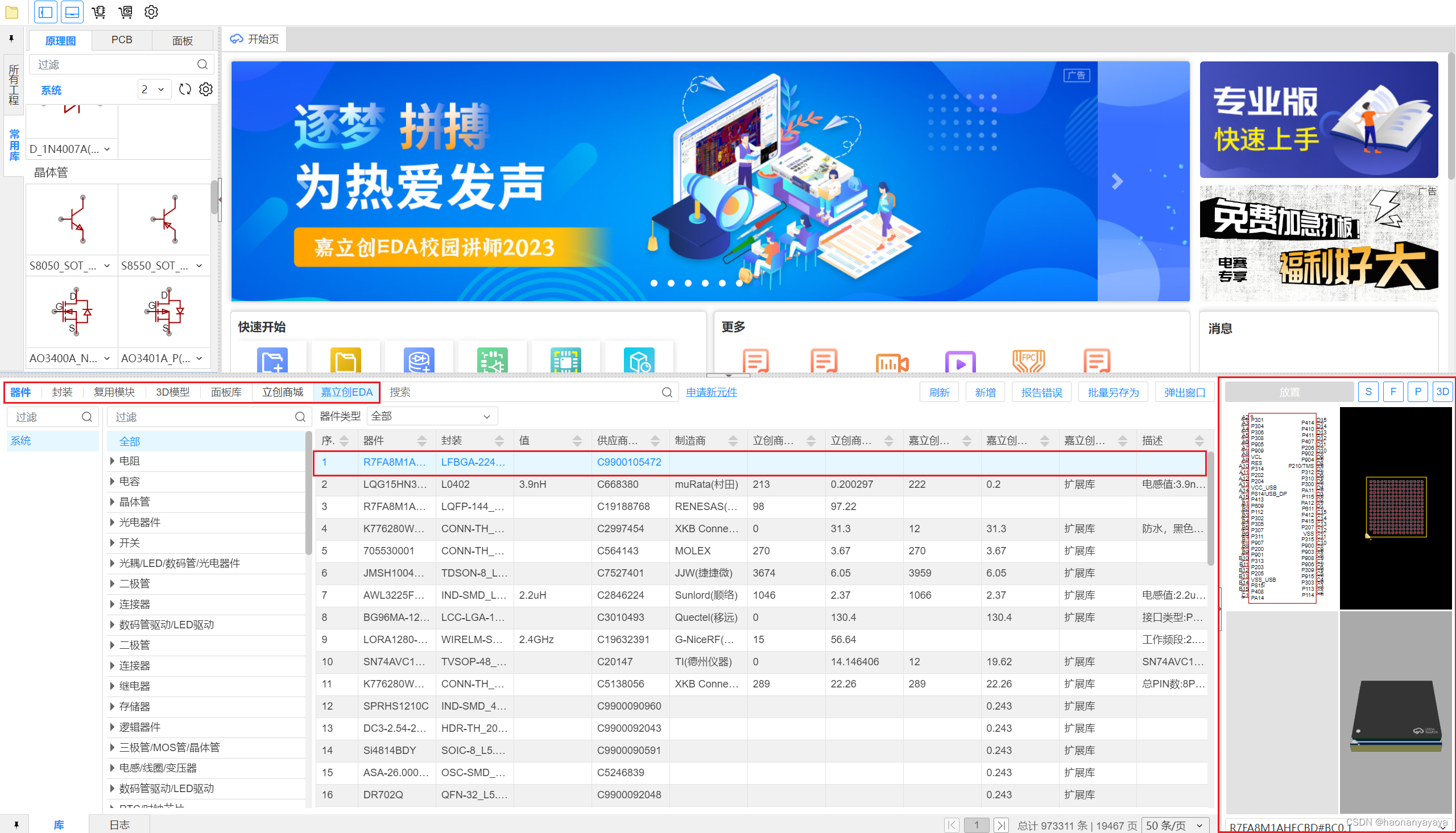

下图为在线系统库,这些封装,符号全都可以直接用

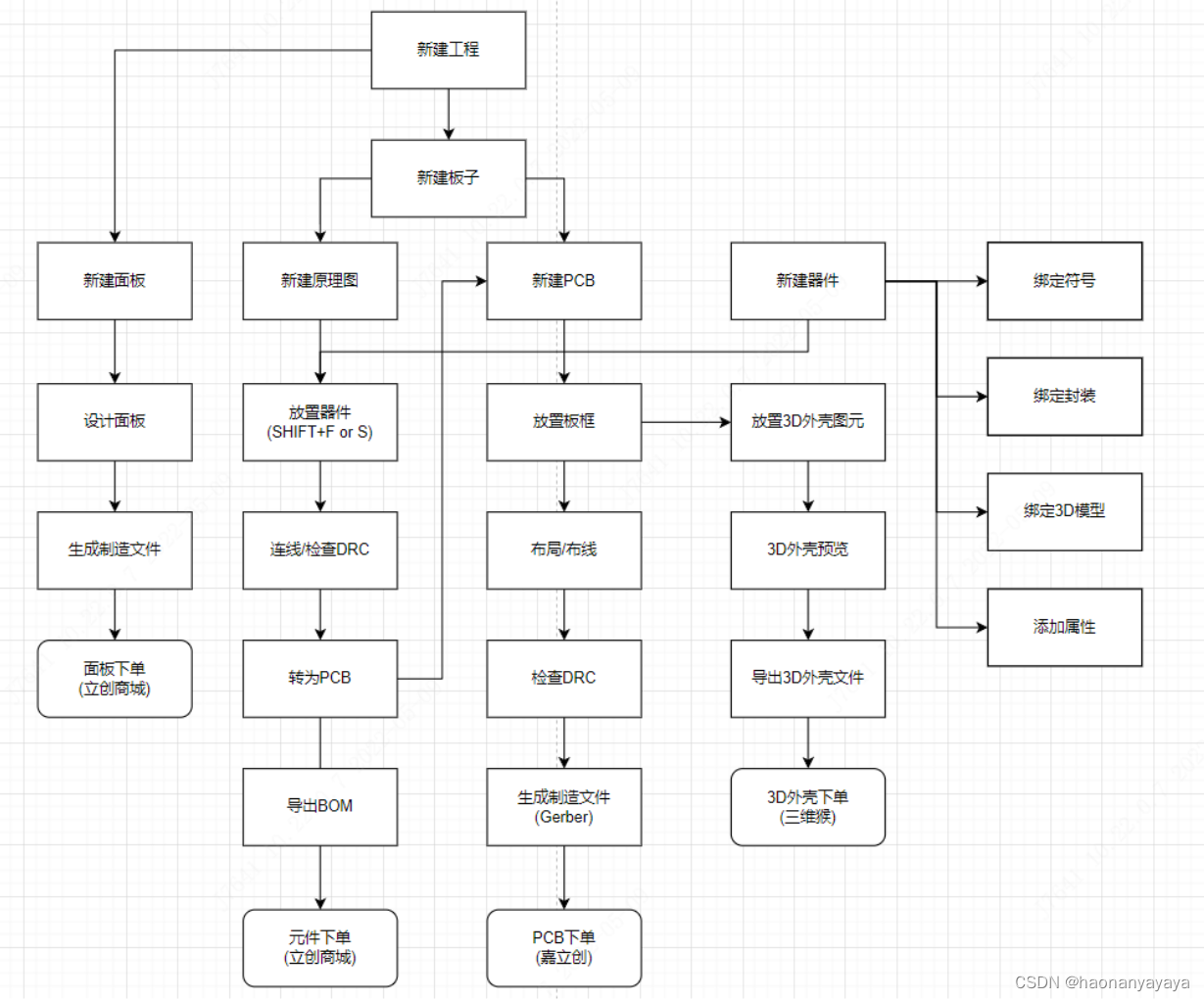

(3)设计流程

总结:先建立符号库,有了符号才能绘制原理图,有了原理图才能画PCB

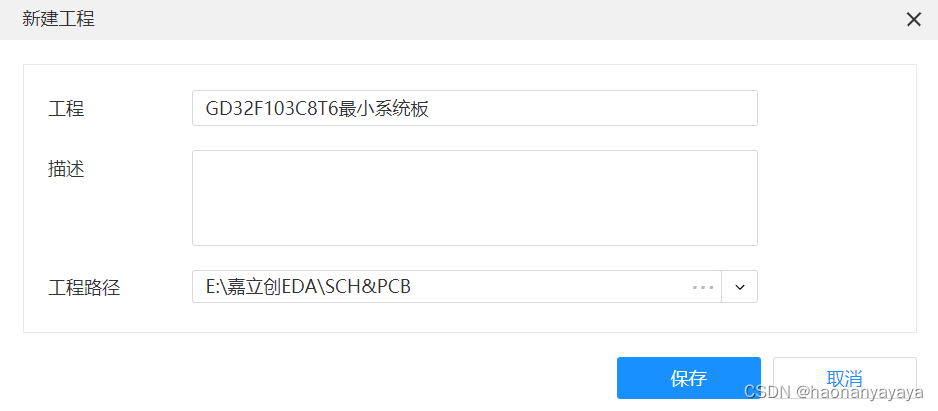

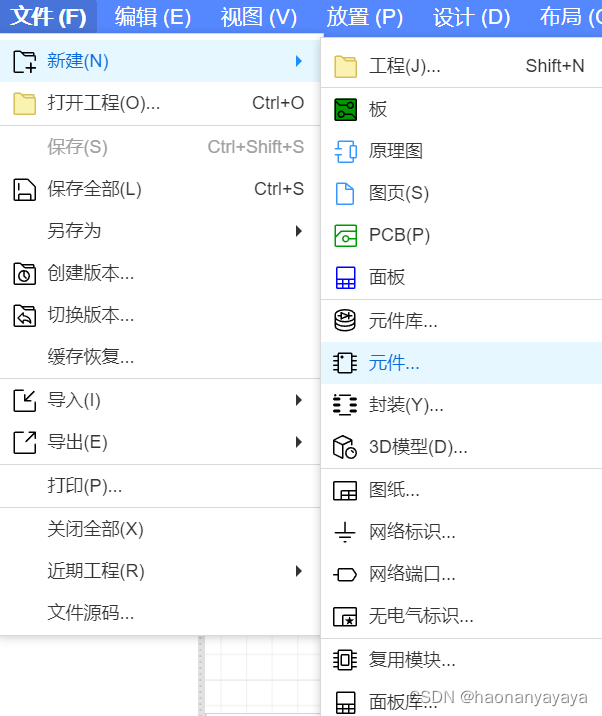

(4)新建工程

1,在嘉立创软件左上角找到文件,点击新建和工程

2,输入工程名和放置路径后点击保存

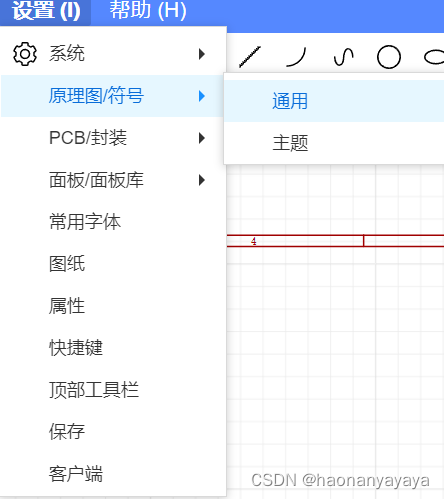

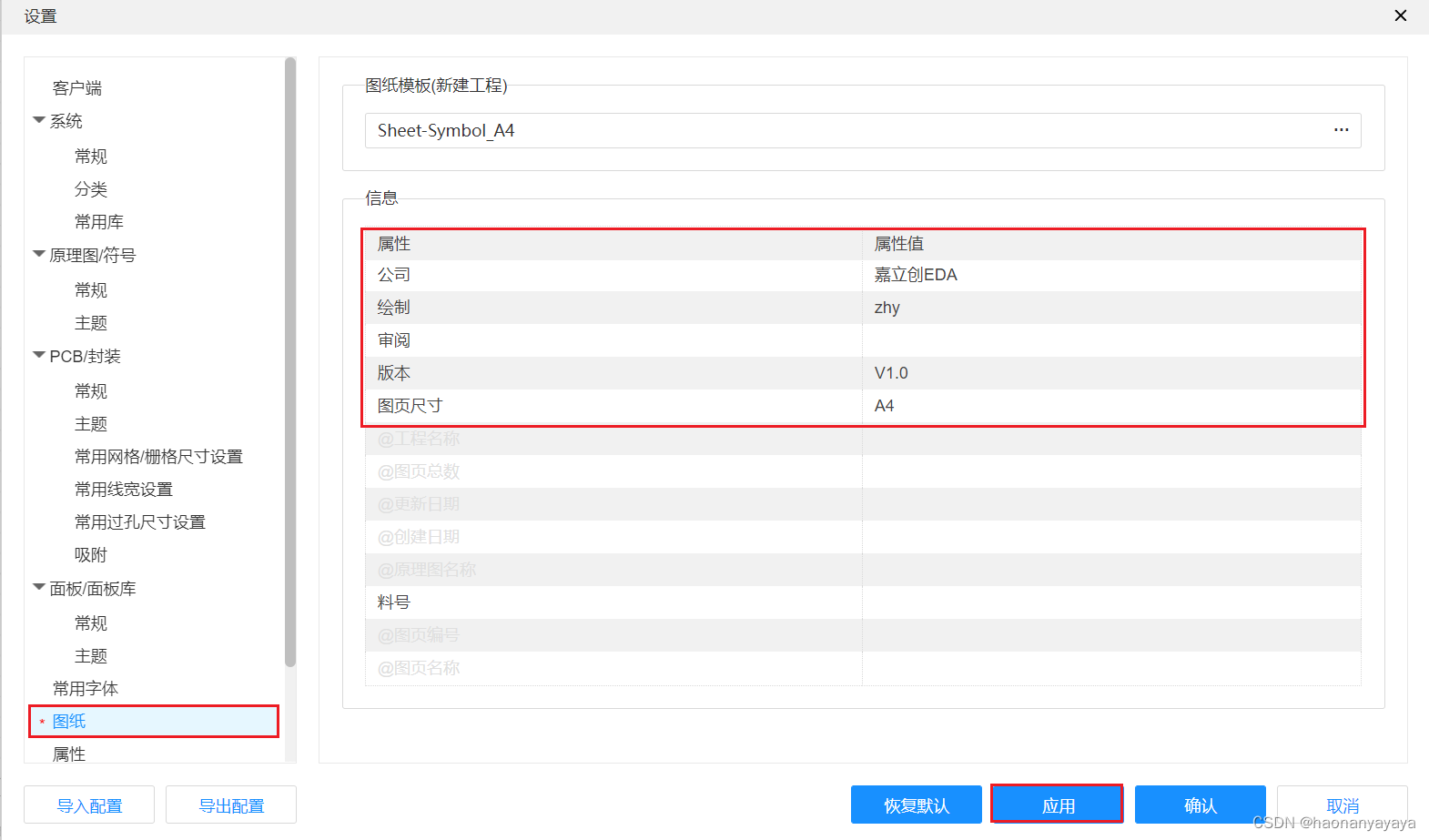

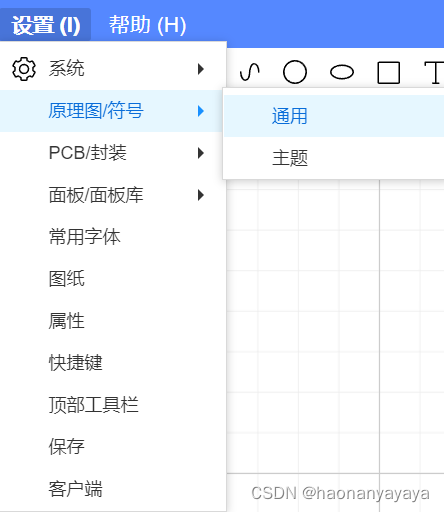

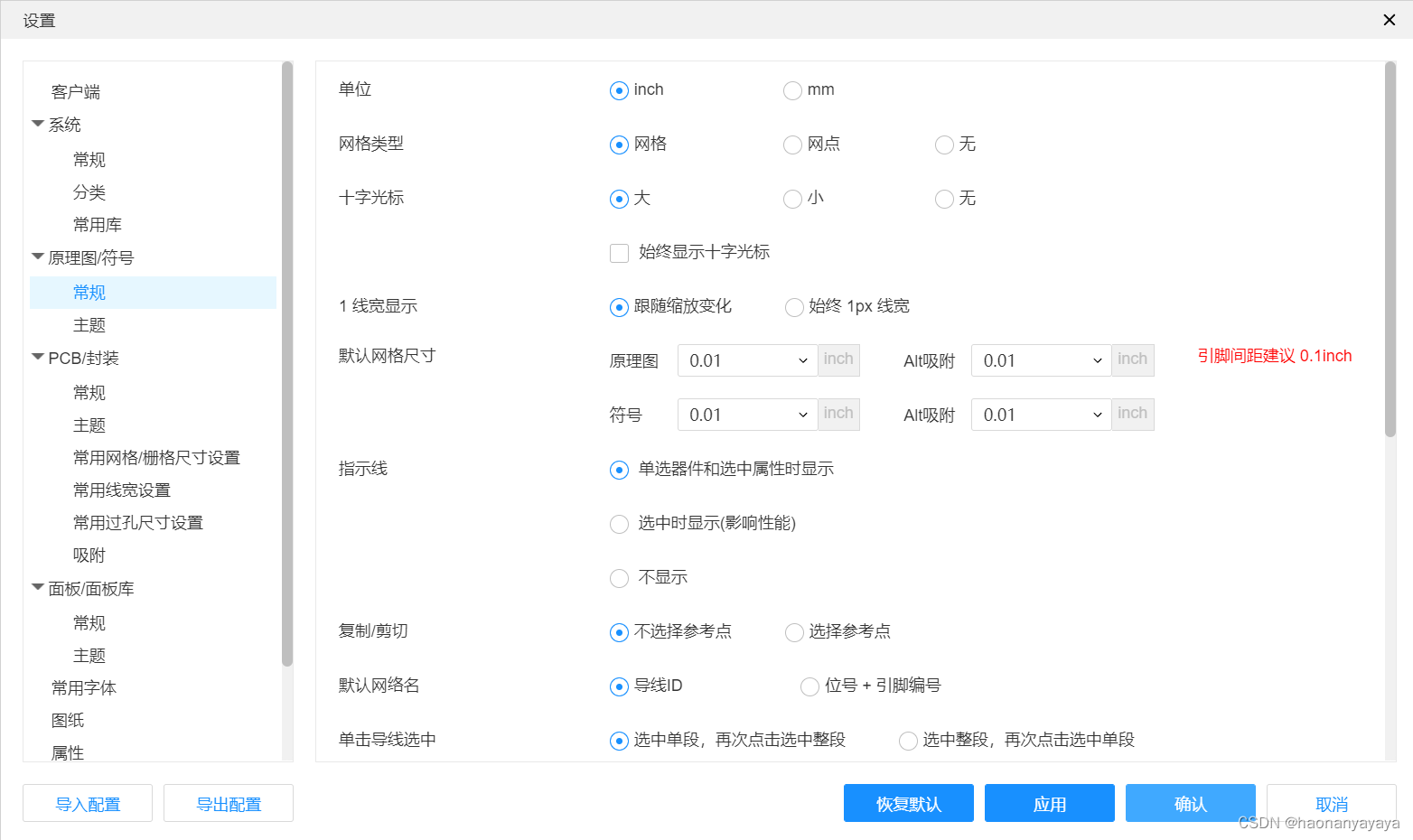

3,点击设置,原理图/符号,通用

4,点击图纸,修改信息后点击应用

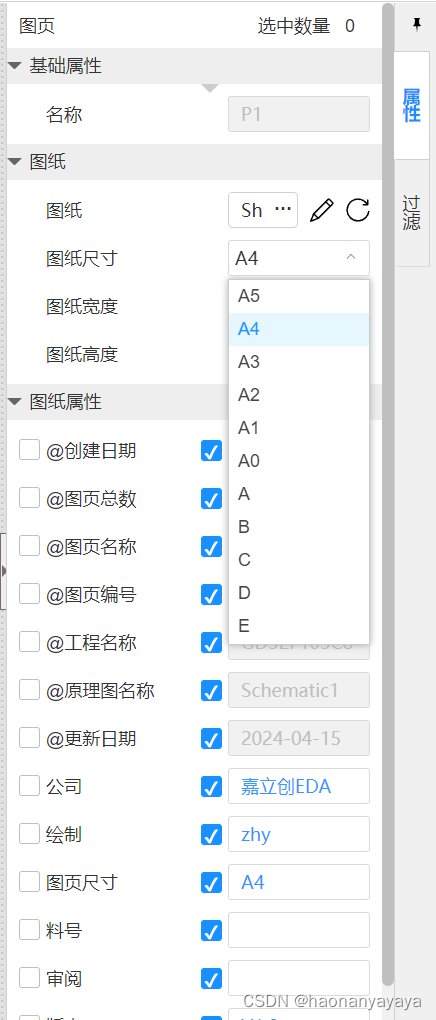

5,在右边栏修改信息

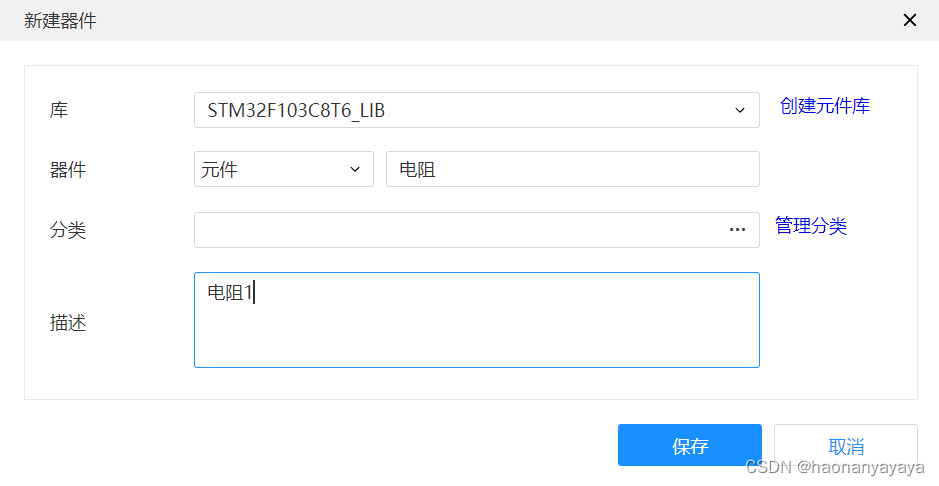

(5)新建原件库

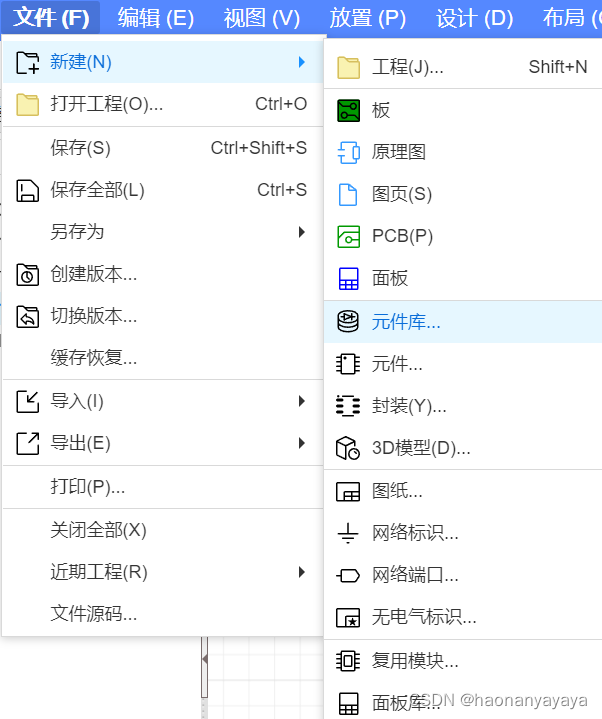

1,点击文件,新建,元件库

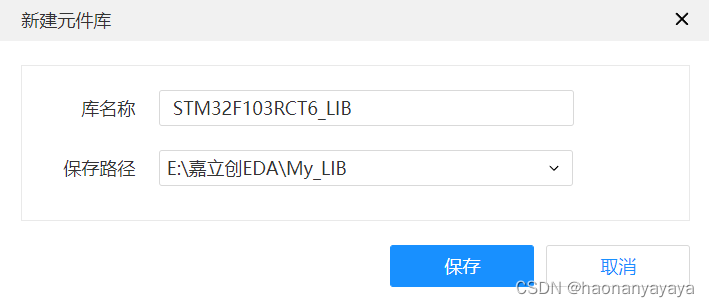

2,选择新建元件库后保存

3,新建元件

4,设置信息

5,打开设置

6,选择要修改的信息

7,选择要绘制的元件形状

![]()

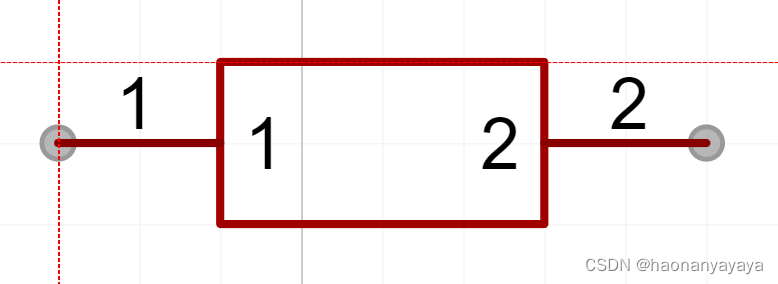

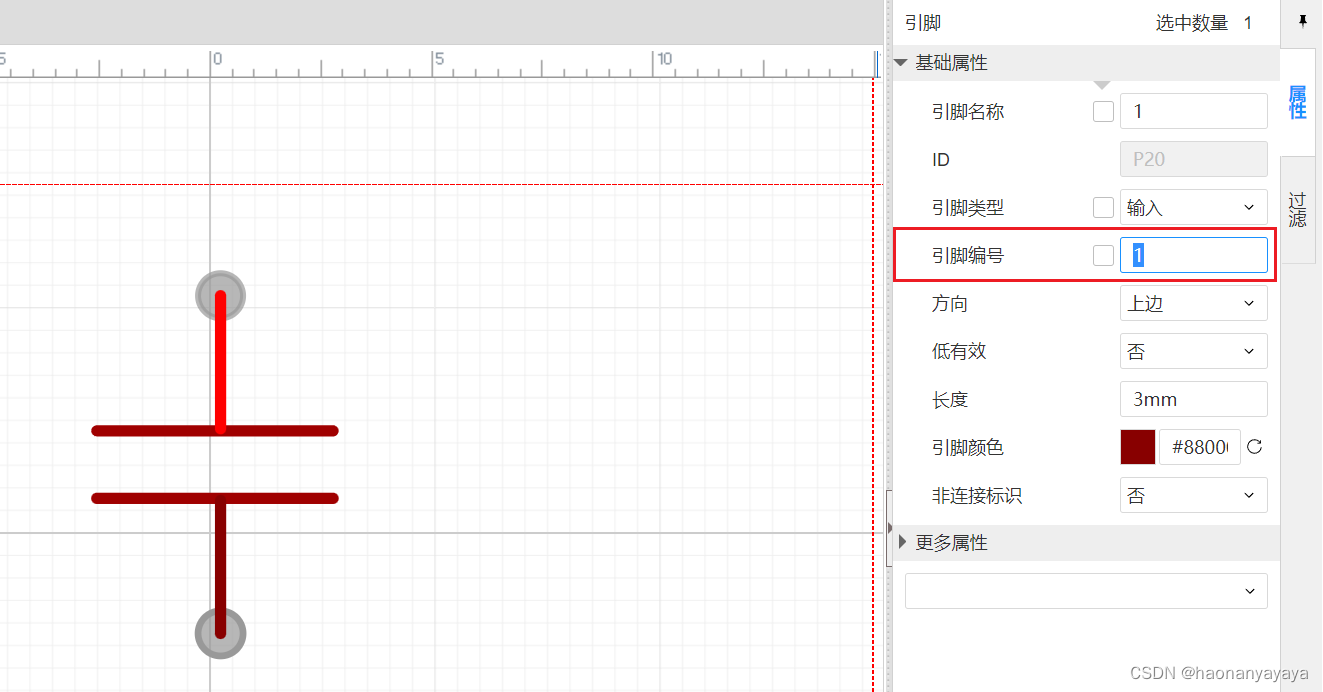

8,绘制元件

如果不想要移动到格子线上,可以先放置,再点击线,按住Alt移动

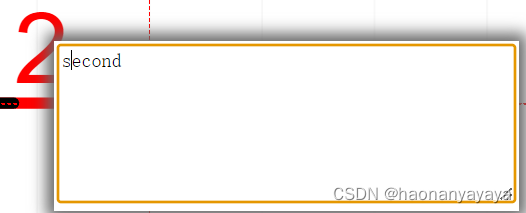

9,双击数字,修改名称

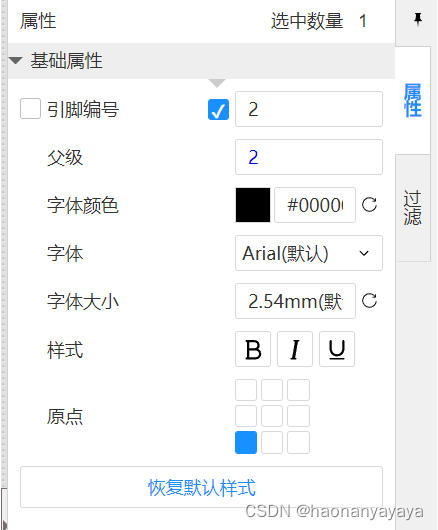

也可以选中以后修改右边栏的属性

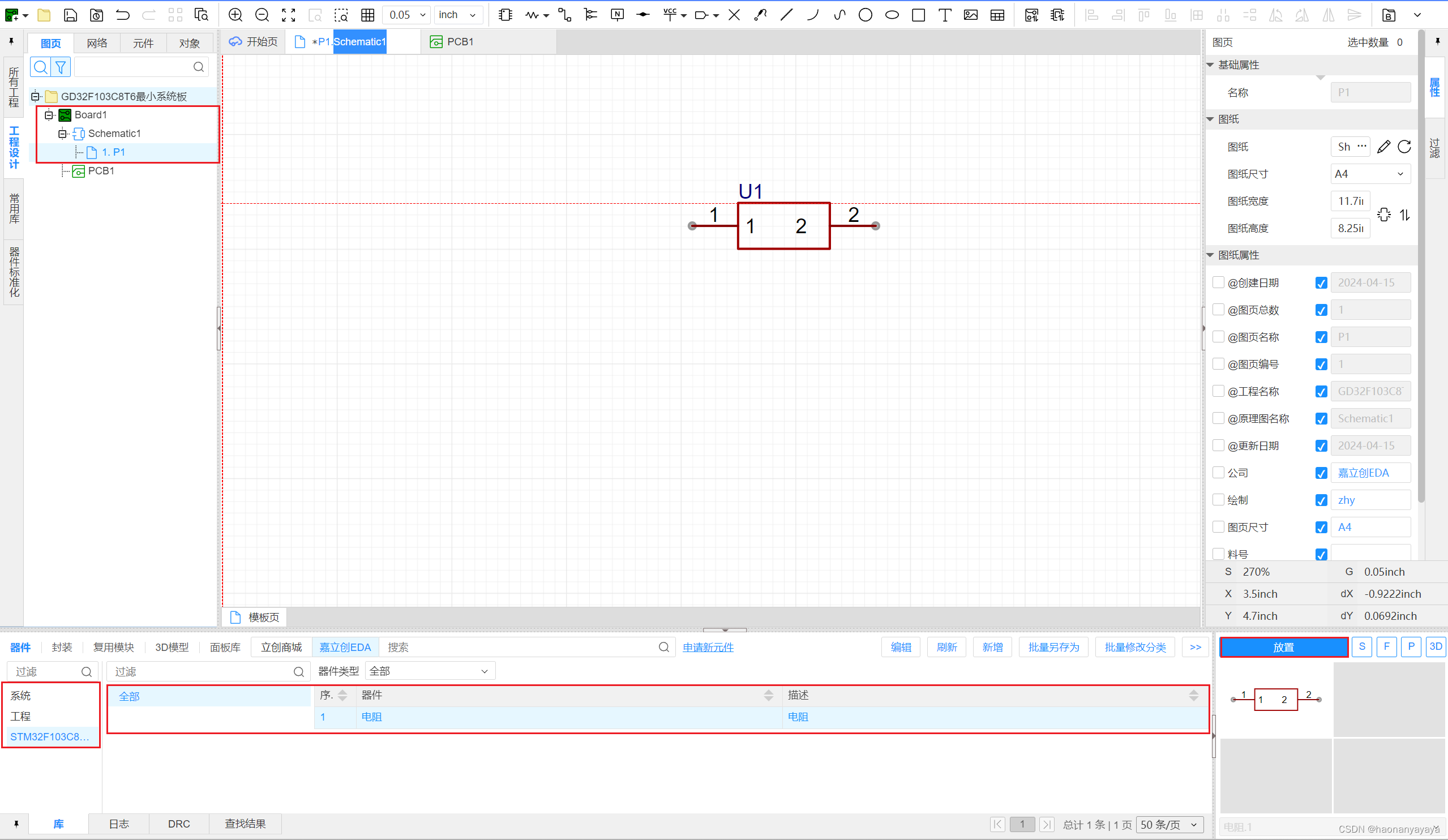

10,返回原理图,点击左下角器件,选中刚刚创建的器件,再点击放置

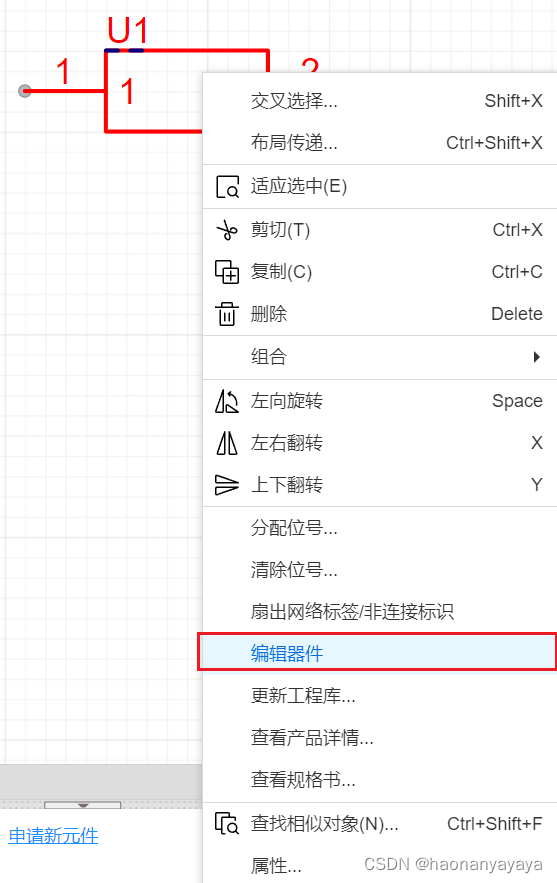

另:如果元件多了,可以选中元件后点击编辑器件

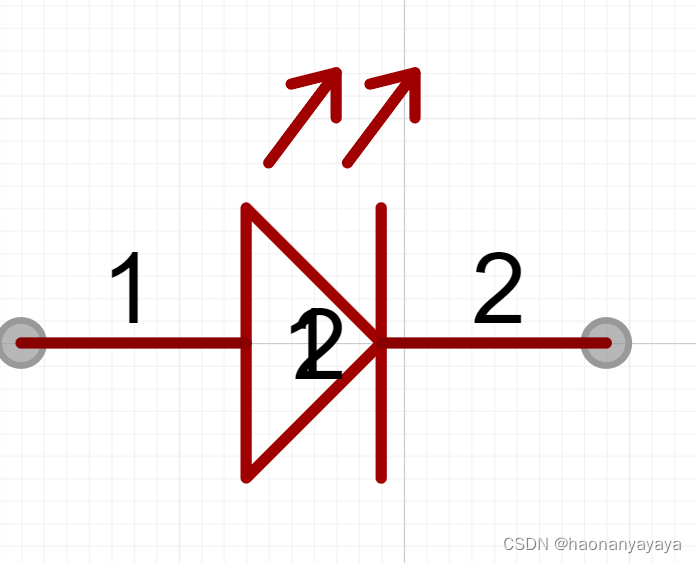

各位可以尝试绘制一个LED

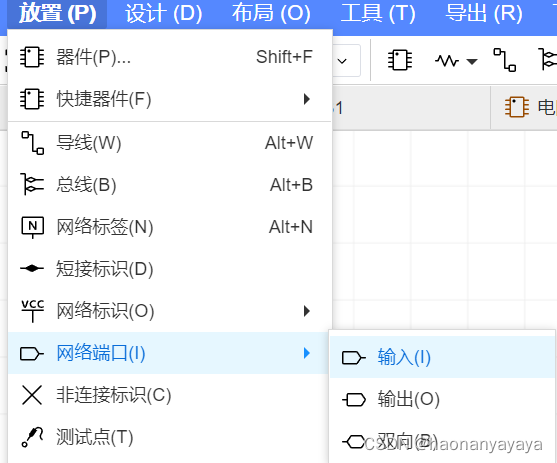

11,放置网络标识

12,放置网络短号

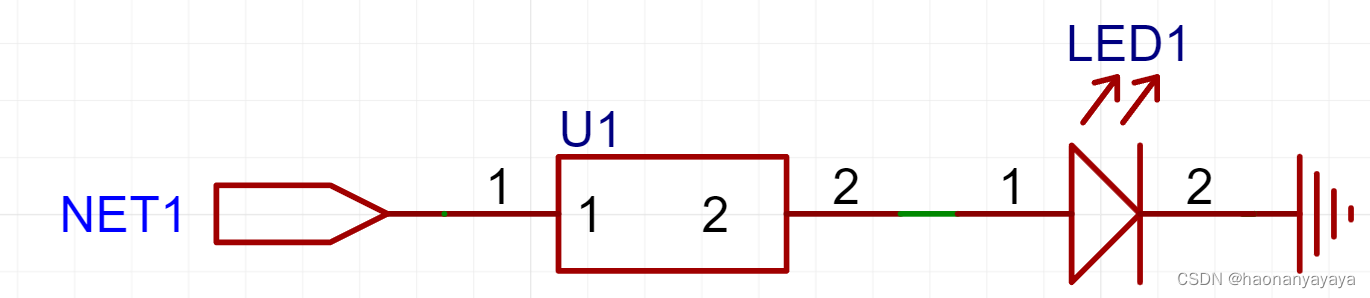

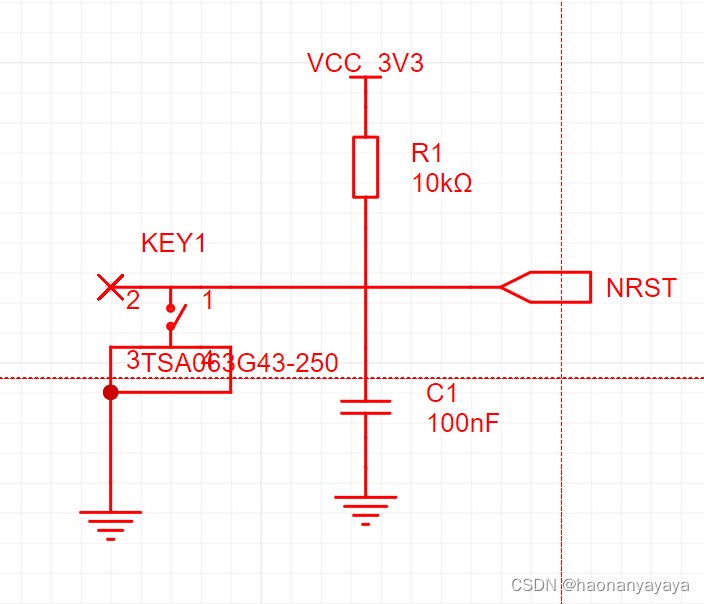

练习:尝试绘制以下图形

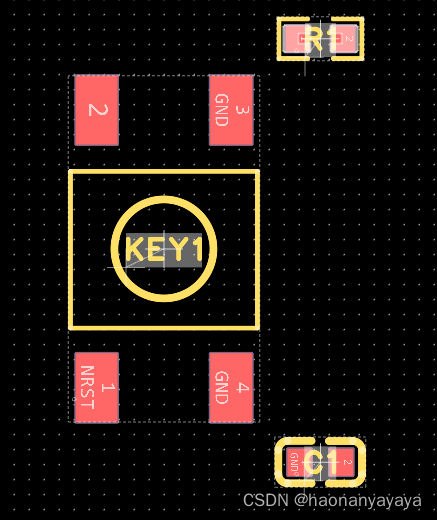

(6)绘制封装

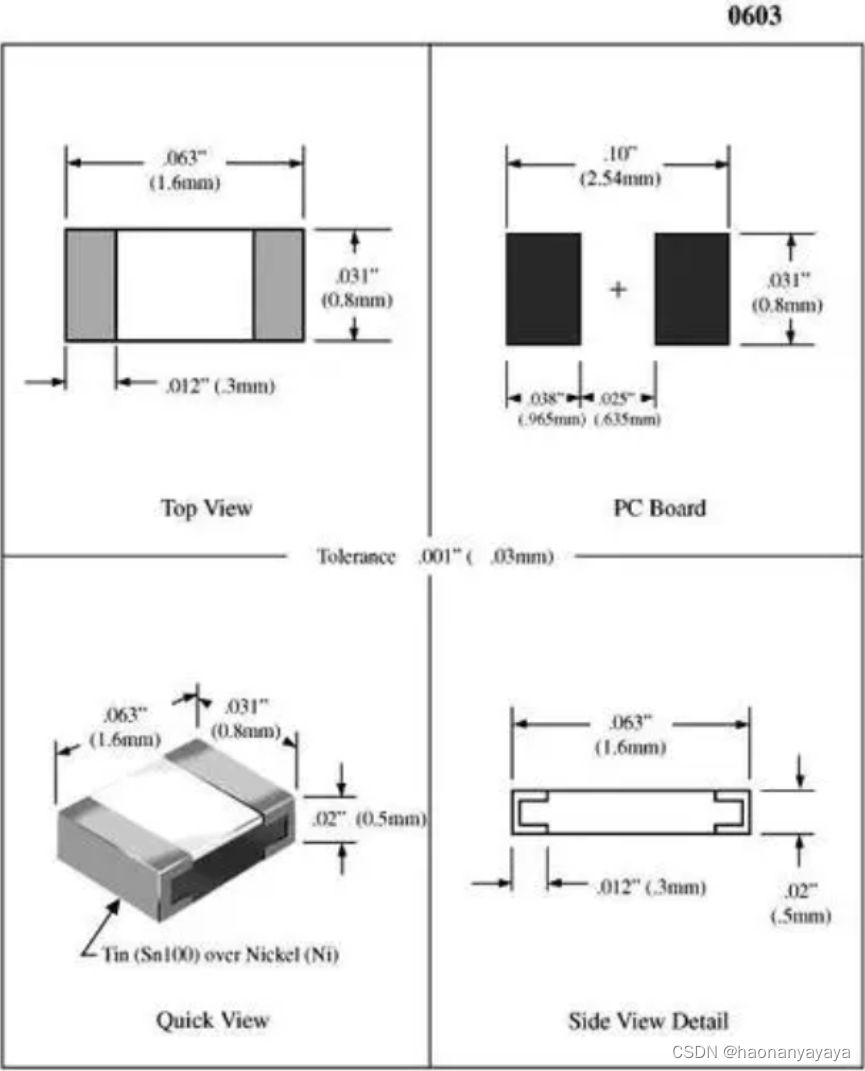

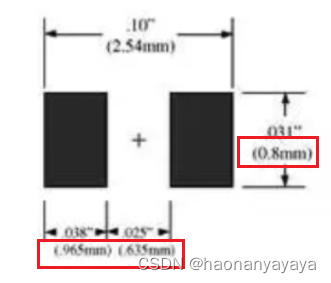

假设我要创建一个电容0603的封装

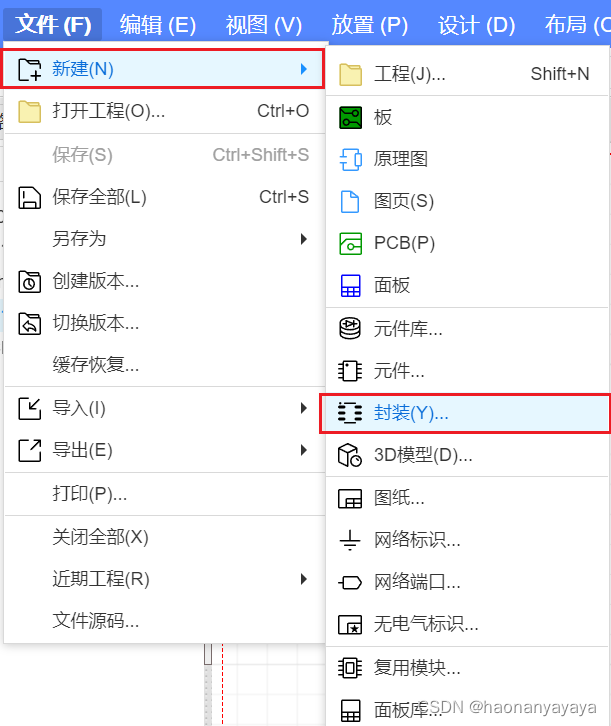

1,先点击文件,新建,封装

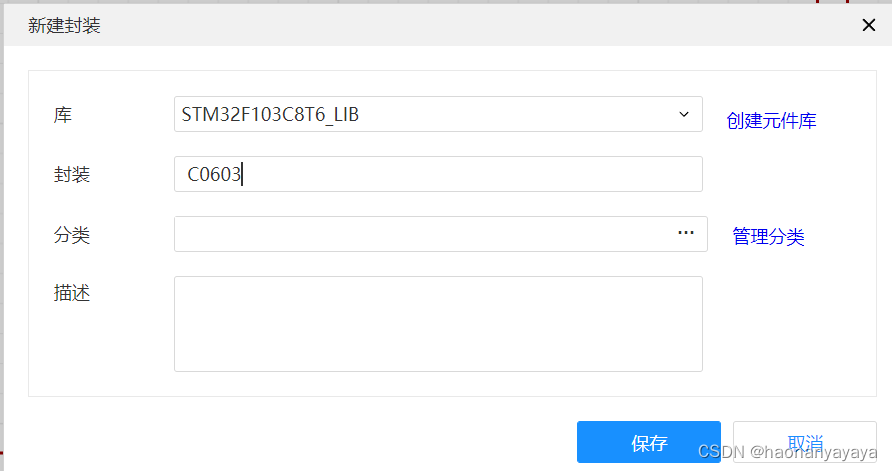

2,修改封装名称后改名

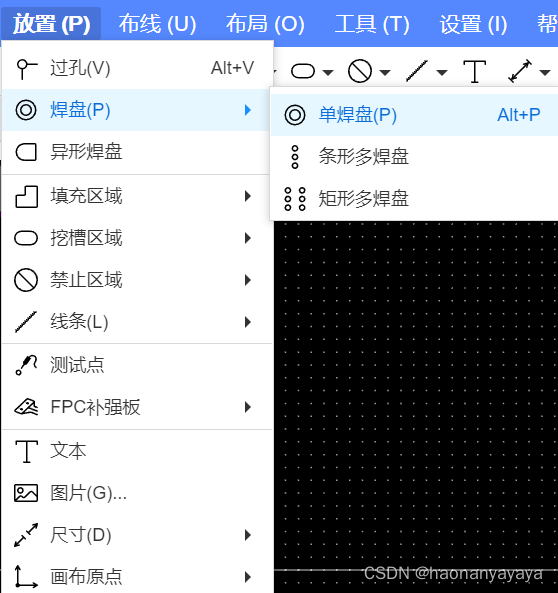

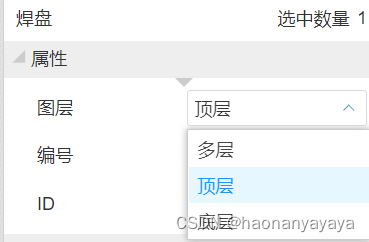

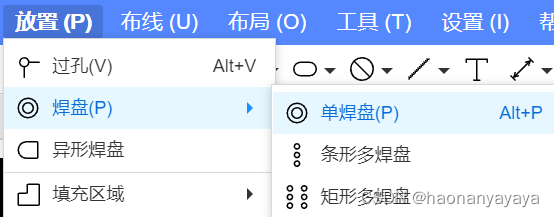

3,点击放置,焊盘,焊盘类型

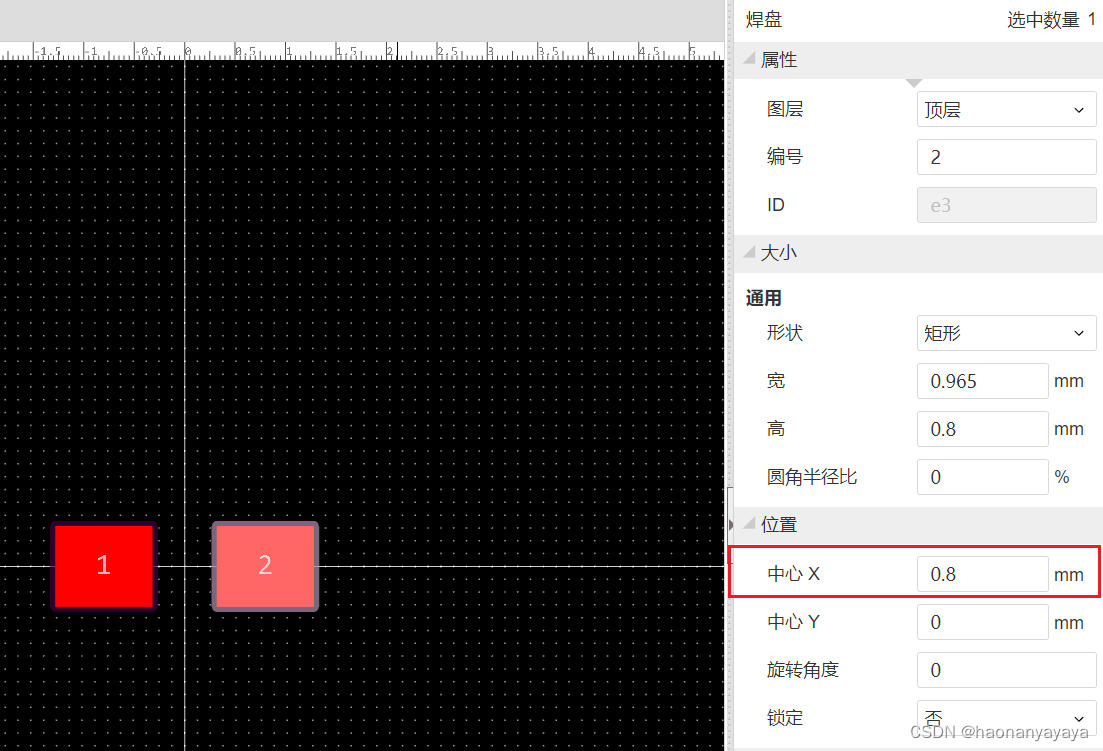

4,放置在图中后修改图层为顶层,只有单层有(因为绘制的是贴片电容)

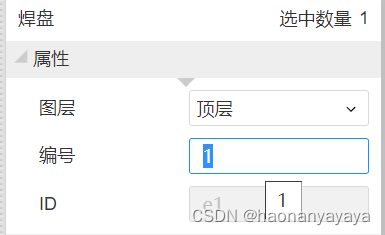

5,修改编号

这个编号是与元件的编号相对应的

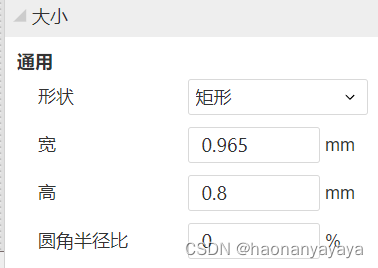

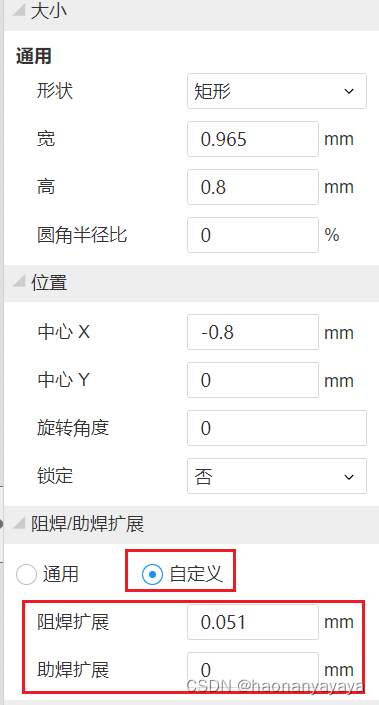

6,选择形状,宽和高

7,再次放置焊盘

8,设置放置位置

由焊盘宽度加间隔可得(0.965+0.635)/ 2 = 0.8mm

9,点击图层,选择顶层丝印层

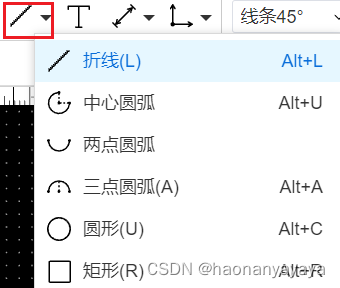

10,点击折线

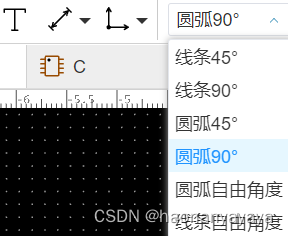

11,设置线形状

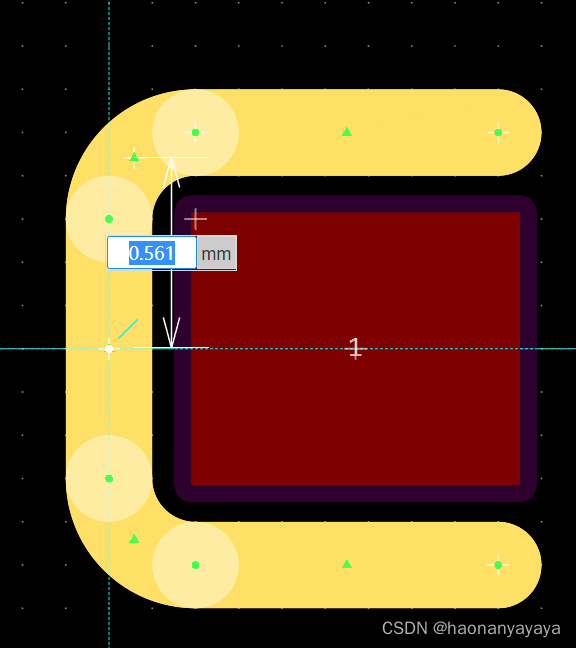

12,绘制

13,修改线宽

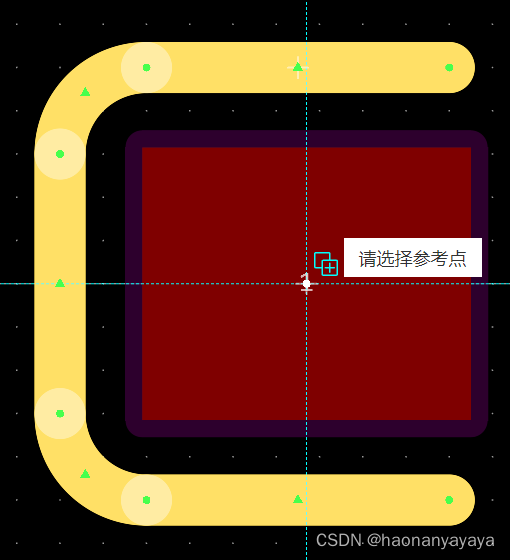

14,选中后点击Ctrl+C,后选择参考点

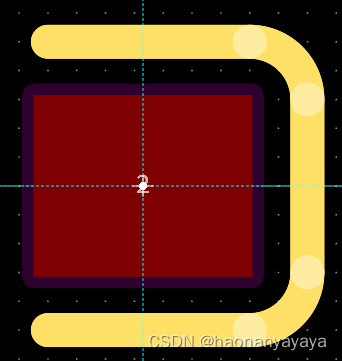

15,点击Ctrl+V(如果方向不对按空格)粘贴

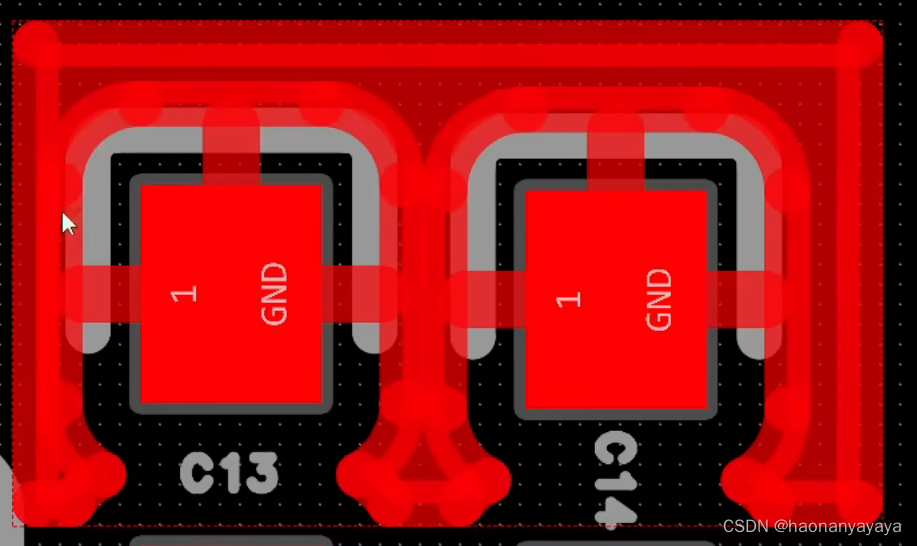

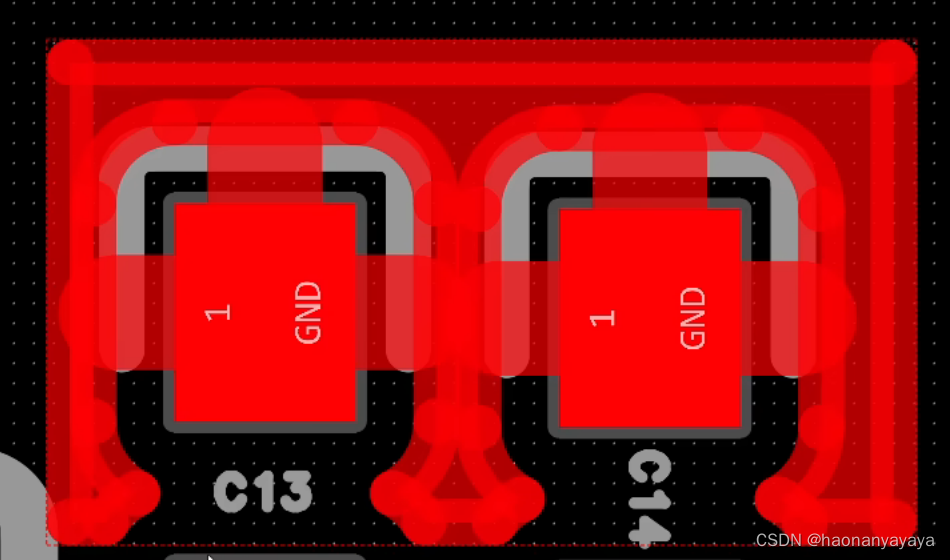

16,点击图层,选择顶层阻焊层

17,可以看到元件是一圈紫色,这一圈是不加绿油

18,如果想要修改就先点击元件,在右边栏设置。(默认就可以)

(7)封装使用

1,返回原理图

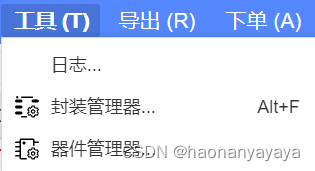

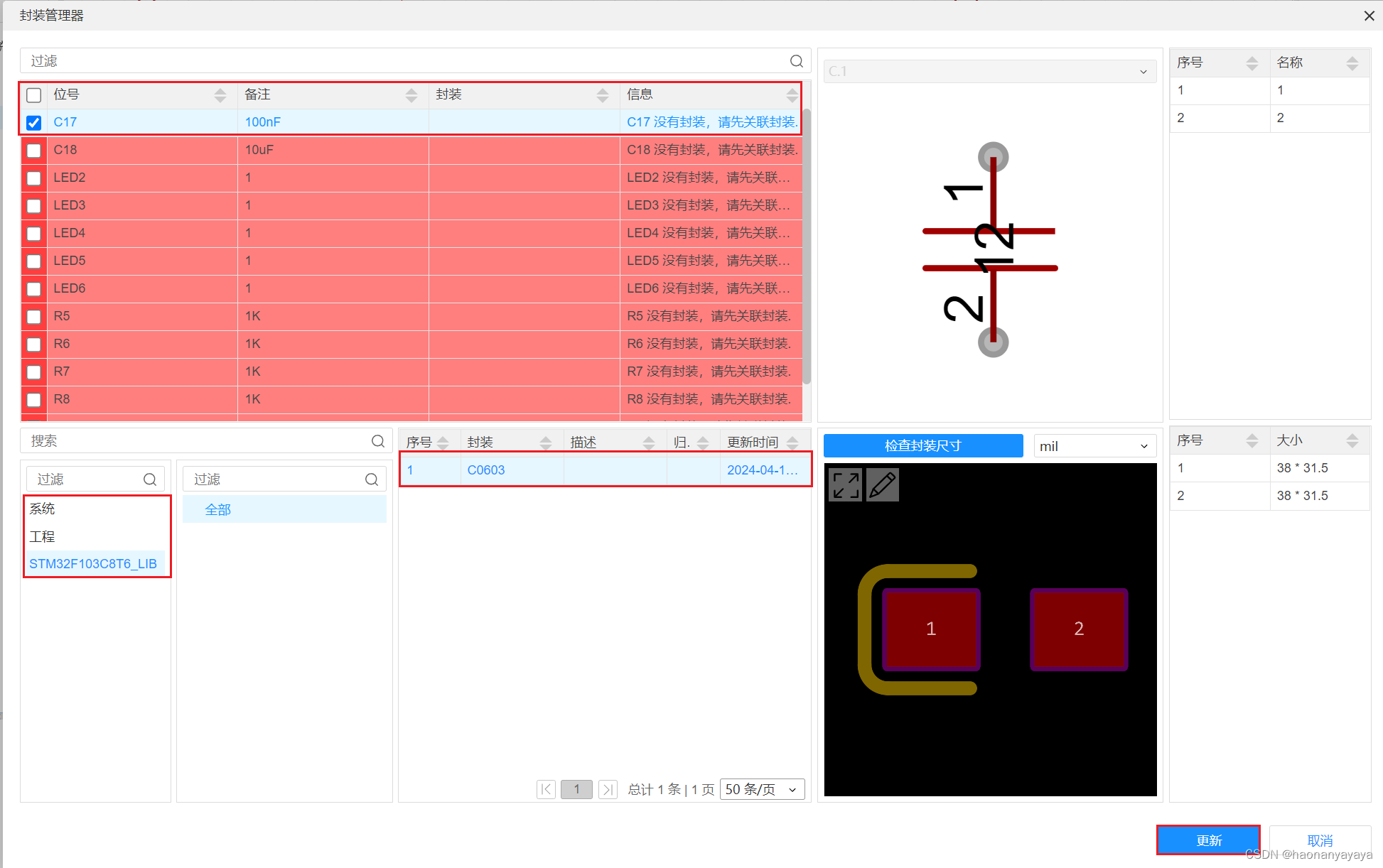

2,点击工具,选择封装管理器

3,选择要使用此封装的元件,选择库,自己绘制的封装,点击更新

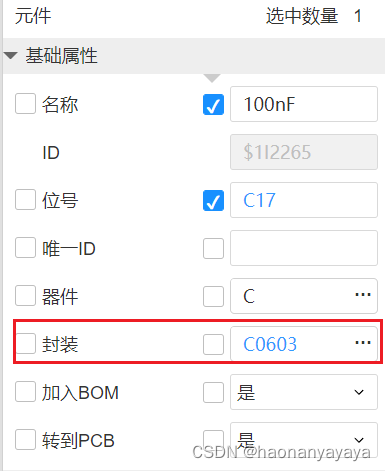

4,这时候再看就可以看见选中的元件使用了这个封装

5,再点击该元件即可看见此封装

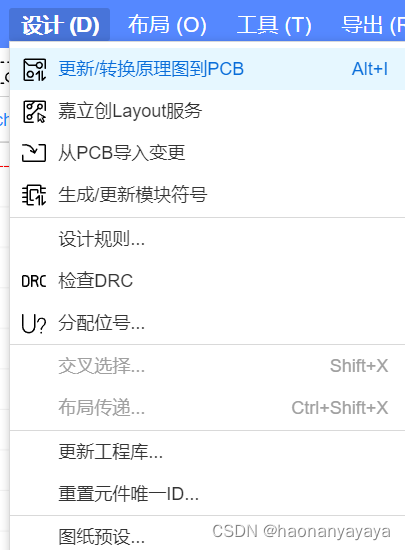

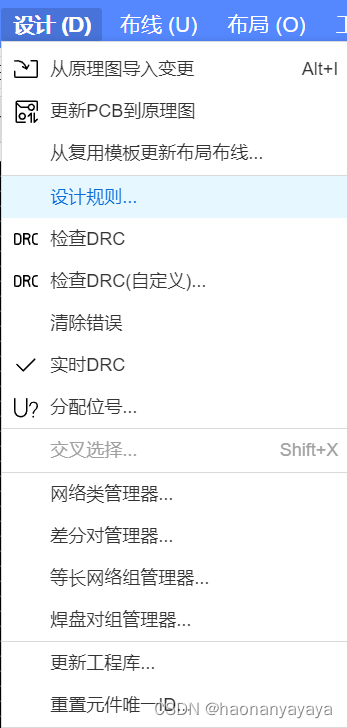

(8)DRC检查

点击设计,检查DRC,这一步可以检查出原理图中出现的错误

如果想要看DRC能检查哪些错误,点击设计,设计规则即可查看

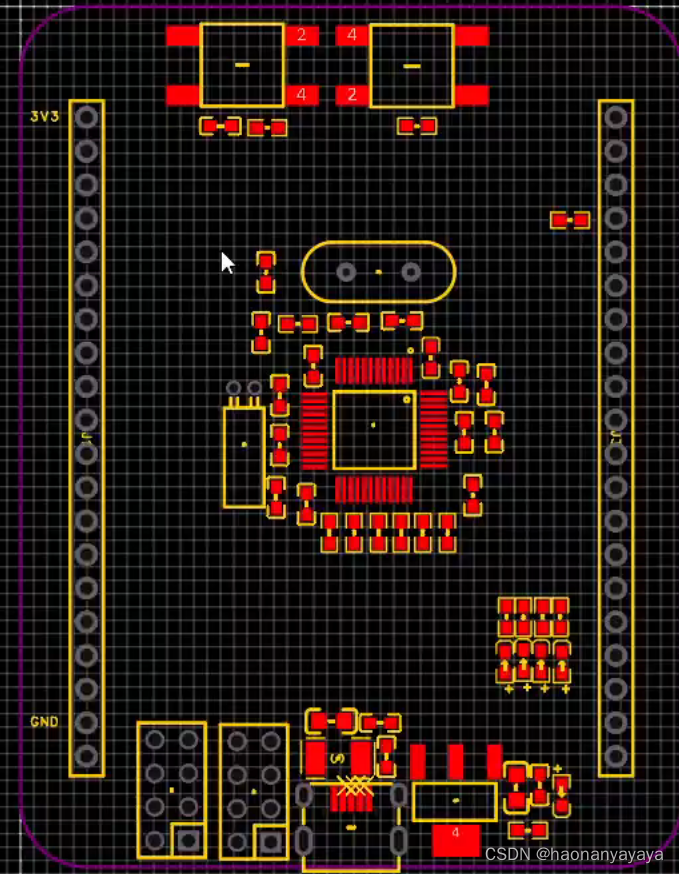

(二)PCB部分

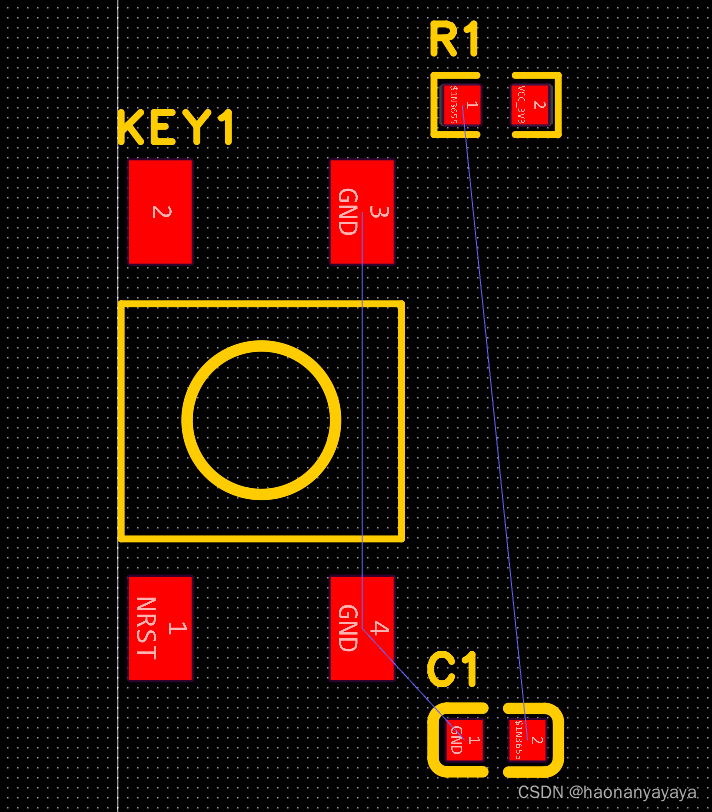

(1)原理图导出

导出完成后,可以看到细线,这些细线就是连接的部分

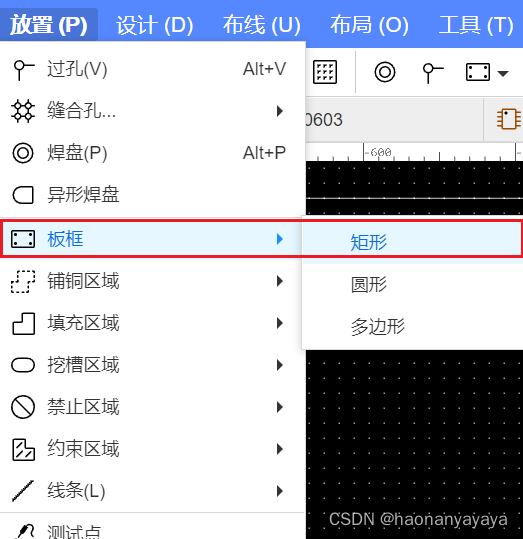

(2)绘制板框

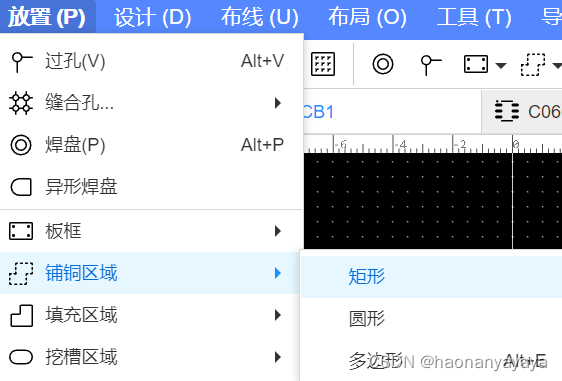

点击放置,板框,形状

如果想要切换单位为mm,就按快捷键Q

绘制板框后在右边栏切换大小

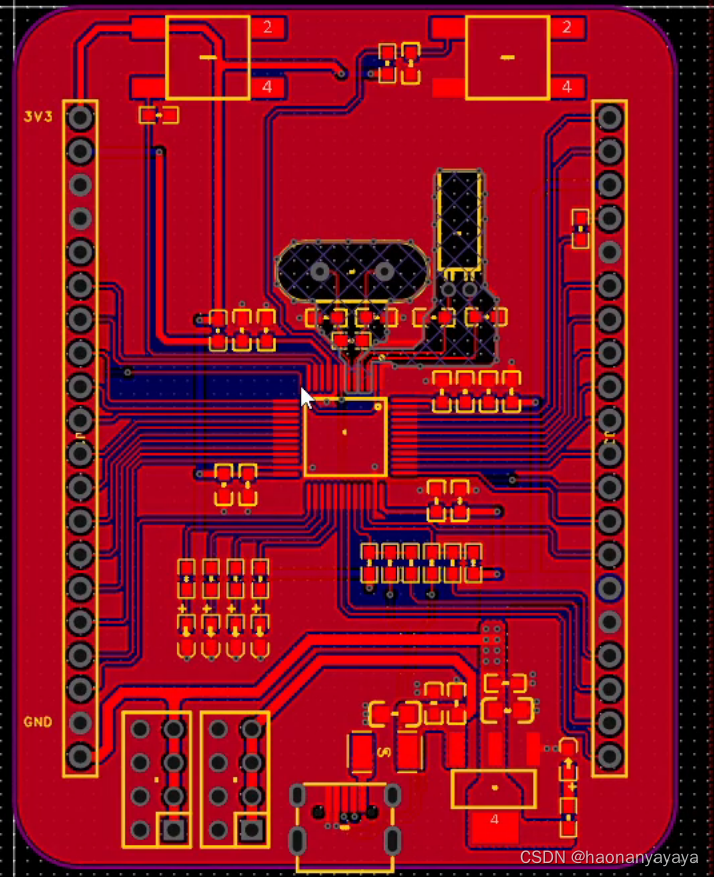

(3)布局

一般先把好确定位置的模块开始布局

首先在原理图中选中对应部分的器件

这时候可以发现PCB中对应部分的元件也被选中了

将同一个部分的东西放一块

这时候大致位置已经放好了,之后就是细致布局了。

一般是一个部分布完以后布下个部分,布局的时候要注意连接方便,比如VCC放一块

注意:电容滤波一般是VCC先过大电容,再过小电容,这点要注意

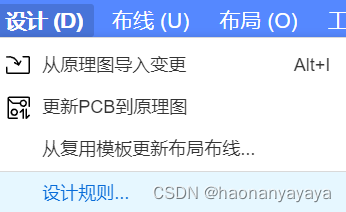

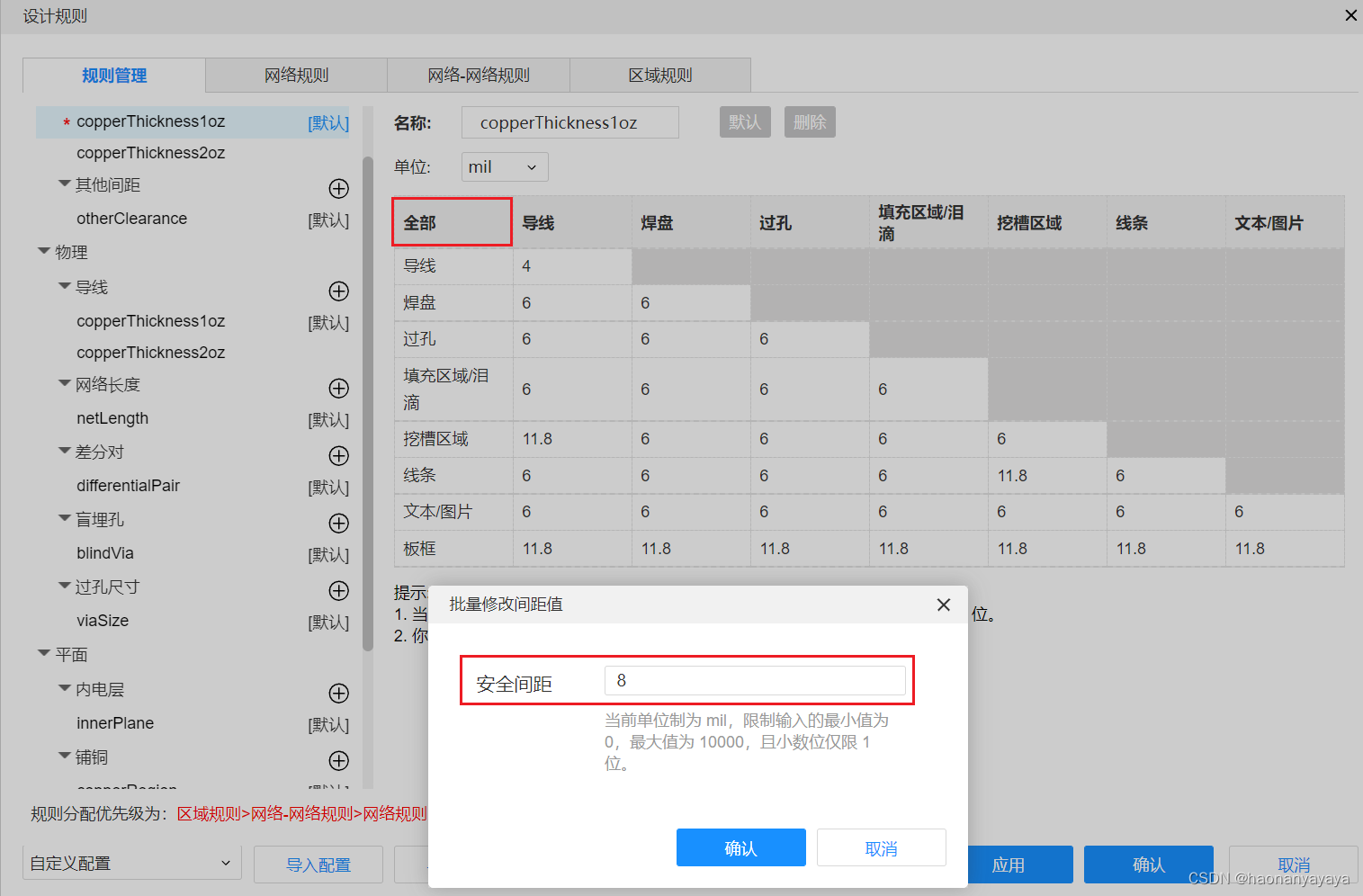

(4)设计规则

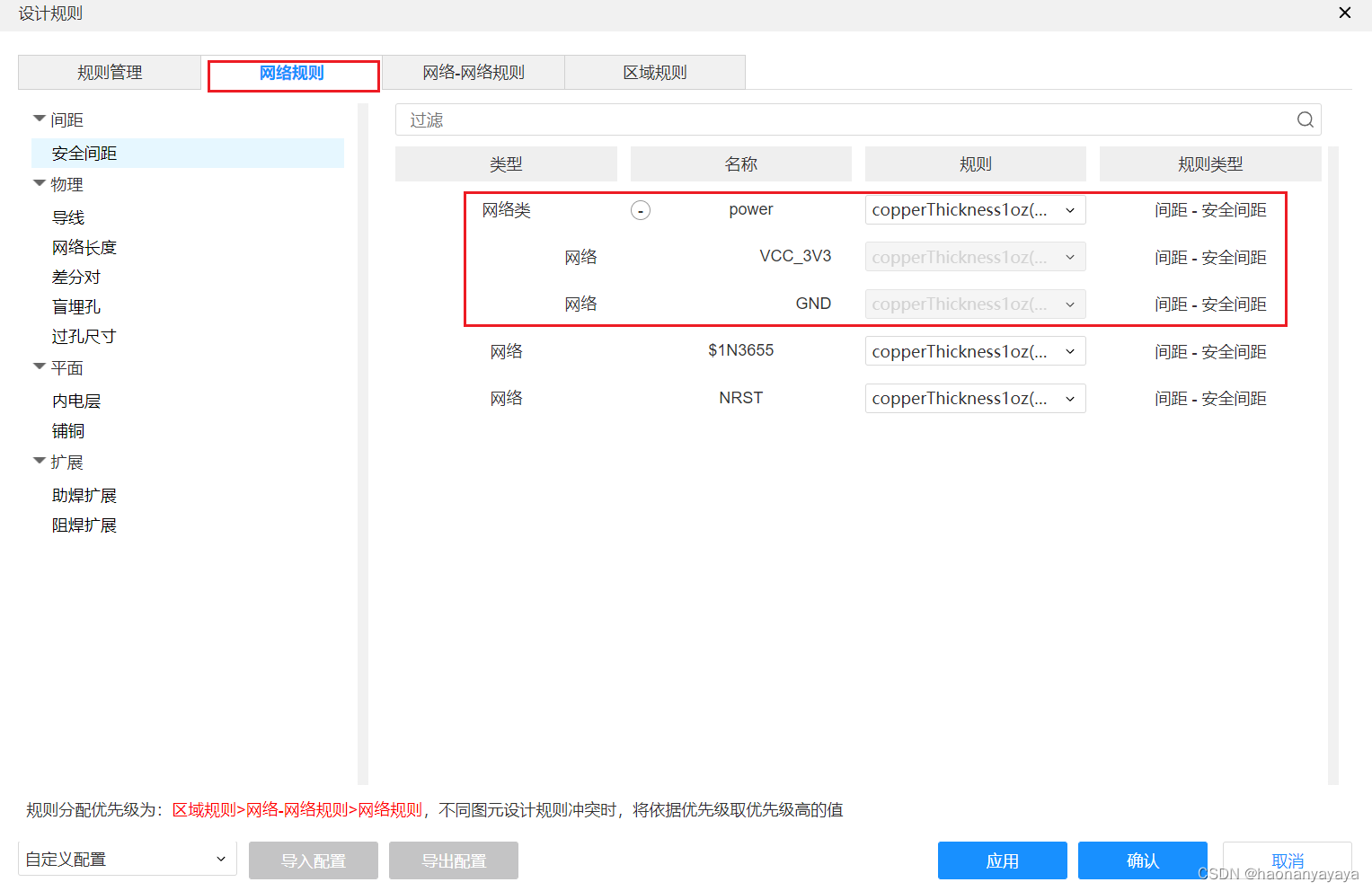

点击设计,设计规则

点击全部,即可一次设置所有距离规则

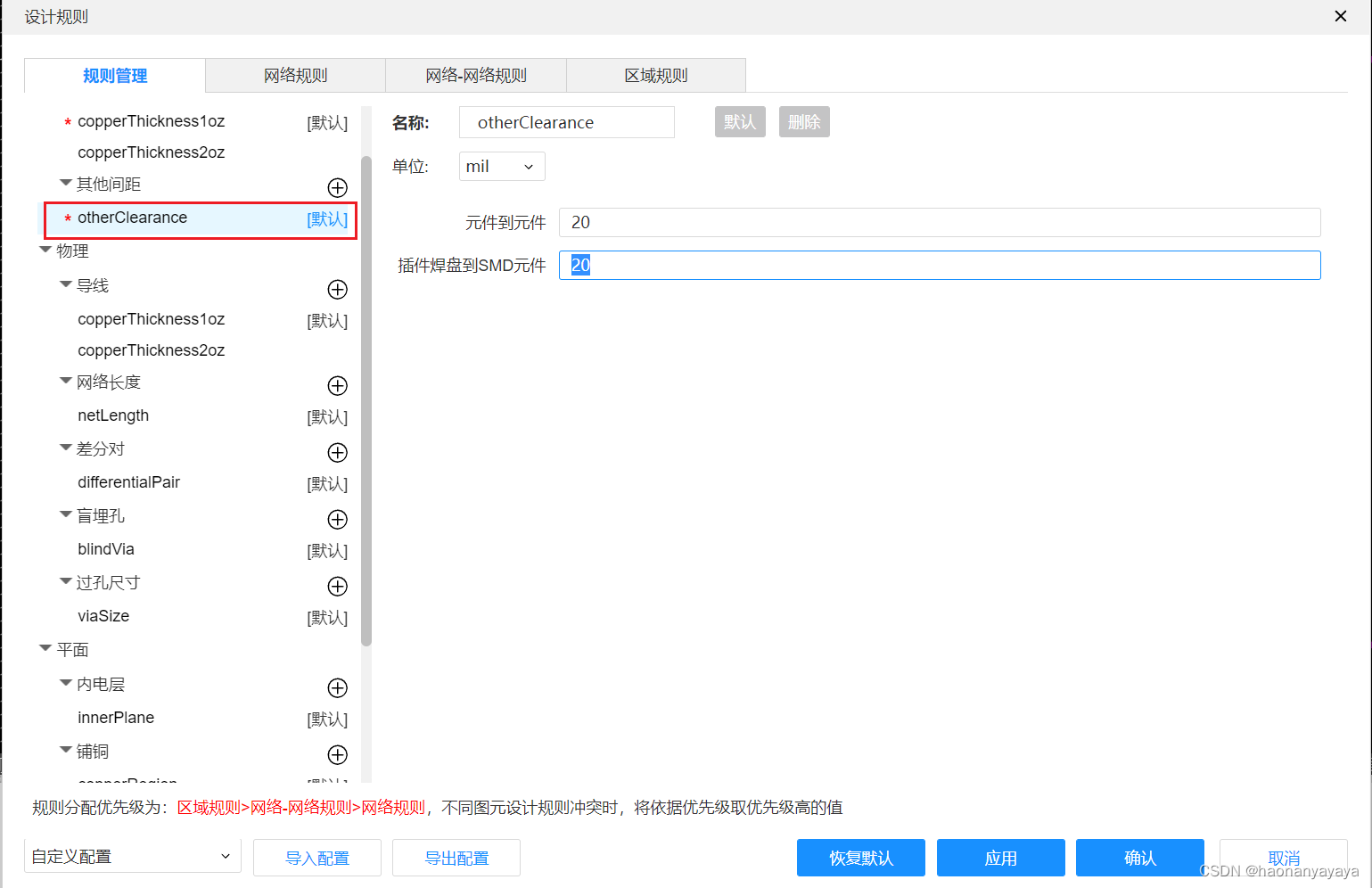

在点击其他间距,即可设置元件到元件等距离规则

如果不知道怎么设置,可以网上查线宽度

设计单独规则

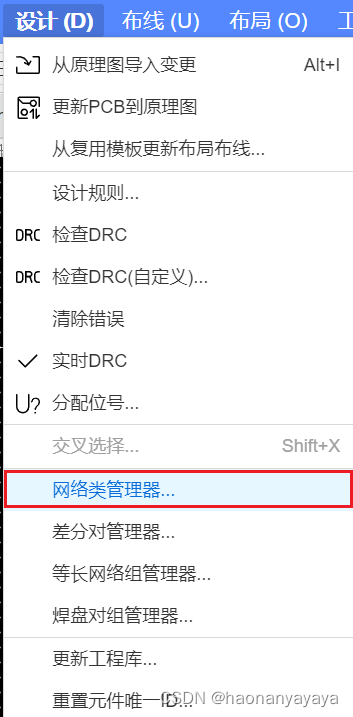

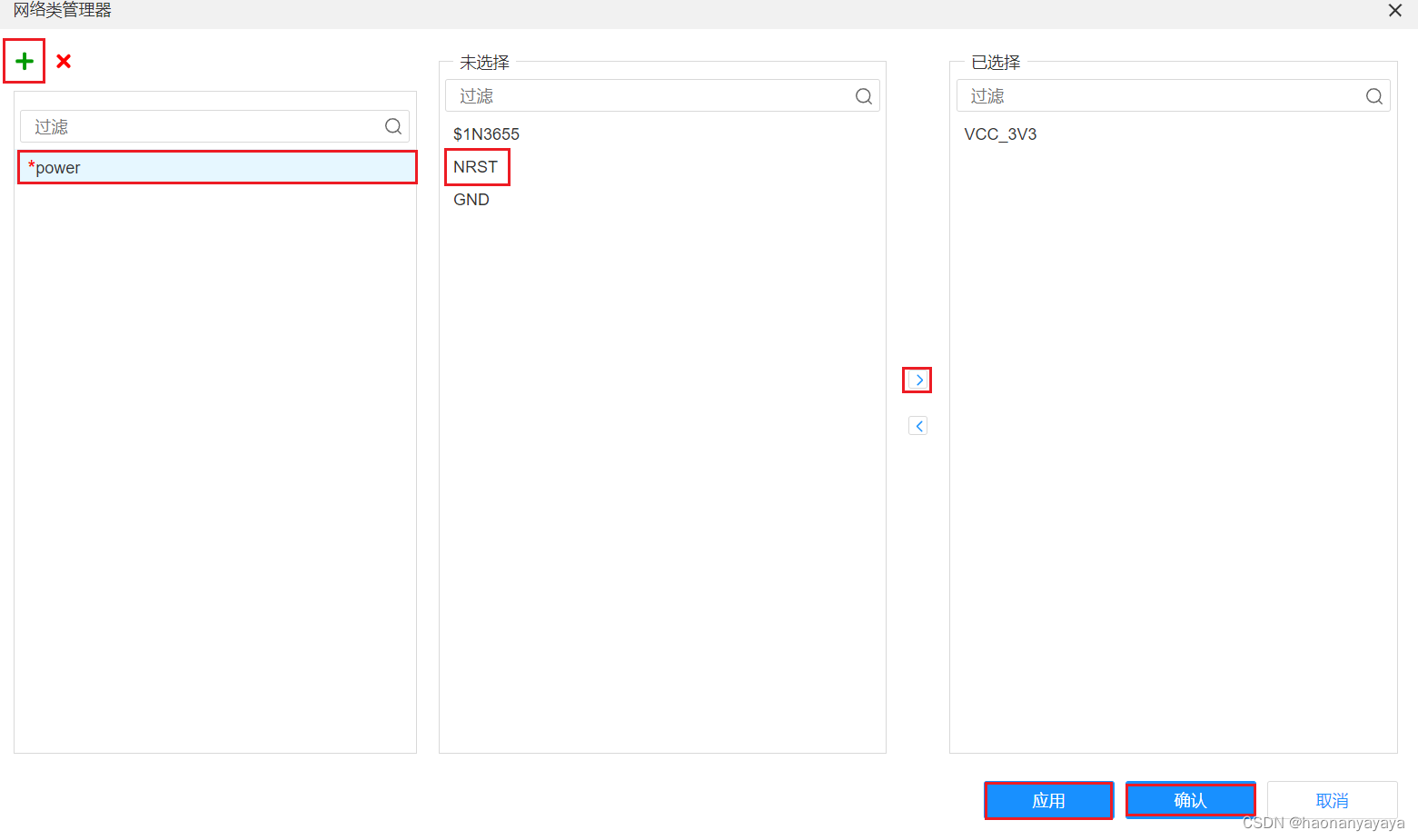

点击设计,网络类管理器

点击加号,输入名称,选择要使用的网络,点击箭头

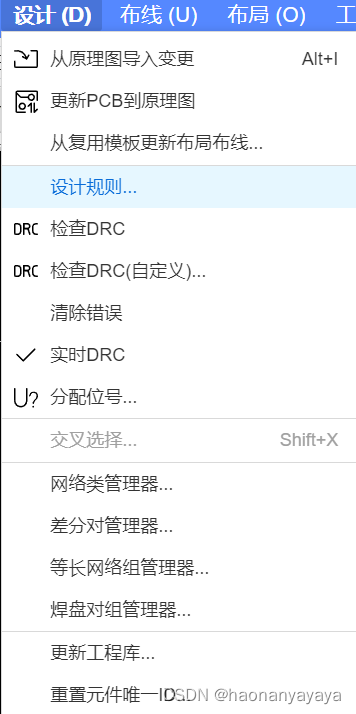

这时候再点击设置,设计规则

这时候点击网络规则即可看见添加的类

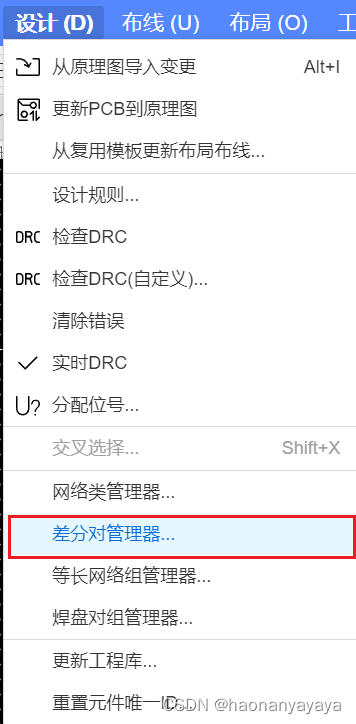

添加差分对

点击选择网络以后应用即可添加

有了差分对就需要设置规则,点击设计规则中的差分对即可设置

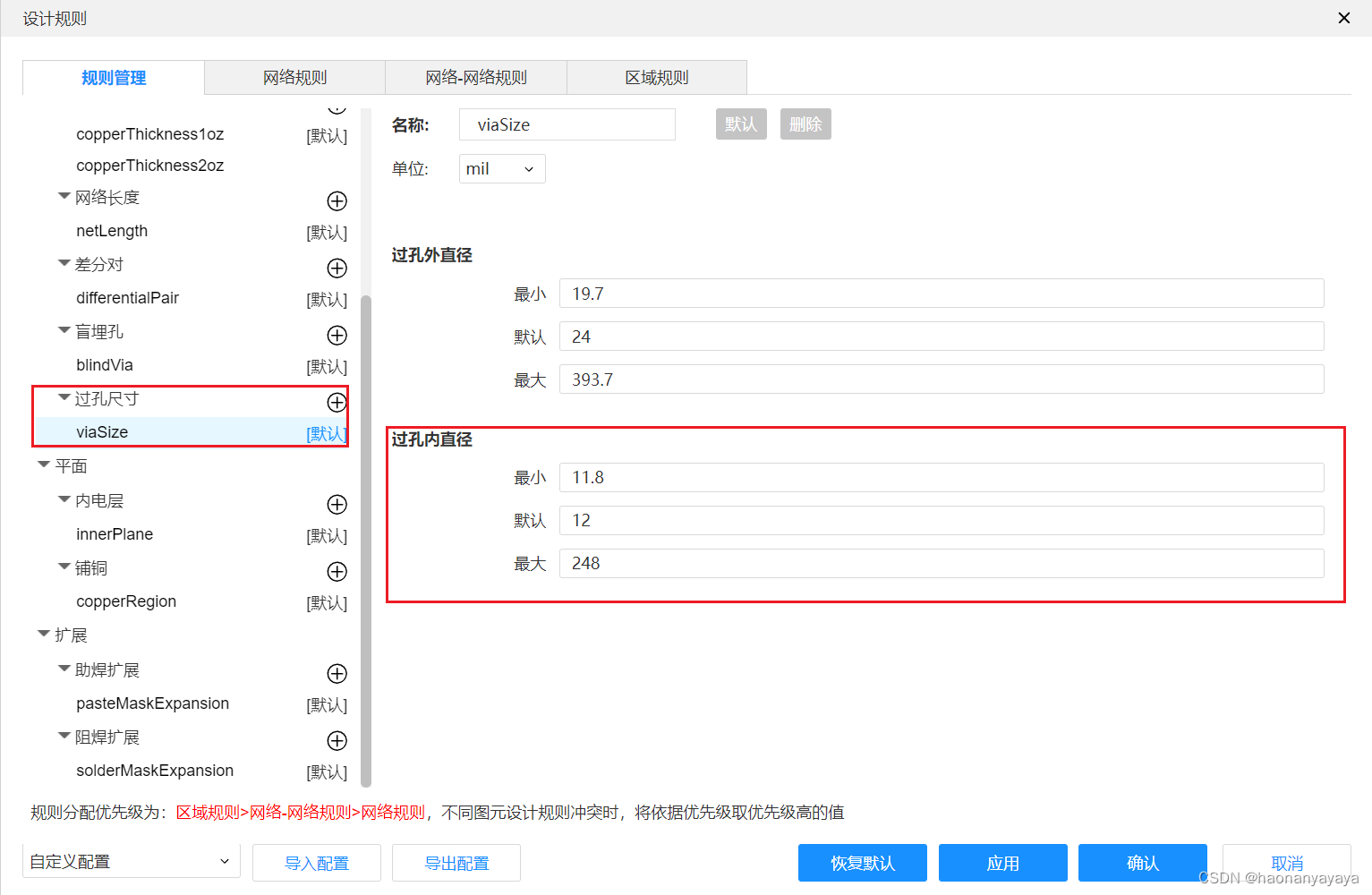

设计过孔尺寸规则(考虑载流能力)

一般过孔外直径是内直径2倍

如果不会可以使用计算机

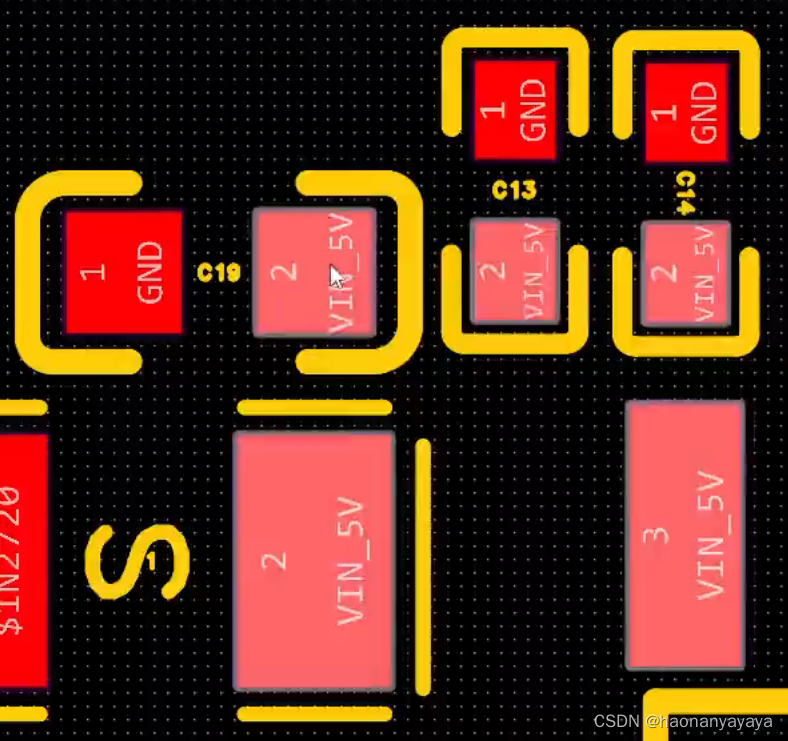

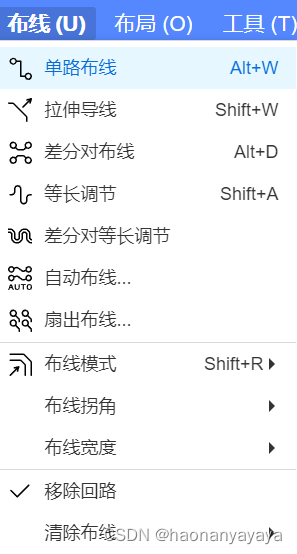

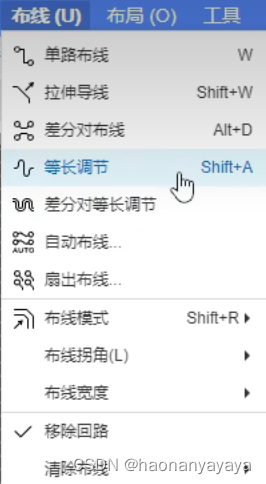

(5)布线

一般从复杂的地方开始布局

注意:不能出现锐角走线

点击布线,单路布线

根据需要设置规则

一般将起始布线宽度和起始打孔尺寸设置为跟随规则(默认和规则一样)

根据原理图将需要连接的部分连接

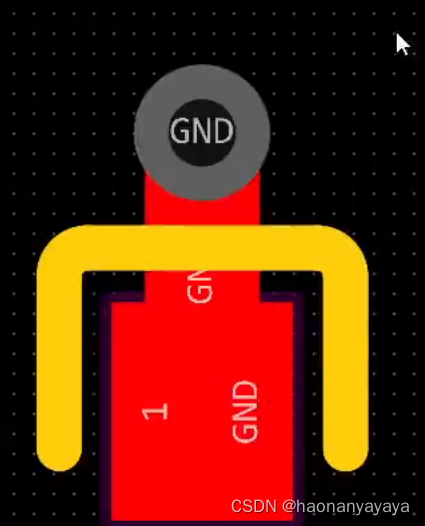

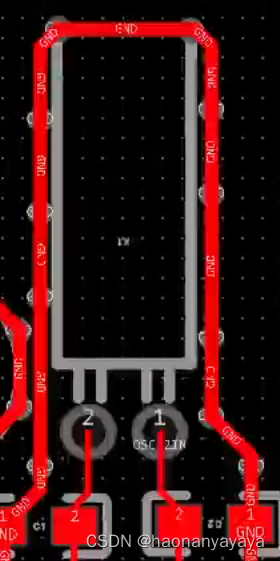

注意:晶振要做包地处理,即用地线将晶振包裹起来并在地线上打过孔,这个可以屏蔽干扰

一般情况下,底层都是整面铺地,电流最后要通过地回流,所以只需要一个过孔直接打到地即可

如果正面没地方走了,可以打过孔走底层

注意:如果是通孔,可以直接连接,但如果连接的是贴片元件,一定要再返回顶层连接

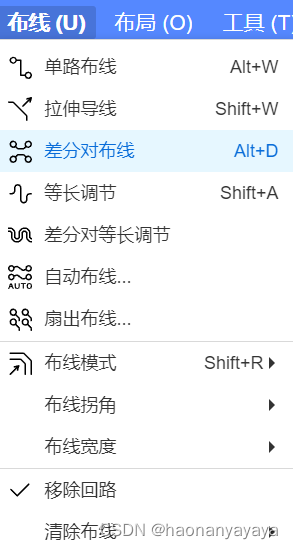

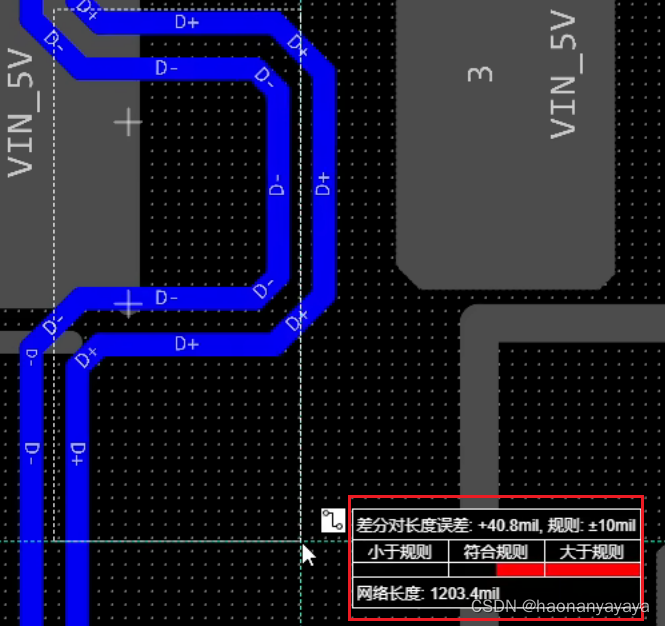

如果是差分对就点击布线,差分对布线,再选中差分器件

走完以后如果线长差距过大,就点击等长调节

右边自带是否符合规则显示

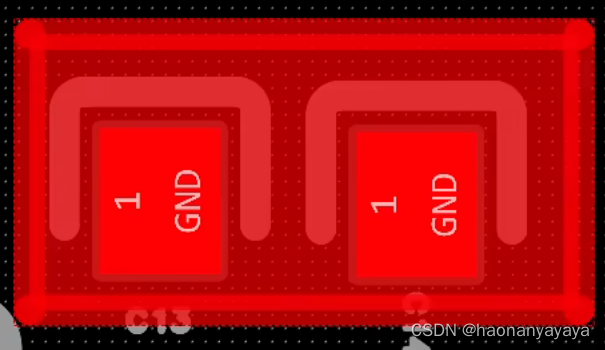

铺铜:由于电源VCC的电流大,所以要宽

首先选择设计规则

再修改规则

机械焊接选择直接连接:周围温度高,不怕散热快

手工焊接选择发散:铜皮大导致散热快,融锡会慢,不好焊

直接连接

发散10mil

发散20mil

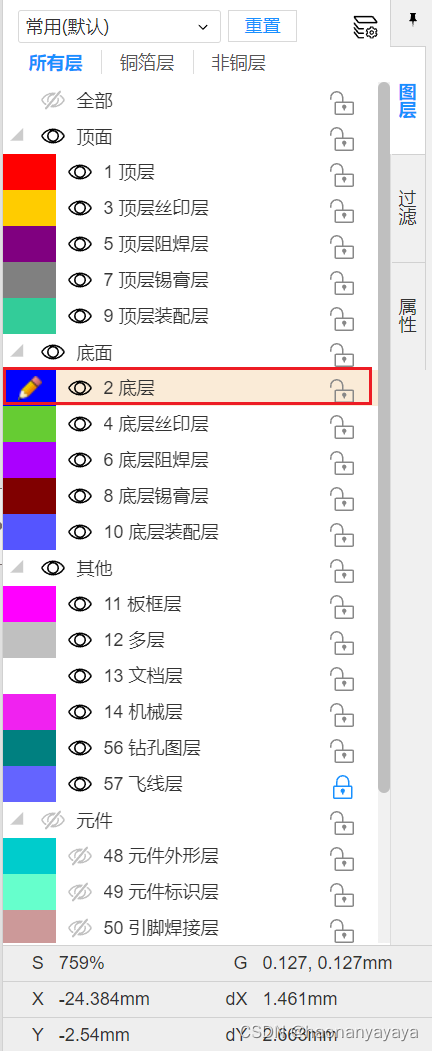

(6)铺铜

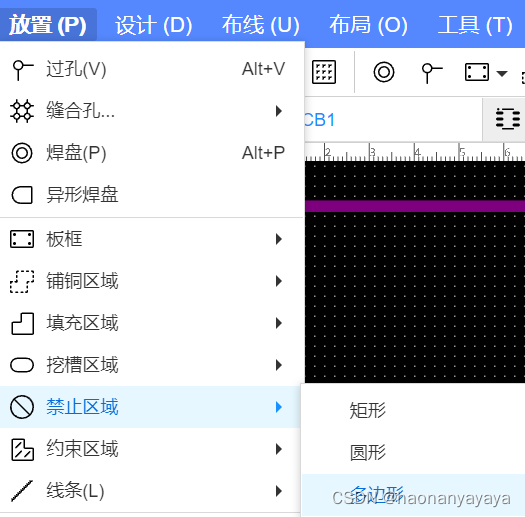

注意:晶振部分不要铺铜

这个禁止铺铜区域可以和之前晶振周围铺地范围一样

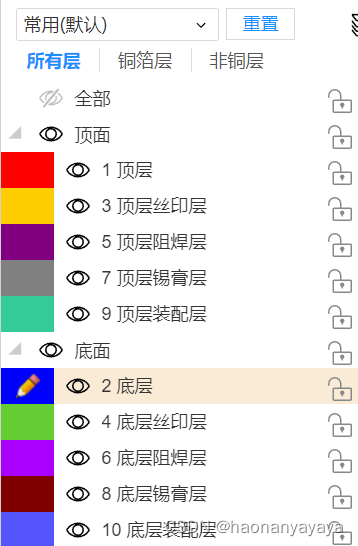

首先选择底层

点击放置,铺铜区域

将整个板子框起来(会自动避让)

如果认真看,会发现这个铜皮距离板框有距离

可以在设计规则中更改

底层铺好以后再铺顶层,也是铺地

(7)DRC错误检测

补充

1,如果画的位置错了,不想让元件移动的时候,导线也跟着移动

点击设置,原理图符号,常规,改变导线跟随方式

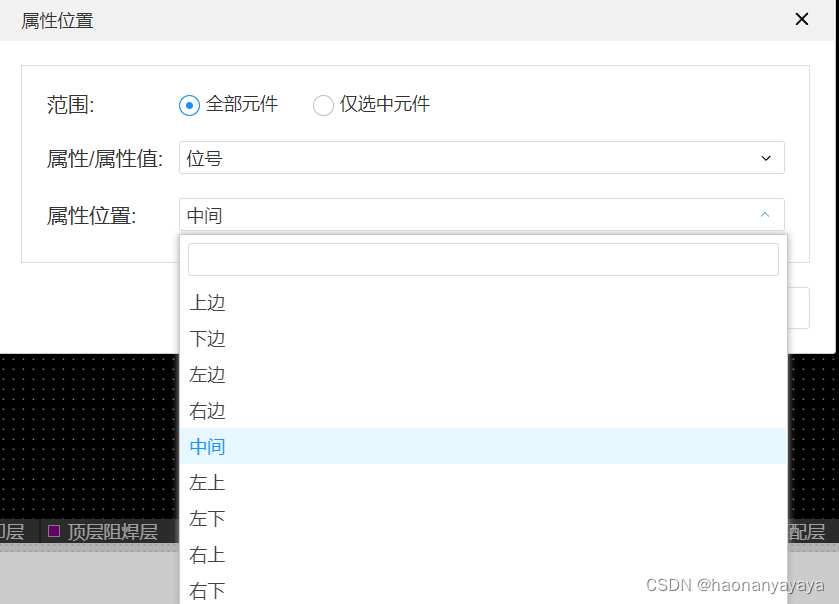

2,在进行PCB绘制的时候,如果认为位号不方便

点击布局,属性位置

属性位置修改为中间

画完以后一定要移出来

3,如果认为飞线太多,影响视野,可以先选中器件,按Ctrl+R

4,如果认为丝印影响布线,按快捷键Shift+S

5,铺铜被隐藏掉就使用Shift+M可显现

6,如果网络太多,不好辨认,就选中网络选择高亮

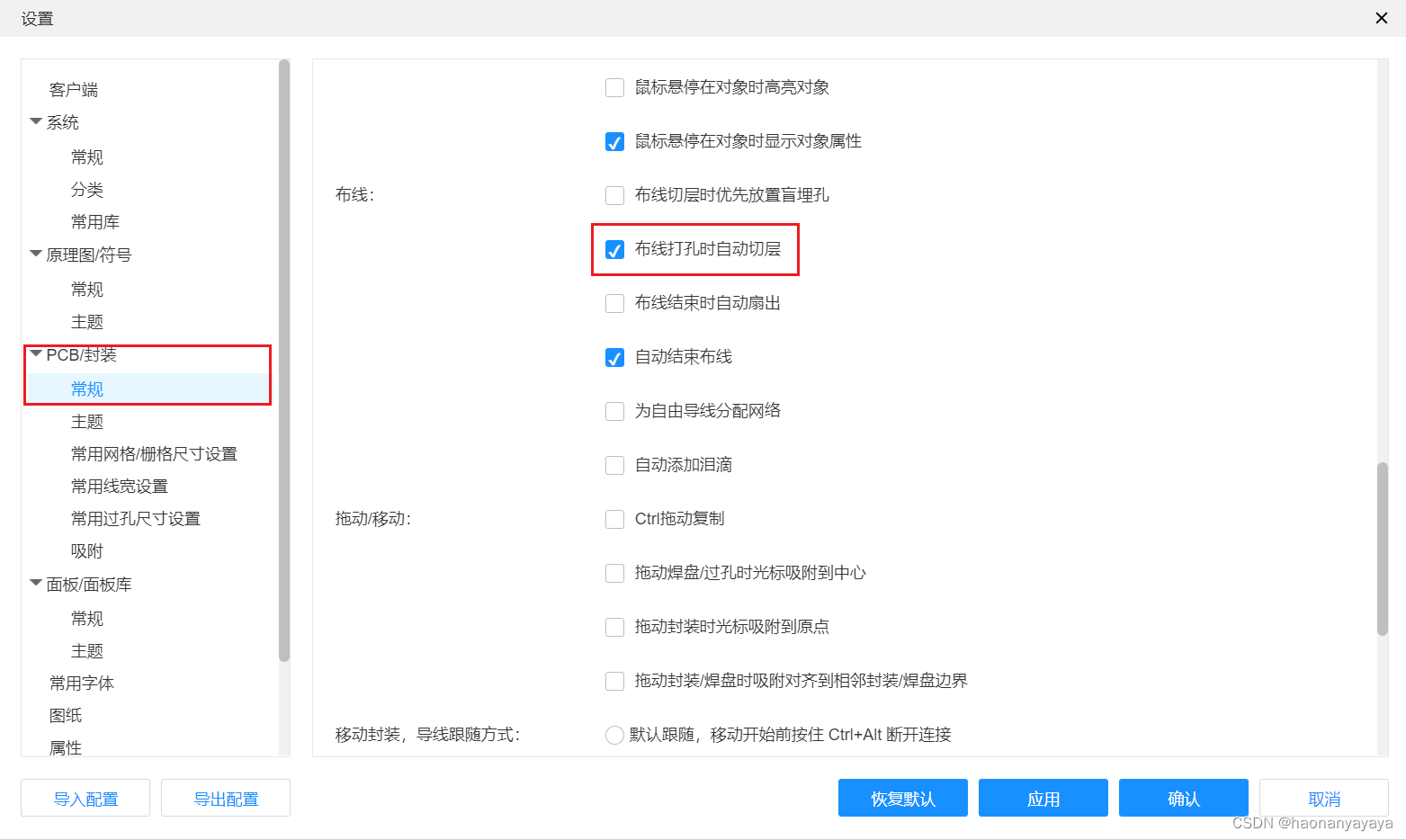

6,如果认为打孔以后切层麻烦,打开设置中的PCB/封装,将布线打孔时自动切层打开

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?