本文总结由数字电路设计的异步时钟引起的亚稳态问题,并针对亚稳态问题提出的处理方法和跨时钟域电路设计方法。重点是分析由异步时钟引起的跨时钟域CDC问题,后续将会总结由复位引起的电路亚稳态问题。

一、亚稳态问题

每一个触发器都有其规定的建立(setup)和保持(hold)时间参数,在这个时间参数内,输入信号在时钟的上升沿是不允许发生变化的。如果在信号的建立时间中对其进行采样,得到的结果将是不可预知的,即亚稳态。亚稳态是一种电路状态,在该状态下电路没法明确的传递“1”和“0”,因此会带来随机的数据比特翻转,导致电路设计失败。

衡量系统亚稳态时间的参数为MTBF (mean time between failures),该参数越大说明系统采样失败的可能性越小。该参数和采样时钟频率相关,时钟频率越高,MTBF越大,系统越容易出现亚稳态。MTBF计算公式:MTBF=(e^(tr/T))/T0*f*a (t上升时间,r和T触发器相关参数,f时钟频率,a采样时钟频率)。假设一个典型的0.25um工艺的触发器,tr=2.3ns,r=0.31ns,T0=9.6as,f=100MHz,a=10MHz,计算出MTBF=2.01days,也就是说该电路平均2天左右会出现一次亚稳态。现在成熟工艺已经进入到5nm,时钟频率最高到5GHz,亚稳态将在几个小时就会出现一次,已经严重影响产品质量和稳定性。并且,上述推算只是单个触发器出现亚稳态的时间,如果设计电路中存在多处亚稳态,那么整个系统可能会在几分钟甚至几毫秒内出现亚稳态。

亚稳态带来的结果和影响是巨大的,最直接的影响是整个该模块的系统异常,由于亚稳态采样的0、1随机,可能会导致正常的工作中断,电路只能通过复位寄存器重新恢复正常,但复位后无法再次恢复到正在工作的状态和寄存器数值,因此最终结果是该模块设计失败,需要重新RTL设计或ECO修复。

数字电路设计过程,应保证电路中没有上述直接采样的电路存在,通过代码规则检查中的CDC(Clock Domain Crossing)检查可以有效发现系统中存在该问题电路的位置。但是需要说明的是,不是所有的CDC检查报错的结果都需要修改,还需要根据电路的实际情况进行分析,例如一个寄存器的功能只在复位后修改一次,那么该寄存器数值不会反复变化,从而不会产生亚稳态,尽管其输入时钟和读取时钟为异步关系。

二、单比特跨时钟域处理

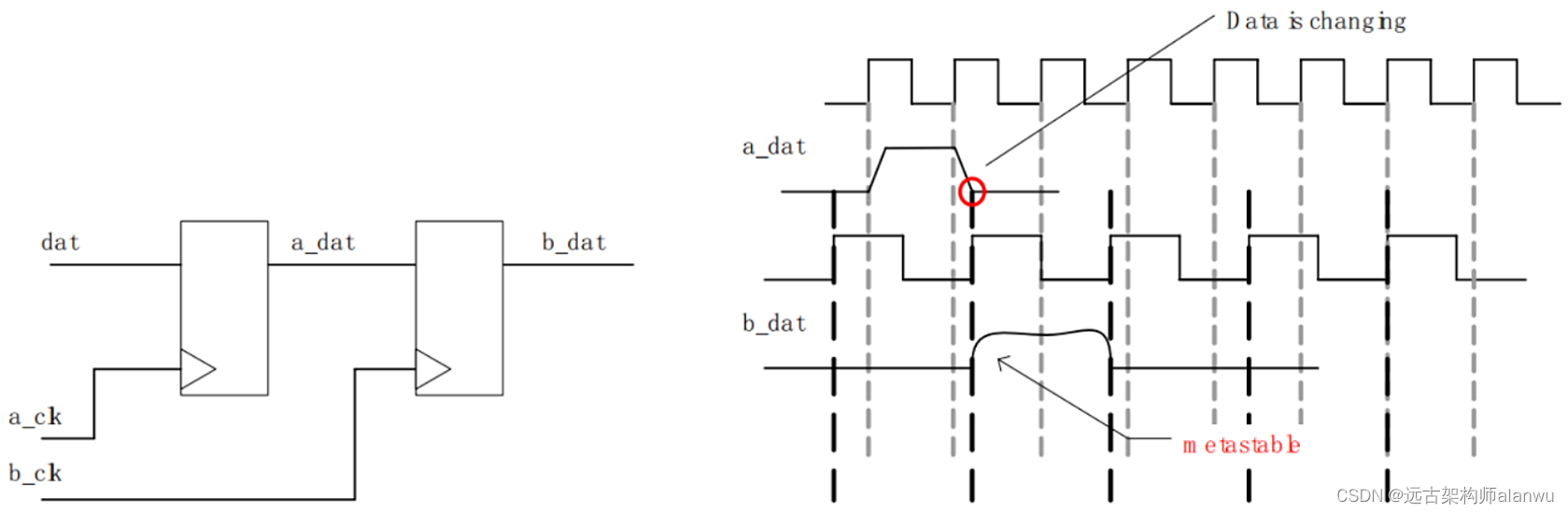

为了避免亚稳态,应该使得MTBF尽量大,采用双锁存器级联可以有效改善这一问题。对于只有单个bit需要跨时钟域的,建议采用上图所示的方式处理。按照图中所示方式,MTBF=9.57*109 years,有效提高了系统稳定性,亚稳态难以再采样出现。

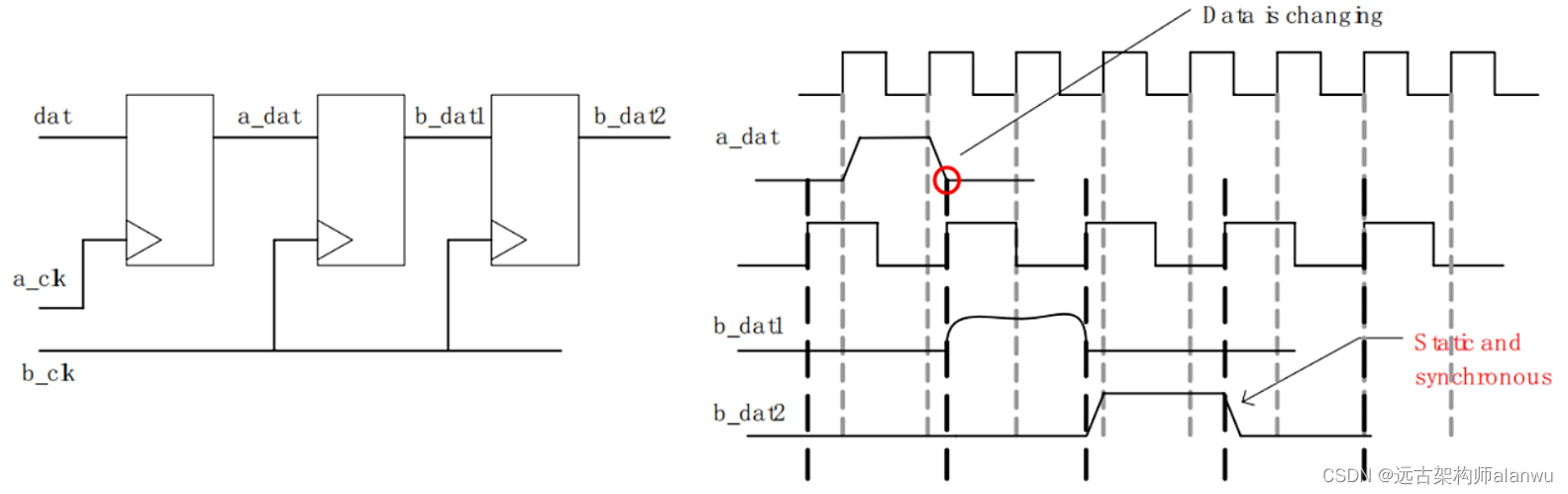

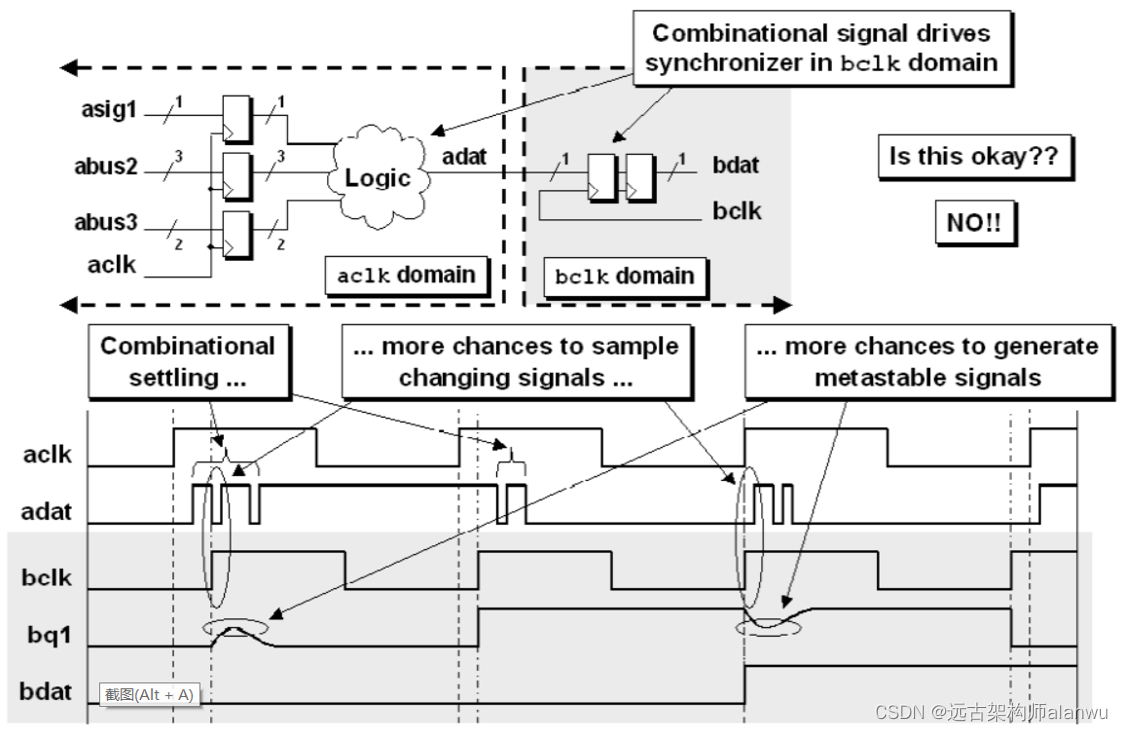

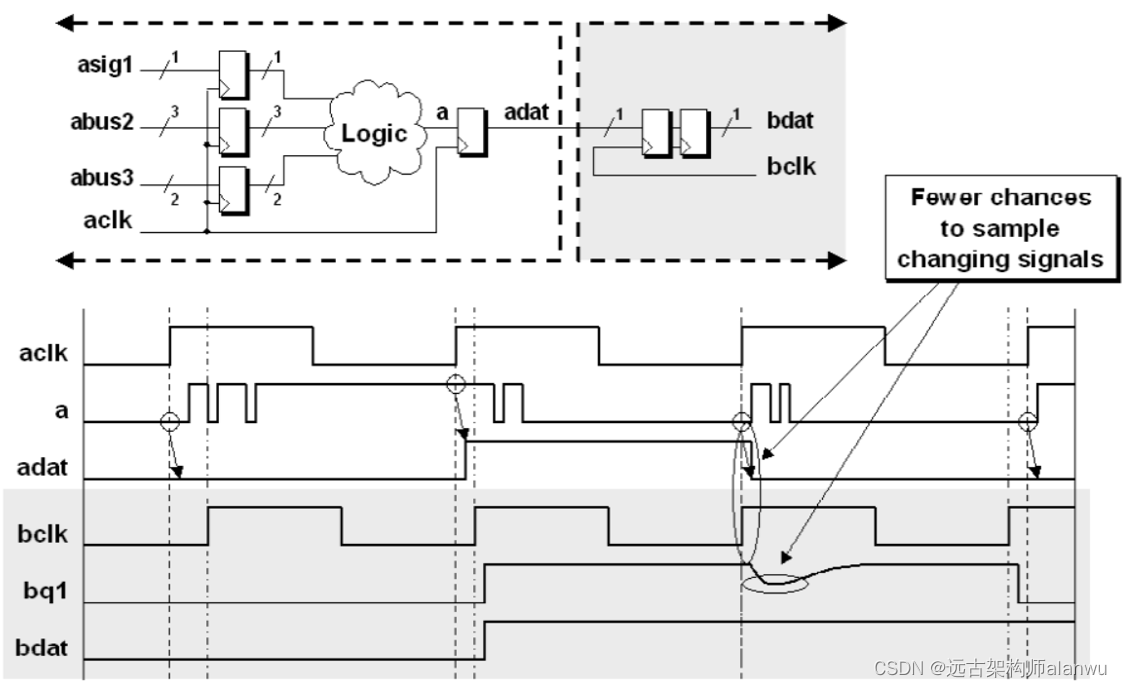

该电路要求跨时钟结构尽量干净,在跨时钟域的两个寄存器之间,不能有组合逻辑存在。组合逻辑电路各个输入信号的不一致性以及组合逻辑内部路径的延时时间不一样,运算后的信号存在毛刺。

因此,如果跨时钟的寄存器必须有组合逻辑,也需要将该组合逻辑在跨时钟前处理成单比特,再使用两级的寄存器两拍同步。也就是说如果CLKB能采到稳定信号,时钟域A的信号必须经过CLKA打拍,在一个时钟周期内稳定输出,结构修改如下图所示:

除此以外,跨时钟域还需要注意下面两个问题:

- 需要注意clock gating的使能信号,如果跨时钟域,也需要单比特cdc处理;

- 跨时钟域两边时钟的快慢问题;

如果较快的时钟域是较慢时钟域频率的1.5倍(或更多),那么将较慢的控制信号同步到较快的时钟域通常不是问题,因为较快的时钟信号将采样较慢的CDC信号一次或多次。因此,快采慢比慢采快引起的潜在问题更少,所以对于快采慢的情况,使用简单的两个触发器同步器在时钟域之间传递单个CDC信号即可。

而对于慢采快的情况则最好更加稳妥些,一般要求在接收时钟域中采样信号要保持三个采样时钟沿的时间("three edge" requirement),也就是1.5倍的采样时钟周期,一般来说1.25倍也够。如果采样信号维持时间过短,可能会导致慢时钟域漏采。

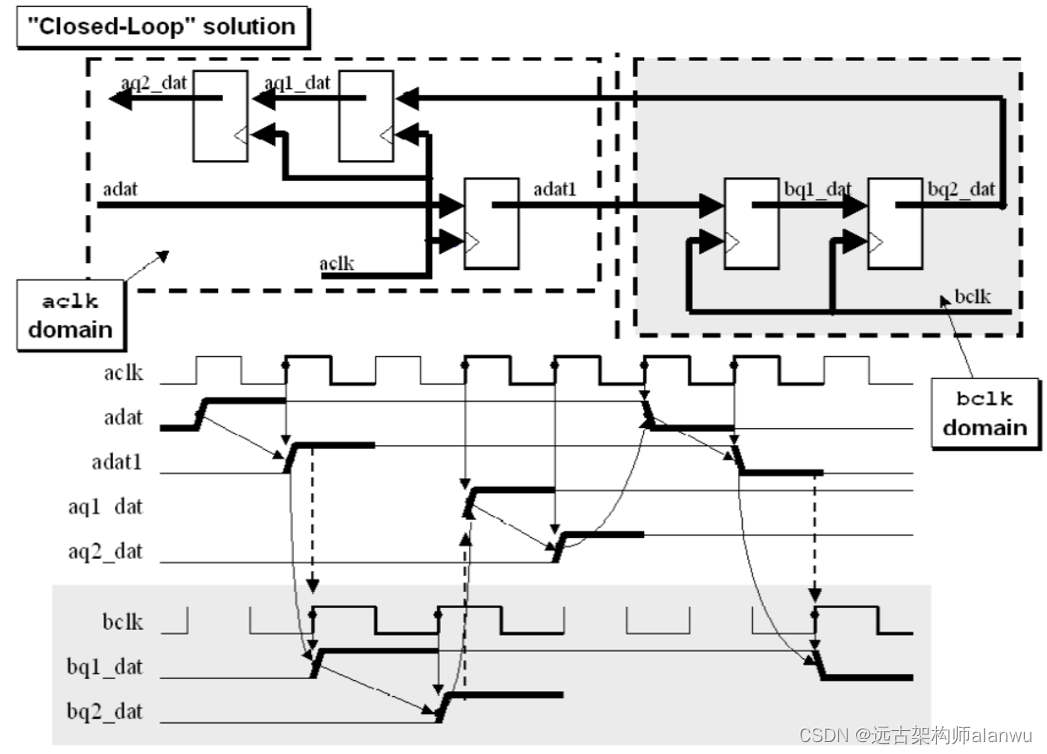

一般采用闭环控制的方法处理慢采快的电路,其原理是将二级同步后的数据再反馈到快时钟域,并在快时钟域二级同步,结构如下图所示:

将A时钟域要传输的信号打一拍送到B时钟域中进行双reg同步,同步之后的信号再反馈到A中,A中再进行双reg同步,当A域中反馈同步信号变为高时才将被采信号拉低,这样的方法时比较稳妥的,但是会有更多的延时,并且需要更多同步寄存器。

三、多比特跨时钟域处理

3.1 多比特控制信号

对于多比特控制信号同步,采用如下策略处理:

- 如果控制信号之间相互独立,则采用单比特的方式处理;

- 如果控制信号之间同步变化,也就是说在同一时间周期变化,则采用合并信号的方式处理,在跨时钟前将逻辑合并,再采用单比特的方式处理;

- 如果控制信号之间存在时钟相位差,且信号之间的相位固定,则只传递其中单比特信号,剩余控制信号在同步域产生;

3.2 多比特数据

3.2.1 开环结绳法

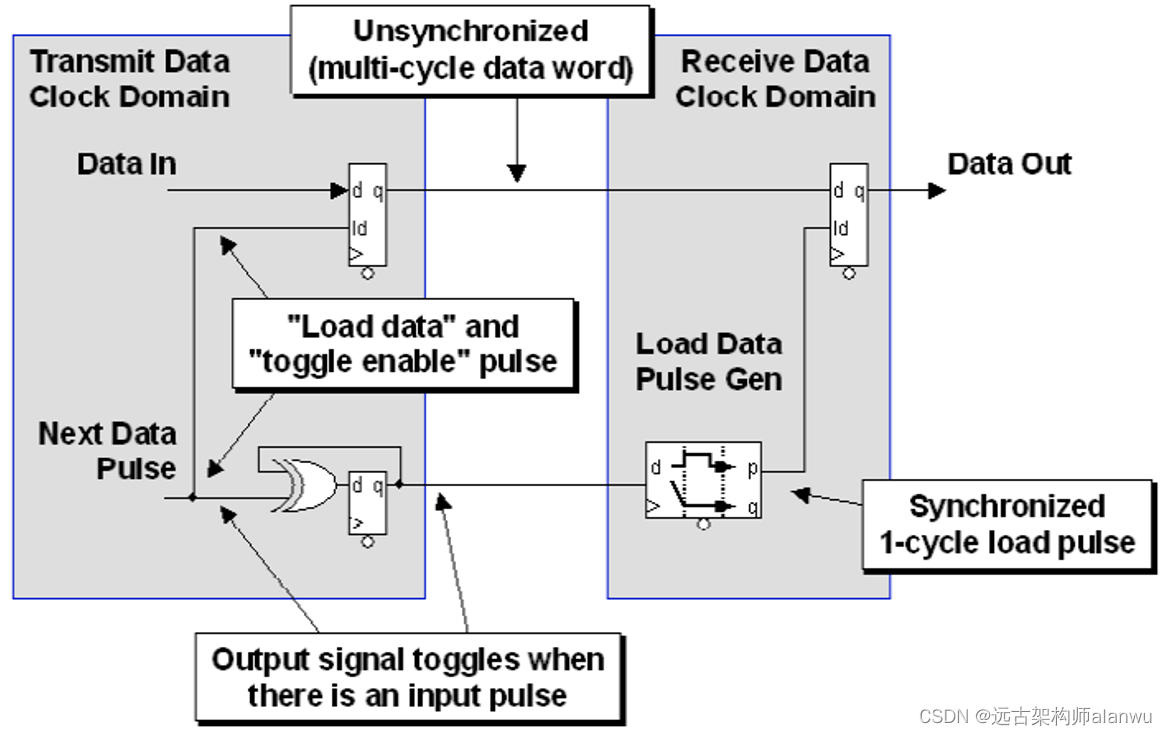

开环结绳法主要是将数据的变化转变为一个对应的脉冲信号,用来指示数据的开始和结束。该方法主要的处理步骤为:

- 在A时钟域产生一组单周期脉冲,其间隔至少需要比B时钟域的两个时钟周期大,否则B中无法进行边沿检测。同时这组脉冲也表示了A中数据传送的开始和结束。

- 在A时钟域中,两个脉冲被电平翻转器(可以由异或门或者mux+inv构成)将脉冲之间的区域变为一段高电平(结绳toggle)。

- A中的结绳信号在B中通过边沿产生器翻译为两个单周期脉冲。

- B中需要由逻辑去监测脉冲并进行信号的采样。

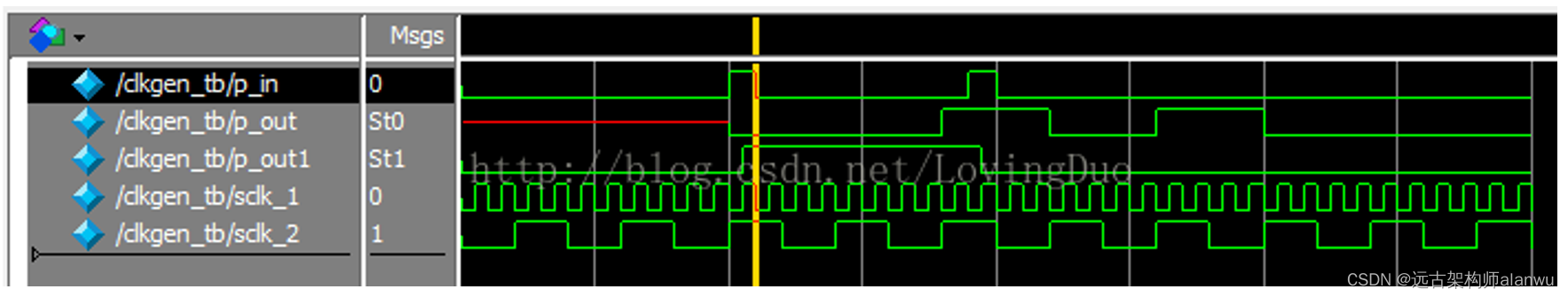

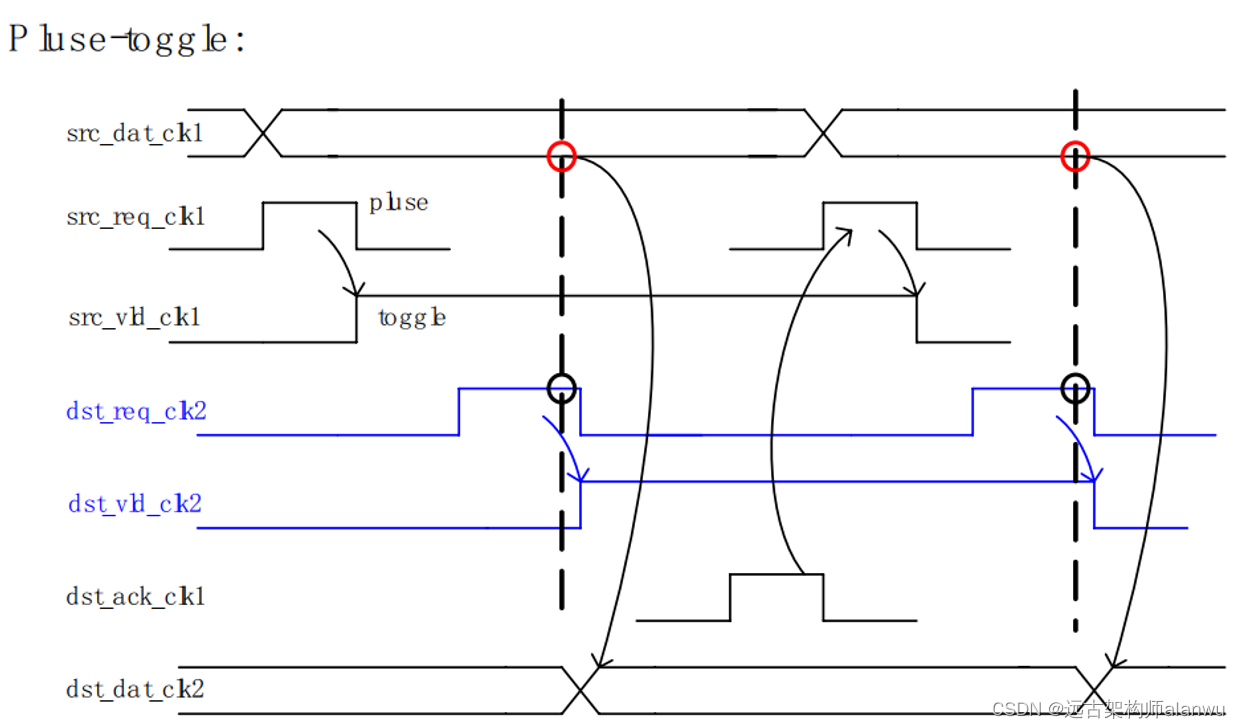

使用该方法仿真得到的波形如下图所示。

3.2.2 闭环结绳法

开环结绳法的一个缺点是脉冲之间的宽度问题,太窄的宽度可能导致漏采样,而开环的方式无法知道多长的宽度合适,因此使用闭环结绳法可以解决该问题。

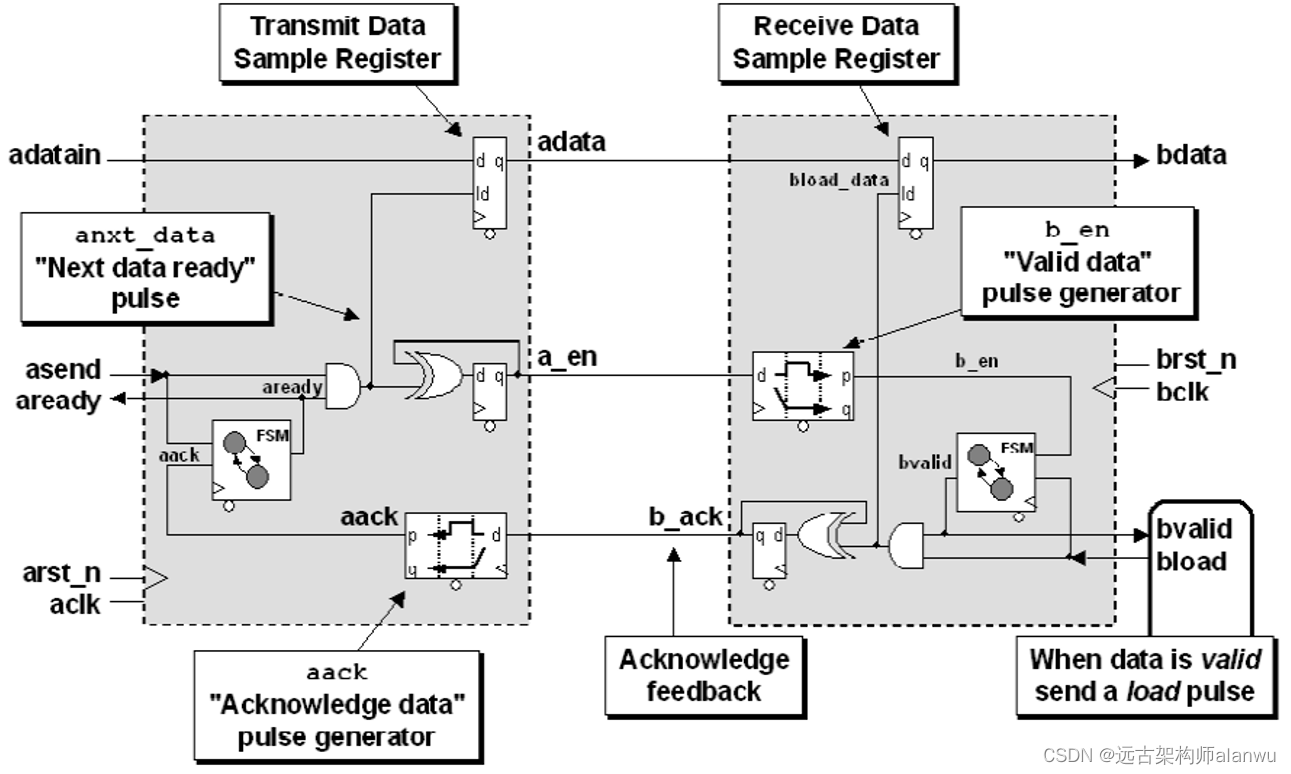

闭环结绳的基本步骤如下:

- 在A时钟域产生一个发送数据的开始的标志脉冲,经过结绳、解绳到B中变成另一个脉冲;

- 将B中的脉冲送入状态机,经过FSM产生该脉冲的应答脉冲,且同样结绳、解绳到A端;

- A端将同步过来的应答信号送入状态机,经过FSM产生ready信号,表征B端数据稳定可同步;

- A端产生发送数据的结束标志,并结绳、结绳到B端,这样一个完整的结绳法过程就结束了。数据在此期间保持不变,直到A端结束标志产生。

使用该方法仿真得到的波形如下图所示。

3.2.3 异步FIFO

异步FIFO是处理多比特跨时钟域的最常用方法,也是现在多比特数据跨时钟域同步的最常用的设计,通常采用双口RAM+格雷码的方式完成跨时钟域处理。关于异步FIFO结构和格雷码跨时钟原理和异步FIFO的设计方法,很多文章已经写的非常详细了,这里不再赘述。

1733

1733

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?