电容作为电子电路中最基础的无源元件之一,其封装选型直接影响电路性能、产品可靠性和生产成本。本文将深入探讨PCB设计中电容封装选择的12个关键维度,结合工程实践经验与行业规范,为硬件工程师提供系统化的选型策略。

一、电容封装与电气性能的对应关系

1.1 容值与封装尺寸的匹配原则

根据当前的技术研究,不同容值范围的电容存在典型的封装对应关系:

- 0.1pF-1nF:优选0402/0603封装(如0.1μF MLCC常用0603)

- 1nF-10μF:适用0805/1206封装(如10μF陶瓷电容多采用0805)

- 10μF-100μF:需使用1210/1812或钽电容封装(如47μF钽电容常用3528)

- 100μF以上:必须选择电解电容或特殊大容量MLCC封装(如100μF电解电容多采用7343)

热设计提示:大容量电容的封装选择需结合纹波电流计算,例如1206封装的10μF X5R电容在1MHz时允许的纹波电流约为50mA,而同等容值的钽电容可承受200mA以上。

1.2 耐压特性的封装关联

实验数据表明,封装尺寸直接影响耐压能力:

降额原则:实际工作电压应≤额定值的60%(高温环境下需≤50%)

二、物理特性对封装选择的影响

2.1 机械应力与封装强度

- 0402/0201:适用于柔性PCB但需注意弯曲应力,在振动环境中建议采用underfill工艺

- 3528/7343:钽电容需避免剪切应力,布局时与板边距离≥2mm

- 电解电容:直径≥8mm需增加固定胶,防止机械共振

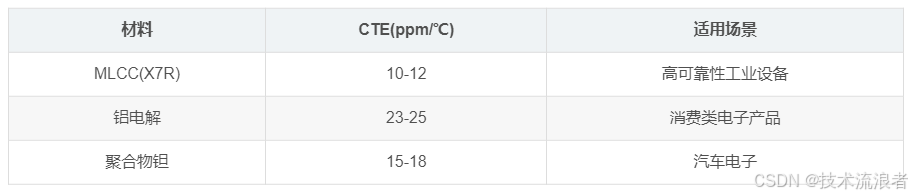

2.2 热膨胀系数(CTE)匹配

不同封装材料的CTE差异:

焊接建议:选择CTE接近FR4基板(14-17ppm/℃)的封装可降低热应力失效风险

三、电路特性与封装的协同设计

3.1 高频特性优化

不同封装的寄生参数差异显著:

- ESL对比:

- 0402:约0.3nH

- 0805:约0.6nH

- 1210:≥1.2nH

- 谐振频率选择:

举例:10nF 0402电容(L=0.3nH)谐振频率≈29MHz,适合500kHz-20MHz滤波f_res = 1/(2π√(LC))

3.2 电源完整性设计

多层PCB的退耦电容布局策略需要结合封装特性与电路需求,实现从低频到高频的全频段噪声抑制

1. Bulk电容布局

- 功能定位:承担低频段(<100kHz)的储能和纹波抑制

- 封装选择:100μF+电解电容优先采用7343封装或φ10mm圆柱封装

- 布局要点:

- 布置在电源入口处,距离连接器≤15mm

- 采用星型接地布局,减少地弹噪声

- 并联多个小尺寸电容时,优先选择3528封装钽电容5

2. 中频退耦设计

- 频段覆盖:100kHz-50MHz噪声抑制

- 典型配置:

- 10μF 0805陶瓷电容每3-5cm间隔布置

- 每平方厘米板面积配置0.5-1μF容值

- 特殊处理:

- 电源层分割区域需跨接0805/1206封装电容

- 数字/模拟混合电路需采用0603封装隔离8

3. 高频退耦策略

- 目标频段:50MHz-1GHz高频噪声吸收

- 实施方案:

- 0.1μF 0402电容紧贴IC电源引脚(间距≤2mm)

- 每个BGA封装底部布置4-8颗0201电容

- 射频模块电源入口串联0402铁氧体磁珠

- 关键技术:

ESL_max = ΔV/(di/dt) % 根据瞬态电流变化率计算最大允许ESL 举例:CPU核心供电要求ESL<0.5nH,需采用0201封装多电容并联4. 三维布局技巧

通过多层PCB的立体空间优化,可显著提升高频电路性能并降低寄生参数干扰

- 过孔背贴:0402电容通过盲孔布置在器件背面,环路电感降低40%5

- 层间耦合:

– 相邻电源/地层间距≤4mil

– 在电源过孔旁布置0402电容,间距<100mil - 跨层连接:

– 每对电源/地过孔配置1颗0603电容

– 高速信号换层处增加0805隔直电容

设计验证:使用矢量网络分析仪(VNA)测量目标频段的阻抗曲线,确保在100kHz-1GHz范围内阻抗<1Ω8。对于DDR4/5等高速接口,需保证每个数据线配置两个0402退耦电容,间距不超过信号线长度的1/10波长

994

994

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?