目录

1.算法仿真效果

本系统进行了两个平台的开发,分别是:

Vivado2019.2

Quartusii18.0+ModelSim-Altera 6.6d Starter Edition

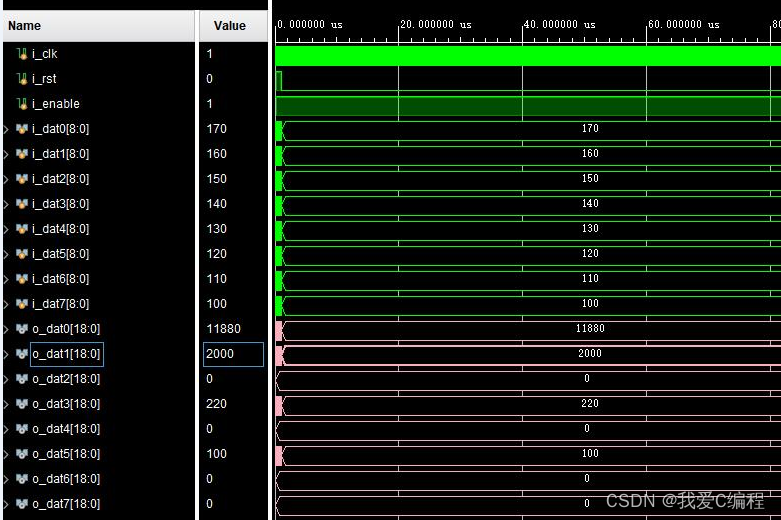

其中Vivado2019.2仿真结果如下:

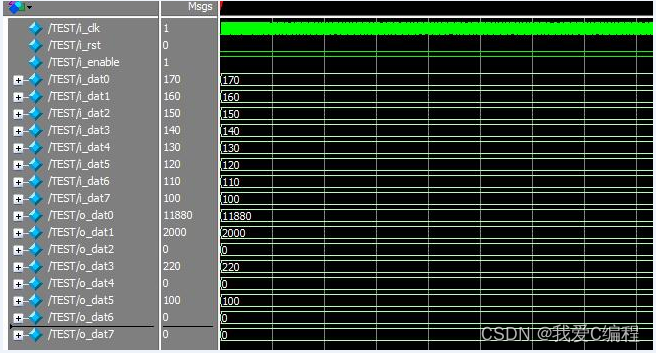

Quartusii18.0+ModelSim-Altera 6.6d Starter Edition的测试结果如下:

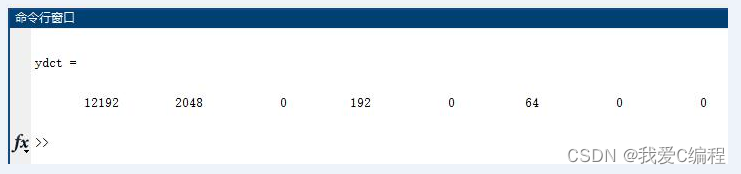

matlab对比结果如下:

部分小的误差是由于FPGA设计过程的量化以及二进制位宽截取产生的,但总体数据大小和matlab仿真一致。

2.算法涉及理论知识概要

DCT(Discrete Cosine Transform)是一种基于余弦函数的一维或二维离散变换,常用于信号压缩、图像处理等领域。在本文中,我们将介绍如何通过FPGA实现一维8点DCT变换。一维8点DCT(离散余弦变换)是一种常用的信号处理技术,它在图像和音频压缩、数据压缩和加密等领域中广泛应用。本文将介绍如何使用FPGA实现一维8点DCT变换。在开始实现之前,我们需要了解一些基础知识。DCT是一种变换,它将一组实值序列转换为一组实值序列。离散余弦变换(DCT)是一种将一组实值序列转换为一组实值序列的线性变换,它与傅里叶变换有关。一维8点DCT变换的公式如下:

X(k)=α(k)∑_(n=0)^(N-1) x(n)cos((π/N)(n+1/2)k)

其中,α(k)是一个归一化的系数,k=0,1,2,…,N-1。

在FPGA中实现DCT变换时,需要将输入数据存储到FPGA的内部存储器中。对于一维8点DCT变换,输入数据长度为8,可以采用RAM(Random Access Memory)或FIFO(First In First Out)等数据存储器进行存储。

DCT变换公式中包含余弦函数的计算,因此需要在FPGA中实现余弦函数的计算。通常可以采用LUT(Look-Up Table)或CORDIC(COordinate Rotation DIgital Computer)等方法进行计算。其中,LUT方法是通过预先计算余弦函数表格,并将其存储到FPGA的内部存储器中,然后根据输入角度值查找对应的余弦函数值。CORDIC方法则是通过迭代计算旋转角度和坐标值,最终得到余弦函数值。

DCT变换公式中包含乘法和加法运算,因此需要在FPGA中实现乘法器和加法器。通常可以采用DSP(Digital Signal Processing)模块或硬件实现乘法器和加法器。在FPGA中,同步器和时钟是非常重要的组件。同步器用于将外部信号同步到FPGA内部时钟域中,以保证数据的稳定性和可靠性。时钟则是FPGA内部各模块协调工作的基础。

3.Verilog核心程序

.........................................................

reg [8:0] i_dat0;

reg [8:0] i_dat1;

reg [8:0] i_dat2;

reg [8:0] i_dat3;

reg [8:0] i_dat4;

reg [8:0] i_dat5;

reg [8:0] i_dat6;

reg [8:0] i_dat7;

wire [18:0] o_dat0;

wire [18:0] o_dat1;

wire [18:0] o_dat2;

wire [18:0] o_dat3;

wire [18:0] o_dat4;

wire [18:0] o_dat5;

wire [18:0] o_dat6;

wire [18:0] o_dat7;

DCT8_tops uut (

.i_clk (i_clk),

.i_rst (i_rst),

.i_enable (i_enable),

.i_dat0 (i_dat0),

.i_dat1 (i_dat1),

.i_dat2 (i_dat2),

.i_dat3 (i_dat3),

.i_dat4 (i_dat4),

.i_dat5 (i_dat5),

.i_dat6 (i_dat6),

.i_dat7 (i_dat7),

.o_dat0 (o_dat0),

.o_dat1 (o_dat1),

.o_dat2 (o_dat2),

.o_dat3 (o_dat3),

.o_dat4 (o_dat4),

.o_dat5 (o_dat5),

.o_dat6 (o_dat6),

.o_dat7 (o_dat7)

);

initial

begin

i_rst = 1;

i_clk = 1;

i_enable = 1;

#1000

i_rst = 0;

i_dat0 = 8'd170;

i_dat1 = 8'd160;

i_dat2 = 8'd150;

i_dat3 = 8'd140;

i_dat4 = 8'd130;

i_dat5 = 8'd120;

i_dat6 = 8'd110;

i_dat7 = 8'd100;

end

always #5 i_clk=~i_clk;

endmodule

00_003m4.完整算法代码文件

V

6159

6159

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?