本文主要是对《深入理解计算机系统》第6章存储层次结构的总结。

一、主存的访问

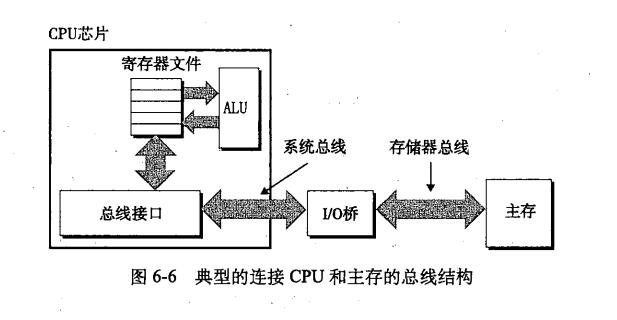

总线结构:

a. CPU执行读内存指令

movl A, %eax 地址A的内容被加载到寄存器%eax中。CPU芯片上称为总线接口(bus interface)的电路发起总线上的读事务。读事务由三个步骤组成的。首先,CPU将地址A放到系统总线上。I/O桥将信号传递到存储器总线。其次,主存感觉到存储器总线上的地址信号,从存储器总线读地址,从DRAM取出数据字,并将数据写到存储器总线。I/O桥将存储器总线信号翻译成系统总线信号,然后沿着系统总线传递。最后,CPU感觉到系统总线上的数据,从总线上读数据,并将数据拷贝到寄存器%eax。

b. CPU执行写内存指令

movl %eax, A 寄存器%eax的内容被写到地址A,CPU发起写事务。同样,有三个基本步骤。首先CPU将地址放到系统总线上。存储器从存储器总线读出地址,并等待数据到达。其次,CPU将%eax中的数据字拷贝到系统总线。最后,主存从存储器总线读出数据字,并将这些位存储到DRAM中。

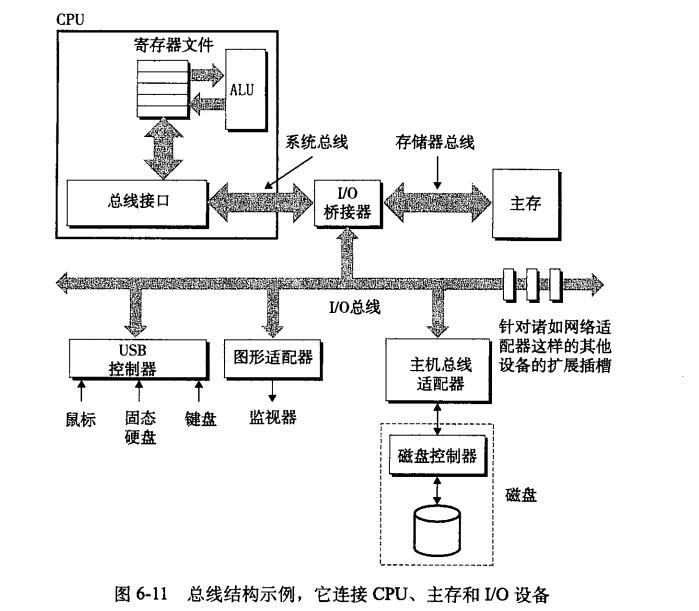

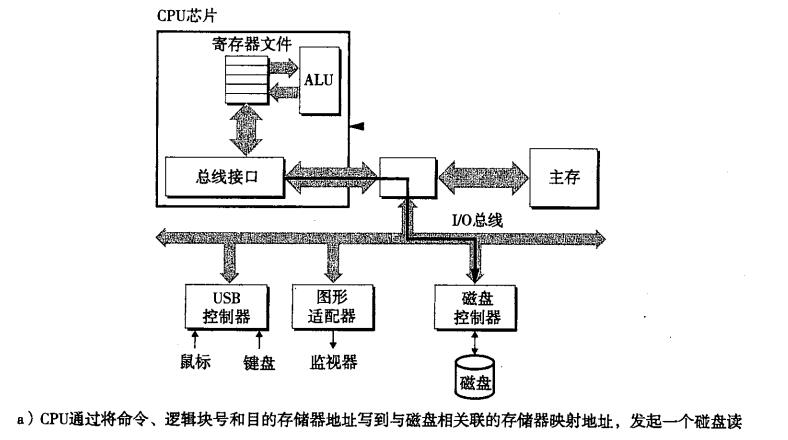

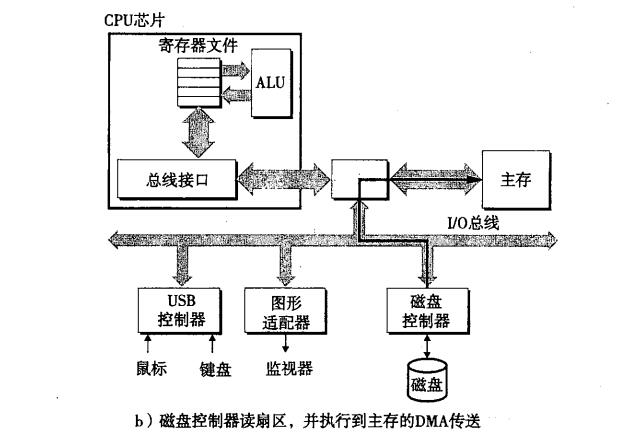

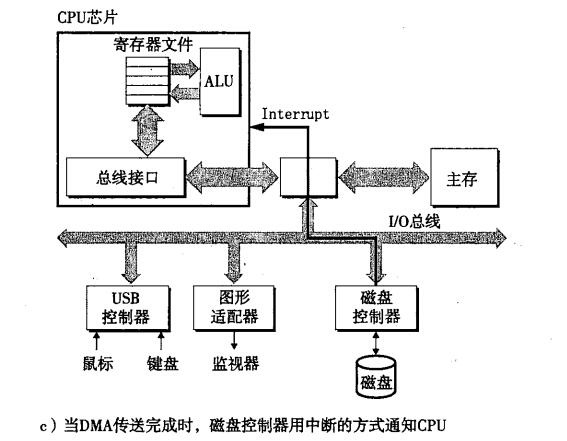

二、磁盘的访问

总线结构:

读一个磁盘扇区的流程:

(1).

(2)

(3).

三、局部性

a. 时间局部性

b. 空间局部性

c. 读数据和取指令的局部性

简单原则:

1). 重复引用同一个变量的程序有良好的时间局部性。

2). 对于步长位k的引用模式的程序,步长越小,空间局部性越好。具有步长位1的引用模式的程序具有很好的空间局部性。在存储器中以大步长跳来跳去的程序空间局部 性会很差

3). 对于取指令来说,循环有好的时间和空间局部性。循环体越好,循环迭代次数越多,局部性越好。

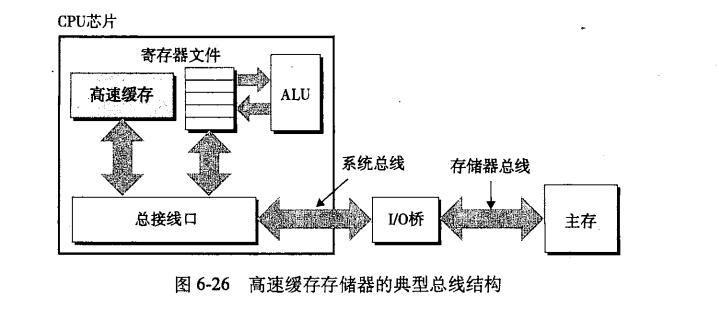

四、高速缓存

结构图:

编程时要充分利用时间和空间局部性原理。

1204

1204

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?