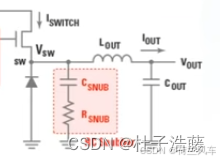

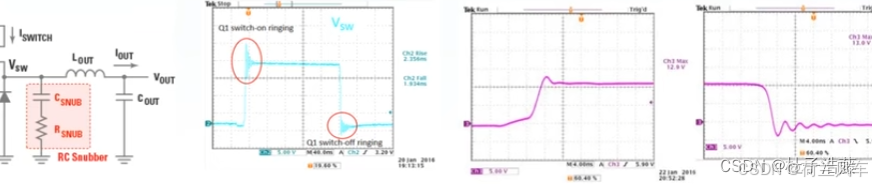

添加RC缓冲电路(上图红色线框住区域)可有效抑制振铃现象,但会增加开关切换损耗,降低效率。

RC缓冲电路应当放置在紧靠开关节点和功率地处。在使用外部MOSFET开关的Buck转换器中,RC缓冲电路应当直接跨过下桥MOSFET的漏极和源极放置。RC缓冲电路的串联电容需要足够大,以便让抑制电阻能在电路谐振期间表现出稳定的谐振抑制效果。如果这个电容的值太大,它在每个开关周期中的充电放电过程就会造成过大的功率消耗。所以的取值通常取电路寄生电容值的3~4倍比较好。

除了可以对谐振产生抑制,RC平滑抑制电路还可以轻微的降低开关切换波形上升和下降的速度。此外,对平滑抑制电容的充放电过程还会导致开关状态变换期间出现额外的开关切换电流尖峰,这会在低频区域引起新的EMMI问题。

当使用RC平滑抑制电路以后,要确保对电路的总功率损失进行检查。转换器的效率是必然会下降的,这在开关切换工作频率很高和输入电压很高时尤其明显。电容越大,效率越低。

缓冲电路RC值的确定:

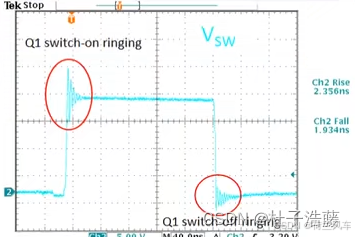

1、用示波器观察SW引脚与GND引脚之间的波形,测量上升沿尖峰谐振频率即原始振铃信号的频率

2、在SW与GND之间焊接一个电容(先不接电阻,电容最好用COG或者X7R),调整电容值,直到尖峰谐振频率降低到原来的二分之一左右。此时该电容值为产生尖峰电压的寄生电容值的三倍。最佳电容值可以通过尝试并联不同容量的电容来确定。最好从小容量电容开始(如100pF),然后逐渐增大。C的取值通常取电路寄生电容的4~10倍。使用更大的电容可以轻微降低电压过冲,但要以更多的功率耗散和更低的逆变效率为代价。

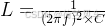

3、计算寄生电感值

用这个公式 算出寄生电感L的值。

算出寄生电感L的值。

F:就是上文说的原始振铃信号的频率

C:上文试出来的寄生电容值。

4、计算特征阻抗

特征阻抗:

L:寄生电感值。

C:寄生电容值。

5、选择合适的电阻和电容值,缓冲电路中的电阻值R接近上面的L,电容值C取寄生电容C的4~10倍之间。

选择好RC抑制电路的参数后,上升沿振铃情况明显好转;但下降沿没有什么变化。

Rboot对效率的影响比较小,但在负载很重的时候其影响会加大。

RC平滑抑制电路对效率的影响会比较大,特别是轻载和中等负载的情况下,但最大也就1~2%,处于可以接受的范围。特别注意,当Buck转换器的工作频率很高和输出电压很高的时候,RC平滑抑制电路对效率的影响会很大。

总结如何确定合适的缓冲电路RC值

1、 用示波器观察SW引脚与GND引脚之间的波形,测量尖峰谐振频率即原始振铃信号的频率 .

.

2、在SW与GND之间焊接一个电容(无电阻,仅电容),调整电容值,直到尖峰谐振频率降到原来的二分之一左右。此时,该电容值为产生尖峰电压的寄生电容值的3倍。

3、知道寄生电容值后,带入公式 求得寄生电感L。其中,L是寄生电感值,C是寄生电容值。

求得寄生电感L。其中,L是寄生电感值,C是寄生电容值。

4、再将寄生电容值和寄生电感值代入 算出来寄生阻抗Z。

算出来寄生阻抗Z。

5、最后就可以确认缓冲电路的RC值了,缓冲电路的电阻R应接近特征阻抗Z;电容值C取寄生电容的4~10倍。使用更大的电容可以轻微降低电压的过冲,但要以更多的功率耗散和更低的逆变效率为代价。

6、缓冲电路的电阻封装选择:

用公式 算出电阻功率,决定使用想要承受能力的封装。

算出电阻功率,决定使用想要承受能力的封装。

:缓冲电路的实际电容值(上面5、取定的值)。

:缓冲电路的实际电容值(上面5、取定的值)。

Vp 和Vn:改造后只有上升沿变化,用示波器看最大输入电压时,上升沿最大值Vp (一般直接取输入电压最大值),上升沿最小值Vn。

Buck转换器PCB布局设计要点:

1、在噪声敏感的应用中,最好选用小型封装的、电感低的晶圆倒装芯片。

2、确定开关切换回路的VIN和GND引脚位置,不同尺寸的输入电容要尽可能靠近这些节点,因为这个切换回路承载很高的电流变化率,所以面积要尽可能小。

3、将输出电容地放在不与输入电容切换路径发生重叠的位置,避免高频噪声串入输出电压中。

4、开关切换节点(SW)和BOOT引脚(BST)含有很高的电压变化率,可导致严重的电场辐射,因此其铜箔面积应当保持最小化,还要避开其他敏感电路.

5、转换器的小信号部分要与大功率的开关切换部分分开,其地线应当位于干净无噪声的地方,千万不要把输入端的电流信号和输入端的纹波电流引入其中。其实就是要把功率地PGND和模拟地AGND隔开。

6、不要再关键回路上使用热阻焊盘,它们会引入多余的电感特性。

7、使用地线层时,要尽量保持输入切换回路下面的地层的完整性。任何对这一区域地线层的切割都会降低地线层的有效性,即使是通过地线层的信号过孔也会增加其阻抗。

8、过孔可以被用于连接退耦电容和芯片的地到地线层,这可使回路最短化。但需要牢记的是过孔的电感量大约在0.1~0.5nH之间,这会跟据过孔的尺寸不同而不同,它们可增加总的回路电感量。对于低阻抗的连接来说,使用多个过孔是应该的。

9、要注意将地线层作为电流回流的路径会将大量噪声引入地线层,为此可将局部地线层独立出来,在通过一个噪声很低的点接入主地中。

10、当地线层很靠近辐射回路的时候,其对回路的屏蔽效果会得到有效的加强。因此,在设计多层PCB的时候,可将完整的地线层放在第二层,使其直接位于承载了大电流的顶层下面。

11、非屏蔽电感会生成大量的漏磁,它们会进入其他回路和滤波元件之中。在噪声敏感的应用中应当使用半屏蔽或全屏蔽电感,还要让敏感电路和回路远离电感。

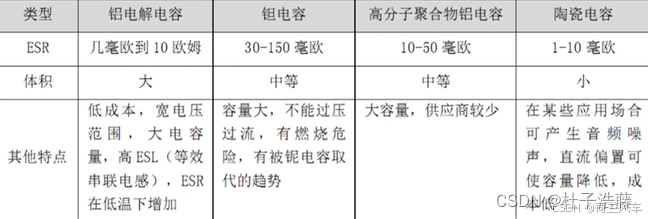

电容选型:

Cin输入电容:电解电容。(选ESR大的)

Cout输出电容:陶瓷电容(MLCC)、X7R、 固态电容。(选ESR小的)

小结:

主要学习了RC缓冲电路的作用,RC缓冲电路电阻电容值的计算,封装的选择以及PCB布线注意事项。

183

183

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?