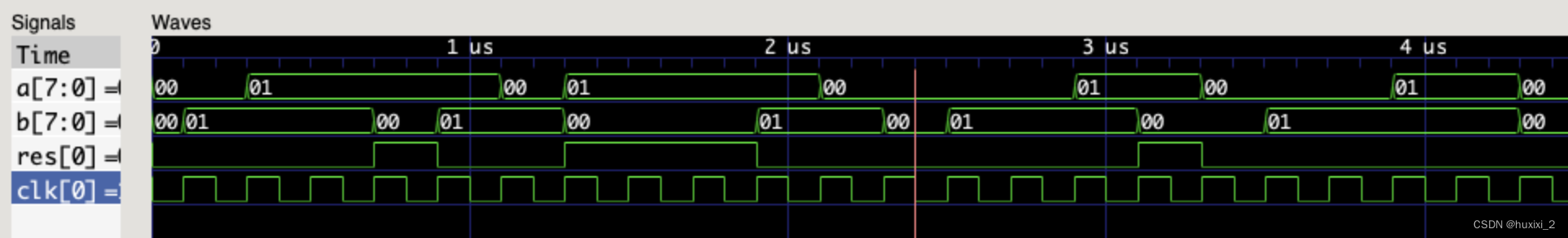

练习1

/*

输入两个八位的数据,比较大小,a>b输出高电平,否则输出低电平

*/

module compareG (

a, b, res

);

input [7:0] a, b;

output res;

assign res = (a > b) ? 1 : 0;

endmodule

测试:

`timescale 1ns/1ns

module t1(a, b);

output [7:0] a, b;

reg [7:0] a, b;

reg clk;

initial begin

a = 0;

b = 0;

clk = 0;

$dumpfile("wave.vcd");

$dumpvars(0, t1);

end

always #100 clk = ~clk;//生成时钟

always @(posedge clk) begin

a = {$random} % 2;

b = {$random} % 2;

end

initial begin

#100000 $stop;

end

compareG c(.a(a), .b(b));

endmodule练习2

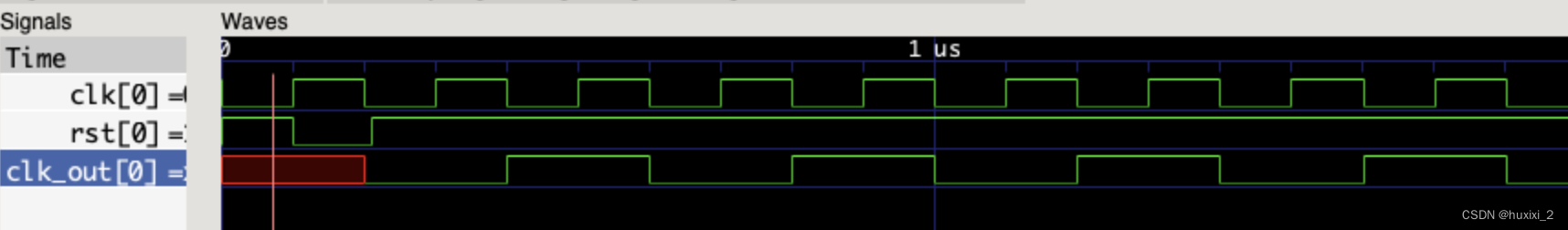

/*

二分频

*/

module half_clk (

clk_in, rst, clk_out

);

input clk_in, rst;

output clk_out;

reg clk_out;

always @(negedge clk_in) begin

if(!rst)

clk_out <= 0;

else

clk_out <= ~clk_out;

end

endmodule测试:

`timescale 1ns/1ns

module t2 (

clk, rst

);

output clk;

output rst;

reg clk;

reg rst;

initial begin

$dumpfile("wave.vcd");

$dumpvars(0, t2);

end

initial begin

rst = 1;

clk = 0;

#100 rst = 0;

#110 rst = 1;

#100000 $stop;

end

always #100 clk = ~clk;

half_clk h(.clk_in(clk), .rst(rst));

endmodule

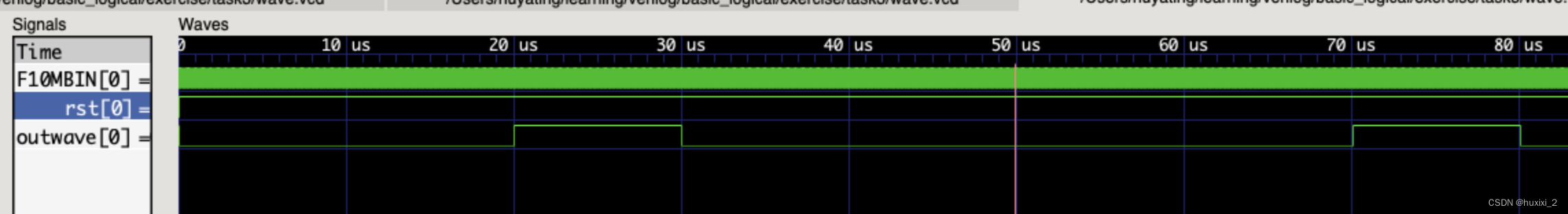

练习3

生成如下波形

/*

利用10MB时钟生成单周期波形:

20us低电平,10us高电平,20us低电平

第一个周期先20us低,

然后周期循环10us高,40us低

时间单位设置为1ns

10MB时钟一个周期是1/10/10^6 = 1*10^(-7)s 100ns

一个时钟周期有100个时间单位

半周期时间单位个数为50个

一个时钟周期是:100ns 0.1us

20us:200个时钟周期

10us 100个时钟周期

40us 400个时钟周期

单周期波形:200个周期反转一下;

之后一直100周期反转,400个周期反转

*/

module single_circle (

F10MBIN, rst, outwave

);

input F10MBIN;

input rst;

output outwave;

reg outwave;

integer i, times;

always @(posedge F10MBIN) begin

if(!rst) begin

outwave <= 0;

i <= 0;

times <= 0;

end

else begin

if(times == 0) begin

if(i == 199) begin

outwave <= ~outwave;

i <= 0;

times <= times + 1;

end

else

i <= i + 1;

end

else begin

if(i == 99) begin

outwave <= ~outwave;

i <= i + 1;

end

else if(i == 499) begin

outwave <= ~outwave;

i <= 0;

end

else

i <= i + 1;

end

end

end

endmodule测试:

/*

生成10MB波形测试single_circle

*/

`timescale 1ns/1ns

`define halfcircle 50

module t3 (

clk, rst

);

output clk, rst;

reg clk, rst;

initial begin

$dumpfile("wave.vcd");

$dumpvars(0, t3);

end

initial begin

clk = 0;

rst = 1;

#(`halfcircle - 10) rst = 0;

#20 rst = 1;

#(100000 * `halfcircle) $stop;

end

always #`halfcircle clk = ~clk;

single_circle st(.F10MBIN(clk), .rst(rst));

endmodule

练习4

八路选择器

/*

八路数据选通器

根据选择开关,从八路输入数据中选择一路输出

各路输入输出为4位

选择开关为3位

输入:

八路数据data

选择开关

输出:

选通的那路数据

*/

module select8_1 (

data1, data2, data3, data4, data5, data6, data7, data8, switch_select, data_out

);

input [3:0] data1, data2, data3, data4, data5, data6, data7, data8;

input [2:0] switch_select;

output [3:0] data_out;

reg [3:0] data_out;

always @(switch_select, data1, data2, data3, data4, data5, data6, data7, data8) begin

case (switch_select)

3'b000: data_out = data1;

3'b001: data_out = data2;

3'b010: data_out = data3;

3'b011: data_out = data4;

3'b100: data_out = data5;

3'b101: data_out = data6;

3'b110: data_out = data7;

3'b111: data_out = data8;

default: data_out = 4'bzzzz;

endcase

end

endmodule

测试:

/*

测试模块

*/

`timescale 1ns/1ns

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3063

3063

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?