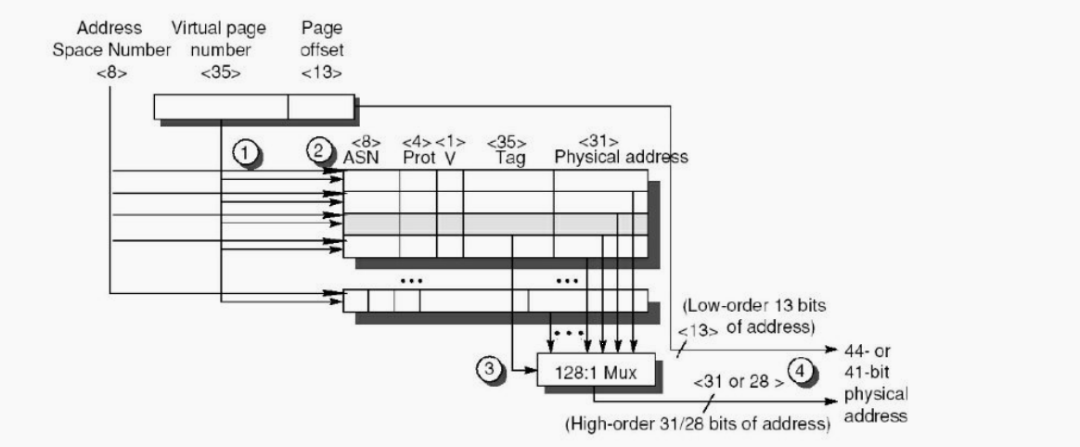

页表存在于主存中,每次内存访问都涉及两次或更多次内存访问(如果涉及多级页表)。每次内存访问将首先执行page table walk,然后执行实际的内存访问,这个代价可能是相当昂贵的。可以通过向页表添加cache(Transation Lookaside Buffers或TLB)来降低此成本。下面显示了一个128项TLB示例。

要执行页面翻译(VA2PA),将首先查找TLB。如果页不在TLB中,则涉及page table walk。

与常规cache不同,从VA到PA的空间相关性很少或根本没有,因此TLB通常是全相联的。

如何处理TLB未命中(miss)?

要翻译的页面可能不在TLB中。通常有两种方法来解决TLB miss

1.软件的方法。TLB错误可能导致中断,操作系统将介入检查页面表并更新TLB。

2.硬件的方法。需要使用称为内存管理单元 (Memory Management Unit,MMU)的特殊硬件来执行主存中的page table walk和更新TLB。

如何处理页面错误(page fault)?

当页不在主存中时,可能会发生page fault。如果发生page fault,则必须首先通过从磁盘进行IO读取将页表条目带入主存。

需要记住的一点是,不管TLB错误是如何处理的,page fault总是由操作系统来处理的。

1442

1442

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?