内存控制器执行地址映射。假设我们正在映射由8个bank组成的DDR SDRAM芯片,每个bank有8个DRAM阵列(位宽),大小为4096行,1024列。

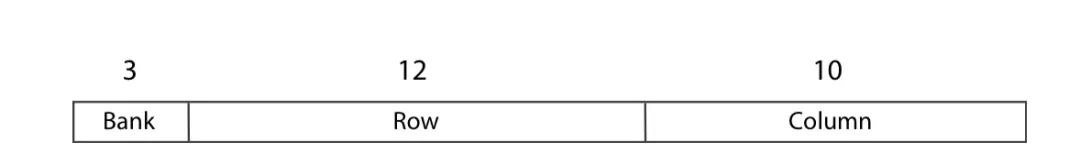

要映射这样的DDR SDRAM芯片,我们需要行地址12位,bank地址3位,列地址10位。

上图显示了地址映射的最直接的方式,其中顶部地址位用于寻址bank,中间12位用于寻址行,最后10位用于选择列。这种简单的地址映射的主要问题是连续行在同一bank中;因此,没有bank交错。对于由多行组成的连续内存传输,当前打开的行应先precharge,然后再打开新行。

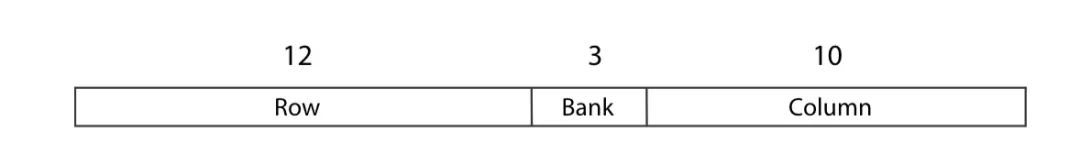

地址映射的更好方法是使连续行位于不同的bank中。通过这种方式,我们可以在当前访问的行precharge之前打开一个新行。所以,precharge时间是被藏住了。上图显示了使用bank交错的地址映射。现在,顶部地址位选择行,而中间地址位选择bank。每次到达一行的结尾时,都会访问不同bank中的同一行。

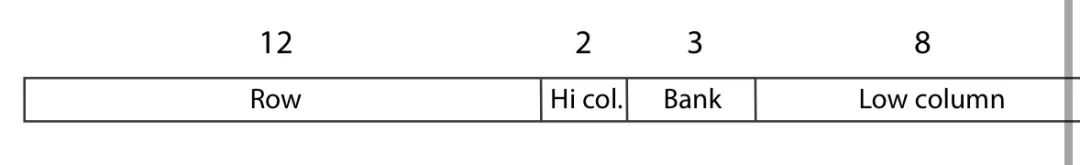

地址映射的第三种方式是考虑cache。通常,cacheline 的大小为64字节。在现实中,内存读取或写入具有局部性的。如果使用cache来支持数据的局部性,CPU将访问连续的cacheline。因此,读写将发生在内存中的连续64字节上。例如,如果cacheline存储在同一bank同一行的最后64字节中,则下一个cacheline上的cache miss将需要预先为该行precharge然后再打开一个新行。因此,最好将连续的cacheline放入不同的bank——这被称为cacheline交错。上图,列bit被分成两部分。低列bit选择cacheline。剩余的高列位选择不同bank的cacheline。

1087

1087

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?