集成电路设计领域正面临严峻的现实问题。可能只有20%的ASIC芯片在首次流片中取得成功。

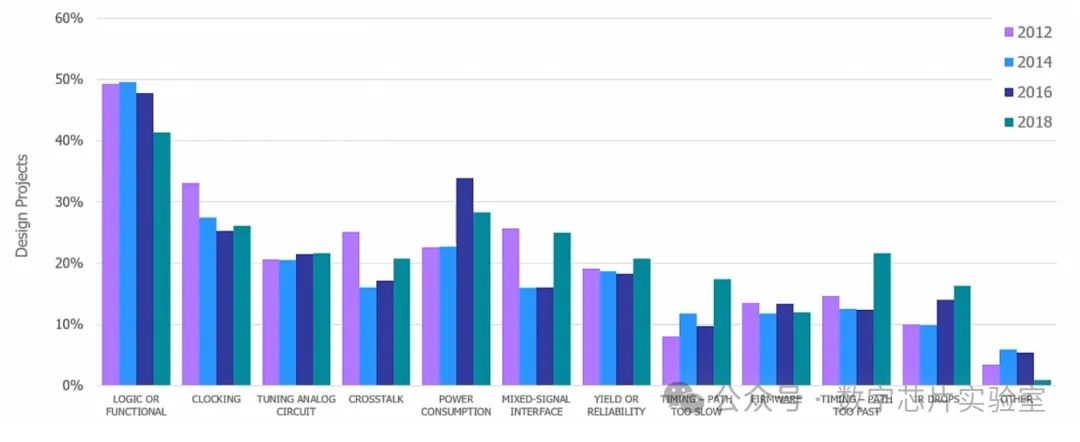

失败率高的一个重要原因是新工艺节点带来的挑战尚未被完全理解。虽然一些长期存在的问题已经被集成到设计工具和流程中,但数模混合信号接口、串扰、时序和电压降等问题仍然是造成重新流片的主要原因。

下图清晰地展示了不同类型的ASIC缺陷对重新流片的影响,包括逻辑或功能问题、时钟问题、时序分析等。

有些芯片失败是因为设计流程过于随意,有的芯片失败不一定是因为功能问题。如果硅片返回后运行速度比预期慢10%,或者功耗比预期大10%,在市场上可能就没有竞争力了,也就需要重新流片

大家普遍会关注功能问题和时序问题,但是电源问题也很重要。

随着芯片集成度提高,片上电源成为一个越来越大的挑战。电压裕量的精确建模和最小化对于平衡能效和稳定性至关重要。有些公司会冒险推进设计,即使发现了问题。公司甚至在知道存在严重IR压降问题的情况下仍然进行流片,因为对他们来说,进度比完美更重要。

越来越多的问题变得相互关联。例如,电源、IR压降、热管理、时序和电迁移都有联系,但目前大多数分析还是分开进行的。

电源噪声会导致电压供应下降,相同的cell在不同位置可能会因电压降低而导致时序延迟,最终导致功能问题。

复杂性导致更高的功率密度,进而产生芯片内的局部热点。增加的cell密度也导致供电电压下降更严重。高精度温度传感器和电压监控器可以帮助系统管理和适应这些条件,提高可靠性并优化性能。

这些问题在数据中心和AI设计中尤为显著,因为此时高性能需求给温度和电压管理带来了巨大压力。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?