文章转载于https://baijiahao.baidu.com/s?id=1735139898060343586&wfr=spider&for=pc

芯片行业对于流片都不陌生。

所谓流片,就是像流水线一样通过一系列工艺步骤制造芯片,该环节处于芯片设计和芯片量产的中间阶段,是芯片制造的关键环节。

简单来说就是将设计好的方案,交给芯片制造厂,先生产几片几十片样品,检测一下设计的芯片能不能用,然后进行优化。如果测试通过,就按照这样开始大规模生产了。

**所以为了测试集成电路设计是否成功,必须进行流片。**这也是芯片设计企业一般都在前期需要投入很大成本的重要原因。

一颗芯片从设计到量产,流片属于非常关键的环节。当芯片完全设计出来以后需要按照图纸在晶圆上进行蚀刻,采用什么样的制程工艺,多大尺寸的晶圆,芯片的复杂程度都会影响这颗芯片的流片成功率和成本,而且许多芯片都不是一次就能流片成功的,往往需要进行多次流片才能获得较为理想的效果。

但流片是一件非常烧钱的事,多几次流片失败,可能就会把公司搞垮。2019年就曾传出小米旗下松果电子的澎拜S2系列芯片连续5次流片失败,设计团队重组的惨痛案例。

有芯片大厂算过这笔账,14nm工艺芯片,流片一次需要300万美元左右,7nm工艺芯片,流片一次需要3000万美元,5nm工艺芯片,流片一次更是达到4725万美元。可见,流片对于芯片设计企业来说是一笔巨大花费,尤其是对于行业中小企业来讲,实际流片的价格比大厂又高很多,让本不富裕的“生活”更是雪上加霜。

流片为什么这么贵?

那芯片流片的价格为什么这么贵?

这就要提到芯片的制造原理了。

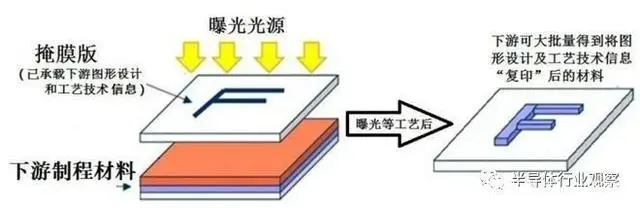

芯片制造要在很小的芯片里放上亿个晶体管,制造工艺已经到了纳米级,只能用光刻来完成。光刻就是用光刻出想要的图形,光刻需要用到掩膜版(又称光罩,Mask),掩膜版就是把设计好的电路图雕刻在上面,让光通过后,在晶圆上刻出图形。

流片贵,一方面是因为刚开始有许多工艺需要验证,从一个电路图到一块芯片,检验每一个工艺步骤是否可行,检验电路是否具备所要的性能和功能。芯片流片过程至少持续三个月(包括原料准备、光刻、掺杂、电镀、封装测试),一般要经过1000多道工艺,生产周期较长,因此也是芯片制造中最重要最耗钱的环节。

如果流片成功,就可以据此大规模地制造芯片;反之,就需要找出其中的原因,并进行相应的优化设计。

其中,**芯片流片贵,主要贵在掩膜版和晶圆,这两项价格不菲且都是消耗品,其中掩膜版最贵,**一套中端工艺制程的掩膜版价格大约在50万美元左右,而一片晶圆的价额也在数千美元。

掩膜贵还是晶圆贵?

掩膜版是一种由石英为材料制成的,是微电子制造过程中的图形转移工具或母版,其功能类似于传统照相机的“底片”,根据客户所需要的图形,通过光刻制版工艺,将微米级和纳米级的精细图案刻制于掩膜版基板上,是承载图形设计和工艺技术等内容的载体。

然后把这种从掩膜版的图形转换到晶圆上的过程,想象成印钞机的工作流程。把光刻机想象成印钞机,晶圆相当于印钞纸,掩膜就是印版,把钞票母版的图形印到纸张上的过程,就像光刻机把掩膜版上的芯片图形印到晶圆上一样。

光刻需要用到掩膜版,掩膜版就是把设计好的电路图雕刻在上面,让光通过后,在晶圆上刻出图形。

掩膜版的质量会直接影响光刻的质量,掩膜版上的制造缺陷和误差也会伴随着光刻工艺被引入到芯片制造中。因此,掩膜版是下游产品精度和质量的决定因素之一。

掩膜版的价格主要取决于芯片所选用的“工艺节点”,工艺节点越高、流片价格就越贵。这是因为越先进的工艺节点,所需要使用的掩膜版层数就越多。据了解,在14nm工艺制程上,大约需要60张掩膜版,7nm可能需要80张甚至上百张掩膜版。

掩膜版层数多了,不仅仅是因为掩膜板的价格贵,还因为每多出一层 “掩膜板”,就要多进行一次“光刻”,就要再多涂抹一次 “光刻胶”,就要再多一次 “曝光”,然后再来一次 “显影” …,整个流程下来耗费的成本就大大增加了。

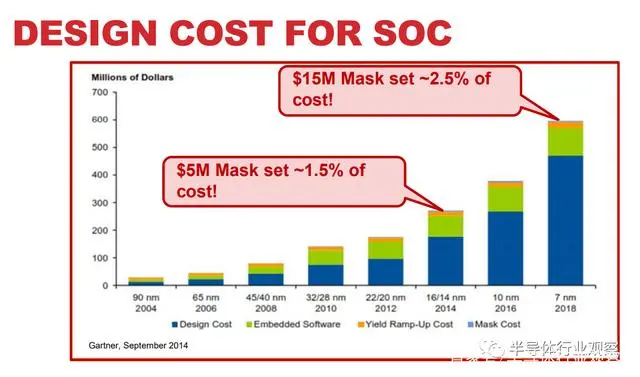

据IBS数据显示,在16/14nm制程中,所用掩膜成本在500万美元左右,到7nm制程时,掩膜成本迅速升至1500万美元。

7nm制程中,掩膜成本大概为1500万美元(图源:IBS)

掩膜版的总体费用,包括石英,光刻胶等原材料的成本,Mask Writer和Inspection等机台的使用成本,另外还有掩膜版相关数据的生成,包括OPC、MDP等软件授权、服务器使用和人工开发成本等等。对于一款芯片,动辄几十层的掩膜版,需要如此多的步骤,设备、软件、人员缺一不可,费用自然昂贵。

在流片中,Mask的费用更是占很大一块,是因为前期流片阶段就是生产5-25片作为产品验证用的,主要成本是Mask成本。对应的,正式生产时,Mask的费用只算一次,后面有大量的晶圆可以分摊成本,自然就便宜了。

准确的说应该是平均到每一颗芯片上的费用便宜了,而不是总的流片费用便宜了。

据业内人士透露,某晶圆代工厂(Foundry) 40nm的流片成本大概在60-90万美元。Mask占据大头,大约60-90万美元;晶圆成本每片在3000-4000美元左右。

所以,如果生产10片晶圆,每片晶圆的成本是(90万+ 400010)/10=9.4万美元;但是如果生产10000片晶圆,那么每片晶圆的成本是(90万+400010000)/10000=4090美元。

可见,进入量产之后,生产上万片晶圆,每片晶圆可能3000-4000美元左右,Mask的成本平摊到每片晶圆以后就很少了,这时候晶圆的成本就是主要的成本来源。所以,如果只是量小的流片阶段,那么Mask成本是主要的。反之如果量产很多,那么则是晶圆主导成本。

另外,半导体制造厂的机台便宜的上百万美元,贵的上亿美元。据了解,28nm的Mask机台就超过5000万美元一台,这些仪器,机台需要七年折旧完毕。也就是说,大概使用一年就要损失14%的机台价值。

晶圆代工行业设备折旧年限通常是5-7年。据报道,中芯国际2019年折旧费用超过了14亿,主要是因为先进制程的投入需要购置部分单价较高的机器设备,使得折旧费用逐年增加。台积电2021年折旧费用更是达到近千亿新台币,创史上最高。

从工艺研发周期来讲,机器的成本和折旧费已然很高,但将工艺的良率及可靠性调到量产要求也是一项有挑战的工作。(据悉某厂搞28nm,机器2011/2012年就全部到位了, 可是5、6年后良率都还没调到严格的量产标准,可见有多难。同时还白白损失了多年的设备折旧费用。)

其次还有人力成本,维护成本以及耗材费等,这些都是Mask成本高的原因。

据etnews报道,随着当前供需状况恶化,掩膜版的价格还在上涨,交货时间也一再被推迟,即使支付额外费用,也很难及时购买到。通常需要4-7天的交期最近增至14天,部分企业的交期延长到了原来的7倍。

此外,为了跟上摩尔定律,Foundry升级换代所需的设备和技术研发的投资不断增大,由于Foundry对先进生产线的投资巨大,必然会将其成本转嫁到客户的投片费用上。这也导致了制造芯片的费用在不断上涨。

如何降低流片成本?

上述种种因素影响下,芯片流片费用成为摆在设计企业面前的一个难题。那么,面对流片价格高的问题,有没有什么办法来降低成本?

摩尔精英资深总监王龙向笔者表示,MPW (Multi Project Wafer) 就是一种可以帮助设计企业降低成本的流片方式。MPW是指由多个项目共享某个晶圆,同一次制造流程可以承担多个IC设计的制造任务,将多个使用相同工艺的集成电路设计放在同一晶圆上流片,制造完成后,每个设计可以得到数十片芯片样品,这一数量对于原型设计阶段的实验、测试已经足够。

通俗来讲就是几家公司或机构一起购买一套掩膜版,然后生产出来的同一片晶圆上会同时存在有好几款芯片,待晶圆切割后,再把各自的芯片“领回家”。而该次制造费用就由所有参加MPW的项目按照芯片面积分摊,极大地降低了产品开发风险。

据王龙介绍,MPW有一定的流程,通常由晶圆代工厂或者第三方服务机构来进行组织,各种工艺在某一年之中的MPW时间点是预先设定好的,通常是越先进的工艺,安排的MPW频率越高。晶圆代工厂事先会将晶圆划好多个区域并报价,各家公司根据自己情况去预订一个或多个区域。

这对参与者来说,在设计和开发方面有一定的进度压力。但是相比之下,MPW带来的好处是显而易见的,采用多项目晶圆能够降低芯片的生产成本,为设计人员提供实践机会,并促进了芯片设计的成果转化,对IC设计人才的培训,中小设计公司的发展,以及新产品的开发研制都有相当大的促进作用。

对比来看,共享Mask的好处就是省钱,但是可能要等代工厂的时间节点,需要更多的时间。对于那些不差钱或赶时间的企业当然可以自己利用一套Mask(Full- Mask,全掩膜),制造流程中的全部掩膜都为自己的设计来服务,通常用于设计定型后的量产阶段。机器一响,黄金万两。

但是,在当前产能严重紧缺的情况下,代工厂面对不同客户的产品需求、竞争优势、市场前景和计划等态度是完全不同的,代工厂会综合考虑客户下单量,后续下单稳定性以及产品所面向的市场前景来做判断。

实际上,对于大部分的中小企业来说,除了价格以外,在流片或量产环节还面临着包括产能、交期在内的诸多挑战:

-

1.对Foundry体系不了解,缺乏工艺选型的经验和Foundry打交道的经验;

-

2.主流Foundry准入门槛高,新兴玩家难以申请预期的工艺或支持,沟通成本高;

-

3.缺乏系统的供应链管理能力,尤其在量产产能爬坡阶段,对产能、交期、质量过于乐观;

-

4.产能紧缺情况下,缺乏备货机制,恐慌性下单或有了订单再下单导致产能跟不上市场需求。此外,交期的变化、产能的波动都会大大增加初创公司与晶圆代工厂的沟通成本,降低效率。

对此,中小芯片设计企业可以寻求有资源、有实力、有经验的第三方运营服务机构进行合作,一同来解决遇到的供应链难题。

以摩尔精英流片业务为例,可以提供完整的工艺平台,对接数十家主流晶圆代工厂,提供MPW、Full-mask及量产在内的不同工艺节点的流片服务,能够显著降低客户的商务成本和沟通成本。

另一方面,凭借自建的专业流片FAE团队,不仅为合作晶圆代工厂提供长尾客户的高效支持管理,也帮助中小公司的产品快速得到支持,协助客户选择最优工艺,并保障客户的数据安全。

在产能方面,利用摩尔精英的know-how协助中小客户去争取产能(包括大订单、订单量趋势、提前排队、及时跟踪产能动态等),帮助客户降低成本和缩短芯片研发周期。

综合来看,无论是从技术、商务还是产能方面,选择一家靠谱的第三方机构都可以协助设计公司解决当前所遇到的供应链难点,提供最优解。

总而言之,处于这些需求赛道中的公司们都可能从流片服务厂商的业务中获利。

写在最后

一个芯片开发项目,需要经历从产品定义、设计、验证仿真一直到最终流片的漫长过程,而作为“终极大考”的流片,此前漫长过程中的任何一个小疏忽都可能导致流片失败,而一旦流片失败往往意味着企业将面临数千万美元起的损失和至少半年市场机遇的错失。

这对于许多企业而言,流片失败是无法承受之痛。

对此,芯片设计企业、制造商以及相关的行业服务平台和机构应紧密合作,优势互补,携手解决困扰开发者的“流片难题”。

来源:内容由半导体行业观察(ID:icbank)原创

作者:李晨光

本文探讨了芯片流片价格昂贵的原因,主要包括掩膜版和晶圆的成本,以及流片过程中复杂的工艺和高风险。掩膜版价格昂贵,且与工艺节点相关,而晶圆成本在量产时才会大幅下降。为了降低成本,多项目晶圆(MPW)共享掩膜版成为一种解决方案,但同时也存在时间安排和产能挑战。流片对于芯片设计企业来说是一笔巨大的投资,尤其是在当前产能紧张的情况下,寻找合适的合作伙伴和流片服务至关重要。

本文探讨了芯片流片价格昂贵的原因,主要包括掩膜版和晶圆的成本,以及流片过程中复杂的工艺和高风险。掩膜版价格昂贵,且与工艺节点相关,而晶圆成本在量产时才会大幅下降。为了降低成本,多项目晶圆(MPW)共享掩膜版成为一种解决方案,但同时也存在时间安排和产能挑战。流片对于芯片设计企业来说是一笔巨大的投资,尤其是在当前产能紧张的情况下,寻找合适的合作伙伴和流片服务至关重要。

718

718

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?