时钟门控(Clock Gating)是一种在数字IC设计中某些部分不需要时关闭时钟的技术。这里的“部分”可以是单个寄存器、模块、子系统甚至整个SoC。

为什么需要时钟门控:大多数SoC都是power constrained,mobile端不能够充更多的电就只能尽可能地降低功耗了(无法开源只能节流呀),也因为时钟门控是降低芯片动态功耗最简单,最常用的方法之一。

时钟门控技术分类:通常,有两种不同的时钟门控实现技术。

combinational clock gating–这种类型的时钟门控由工具在综合时自动识别引入。

sequential clock gating –这种类型的时钟门控作为功能的一部分引入RTL设计中。通常时钟门控策略在系统架构中定义,然后由设计人员进行实现。

combinational clock gating

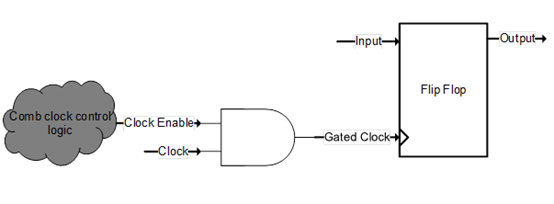

最简单的combinational clock gating可以通过AND门实现,如下图所示

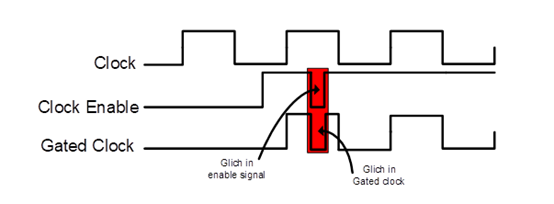

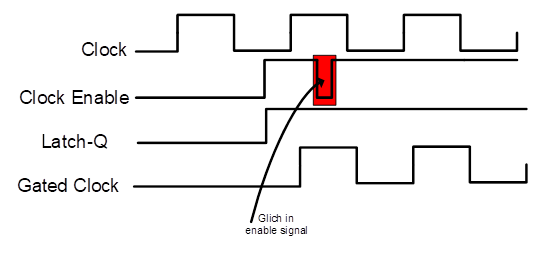

当enable为1时,时钟会传给寄存器FF;当enable为0时,时钟将被关闭, FF将不起作用。这种最简单的时钟门控技术形式存在一些问题,即在提供给FF的时钟中产生毛刺。

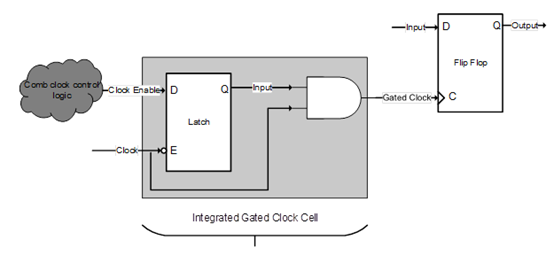

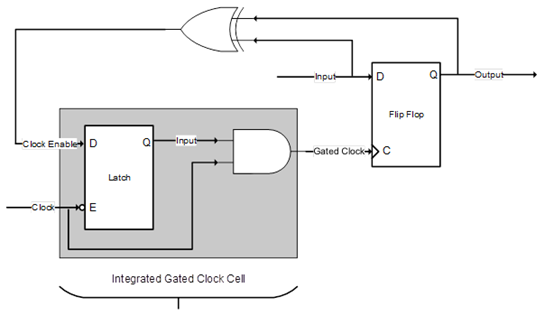

可以通过在时钟使能信号的输出端引入一个低电平敏感的锁存器来解决这个问题。

锁存器输出仅在时钟低电平内更新,因此与门的输入将稳定为高。

Integrated Gated Clock Cells(ICG Cell)

要实现这种时钟门控可以实例化标准单元库中的两个Cell(Latch和AND门),秉着不重复造轮子的思想以及方便工具进行后续的时序分析更建议使用库中的ICG Cell并且由工具自动综合插入。

时钟使能信号可以由软件控制和硬件同时控制,即由软件控制是否需要启动时钟门控,硬件动态控制时钟使能。

软件控制示例如下:

软件控制这个全局时钟使能信号,为低电平时不打开时钟门控,这种全局时钟门控使能策略可以进行层次化的设计,从系统级到最终的单个寄存器。

硬件控制示例如下:

XOR门的输入连接到FF的输入和输出。如果FF的输入和输出相同,则无需触发FF,此时可对时钟进行门控。

在前端RTL级引入combinational clock gating很简单,没有对逻辑功能产生影响,可以由EDA工具自动插入。但是在物理设计的视角,这可能是一个更大的课题,因为我们引入了一个实实在在的物理cell,更何况还是在时钟路径上。

从时序功耗上, clock gating应该离寄存器时钟端远还是近?

从面积功耗上,只有一个寄存器是否应该被门控?

sequential clock gating

除了上述combinational clock gating外,还有sequential clock gating,这涉及对RTL设计中多个时钟周期进行深入分析。当然基本思想也很简单,如果寄存器X在周期C中未更新,并且在时钟周期C + 1中输入给寄存器Y的D端,则无需在周期C + 1中使能寄存器Y的时钟。

1001

1001

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?