前言

同步以太网是一种采用以太网链路码流恢复时钟的技术, 简称SyncE。同步以太网通过以太网物理层芯片从串行数据码流中恢复出发送端的时钟,从而实现网络时钟同步。IEEE1588 协议,又称 PTP( precise time protocol,精确时间协议),可以达到ns级别时间同步精度,于 2002 年发布version 1,2008 年发布 version 2。

时钟难题

某知名国际组织开大会,会议主席提前三个月写信给各成员,通知准时参加,到了会议日期,与会代表一个也没有到,三天后,有参会代表陆续抵达,又过了半个月,终于又陆续到了两位代表,还有一位代表一直没有露面,会议主席再次写信跟未参会这位代表确认,原来,那家伙压根就没有收到上一封邮件!

为此,会议主席跟各代表确认迟到原因,主要分为以下几点:

1、时间不一致,会议主席通知时间和当地代表当地时间存在固定偏差;

2、代表手表存在偏差,有的代表的手表高级,精度高,有的代表的手表每天要慢半小时;

3、路上耽搁时间不一致,有的需要走三天,有的需要走五天,更久的需要走上半个月,代表出发之前没有经验,根本不知道会不会迟到,要迟到多久;

时间同步问题

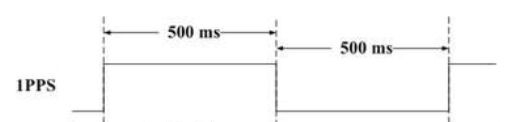

Ø 1pps(Pulse Per Second)相关概念

为了避免下次参会,各代表时间不一致问题,会议主席提议,他以后会在固定时间给各成员代表寄一个空信封,用于大家调整各自的时间。

各成员代表收到信件之后,打开一看,靠,时间好像又不准了,重新校准一下手表表盘刻度,这像极了同步以太网通过GPS卫星发送的1PPS时钟;

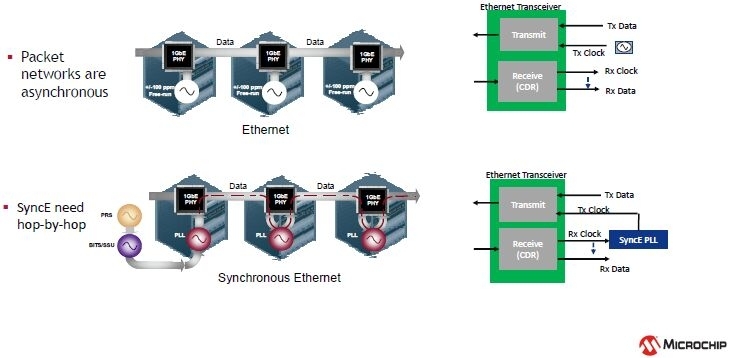

Ø SyncE同步原理

会议主席后来变懒了,觉得每次都发空信封,太浪费资源,不是反正都要定时不定时的给各成员国写信吗?算了,信件里面顺便夹带频率信息,让各成员自己去提取,顺便也可以发布一些会议日程,这样,大部分与会代表都会在会议前后到达会议现场。

接收端通过以太网获取数据包信息,经过锁相环做CDR(时钟信号恢复),提取到比较准确的时钟频率,解锁出来做本地时钟,节约资源、而且准确,这就是SyncE。

SyncE和异步通信最大的区别,就是利用锁相环提取通信链路的时钟,可以轻松实现频率同步。

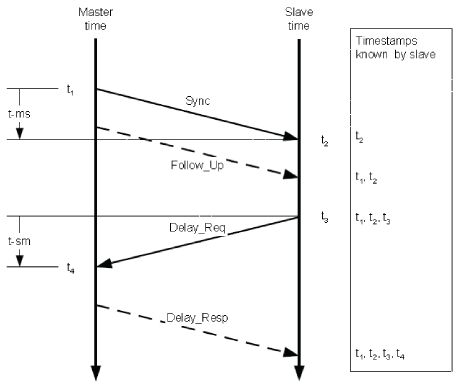

Ø IEEE1588-PTP

为了提高效率,会议主席希望各个代表,最好能准时参会,不用为等人而拖拉,找了一帮人出主意,问他们,有没有办法让与会代表准时参会,这些人提了好几个方案,比如用直升飞机运输,开通专列,提前半年集合,都被一一否决,最后,一个代号1588的咨询机构站出来说,你不是经常要跟他们写信吗?寄信的时候,信封上盖个戳,让他们回信的时候再盖个戳,你收到信再回他确认一下,让他重新确认给你,这样,掐指一算,来回时间和中途空档期,应该完全算计得出来,会议主席一听,嗯,这个馊主意(好主意)不错,就这么干。

寄信的时候,啪,打一个戳,收件打一个戳,回复再打一个戳,加上延时,如此往来,就通过这几个时间差,很容易就知道收发的时间偏差,以及开销,拿这个来做IEEE1588 PTP精确时间同步,相当顺手。

Microchip时钟解决方案

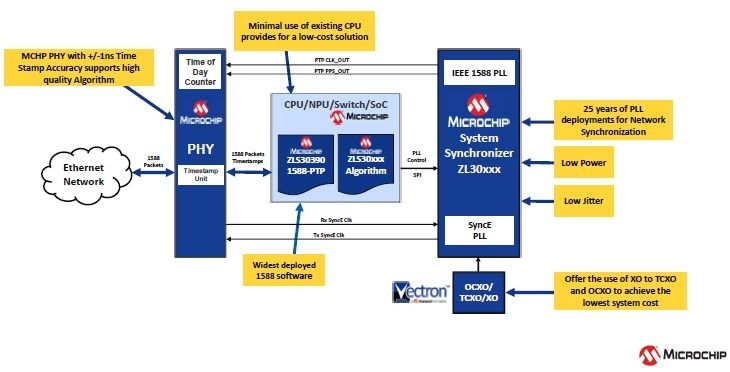

基于以上众多时钟难题,Microchip专注于通信领域,对于5G通信技术,Microchip帮你提供一揽子解决方案,通俗来说,这就是一个闭环自动控制系统,Microchip可以提供时钟(包括晶振、去抖和锁相环)、PHY,IEEE1588 PTP协议IP,只需一招,让你轻松搞定。

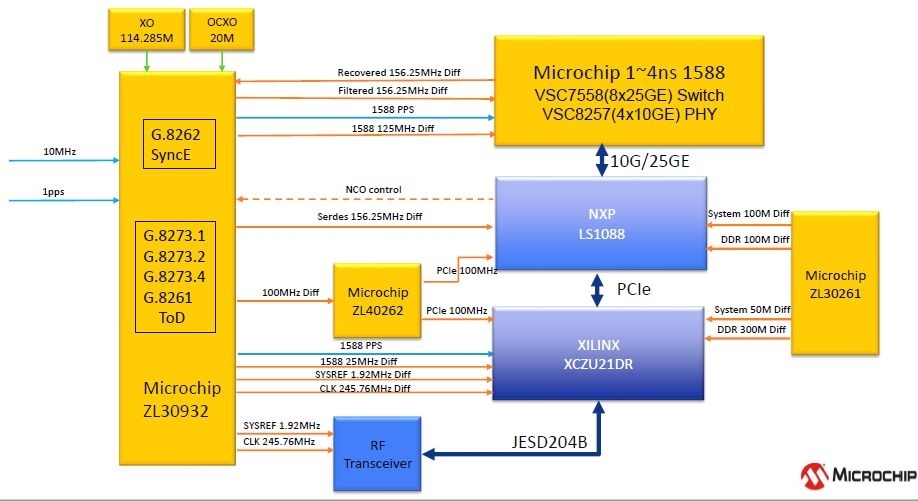

小道消息,Microchip正和世界知名大厂合作,把他们的TCG和ENT打包做到他们的解决方案中,据传,Microchip已经和Intel、Xilinx和NXP建立合作,已经成功完成5G小基*参考设计,小狼目前只整理到一家的参考方案,供大家参考,后续有进一步的消息,小狼将会继续为你更新上传。

路边社小狼,在搬砖的路上为你追踪报道。

---------------------

作者:wolfe_yu

链接:https://bbs.21ic.com/icview-3142058-1-1.html

来源:21ic.com

此文章已获得原创/原创奖标签,著作权归21ic所有,任何人未经允许禁止转载。

---------------------

作者:wolfe_yu

链接:https://bbs.21ic.com/icview-3142058-1-1.html

来源:21ic.com

此文章已获得原创/原创奖标签,著作权归21ic所有,任何人未经允许禁止转载。

本文通过比喻解释了同步以太网(SyncE)和IEEE1588(精确时间协议,PTP)的工作原理,如何解决网络中的时钟同步问题。SyncE通过以太网数据包恢复发送端时钟,实现频率同步,而PTP利用时间戳进行精确时间同步。此外,文中还提及Microchip提供的通信时钟解决方案,适用于5G通信技术。

本文通过比喻解释了同步以太网(SyncE)和IEEE1588(精确时间协议,PTP)的工作原理,如何解决网络中的时钟同步问题。SyncE通过以太网数据包恢复发送端时钟,实现频率同步,而PTP利用时间戳进行精确时间同步。此外,文中还提及Microchip提供的通信时钟解决方案,适用于5G通信技术。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?