1、PCIE bifucation 是什么

Bifucation在汉语中指的是分叉的意思。简单理解,PCIE device支持bifucation特性指的是此pcie device可以同时对接多个不同的pcie设备。本文以intel FPGA SPEC文档为例,讲解bifucation特性。下文将讲解,一个16lane的pcie IP在不同的模式下,可以连接1个、2个和4个pcie设备。

2、支持bifucation特性的PCIE IP

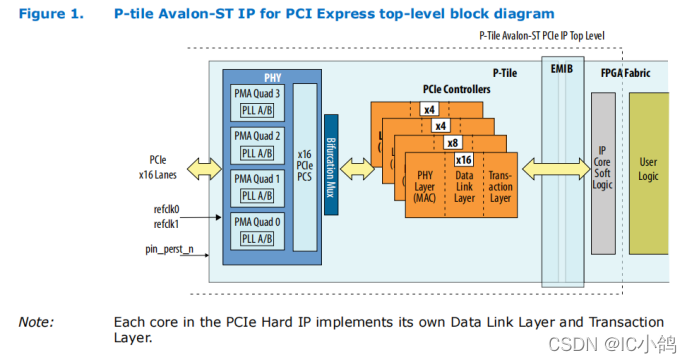

The P-tile Avalon-ST IP for PCI Express consists of the following major sub-blocks:

• PMA/PCS

• Four PCIe cores (one x16 core, one x8 core and two x4 cores)

• Embedded Multi-die Interconnect Bridge (EMIB)

• Soft logic blocks in the FPGA fabric to implement functions such as VirtIO, etc.

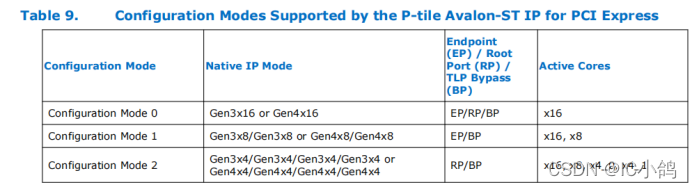

如图1,所示,当前PCIE支持bifucation特性,能够同时对接多个PCIE设备,支持的模式如表9:

bifucation特性说明:

In Configuration Mode 0:工作在x16 模式,只有x16 core 处于活跃状态,只有一组接口暴露给用户

In Configuration Mode 1: the x16 core and x8 core均处于活跃状态,工作状态组合是:2个Gen3 x8 cores或者 2个 Gen4 x8 cores. NOTE:不支持 1个gen3 core + gen4 core

In Configuration Mode 2: 4个 cores (x16, x8, x4_0, x4_1) 均处于活跃状态, 工作状态组合是:

4个 Gen3 x4 cores 后者 4 Gen4 x4 cores.

注意:每个core都拥有一套与用户逻辑对接的接口,因此在mode0模式下,只有一套活跃的接口,在mode1模式下,有两套活跃接口。

NOTE: x16的core也能作为一个x4 core 或者x8 的core使用;x8的core也能作为一个x4 core 使用;

bifucation特性所需的硬件支持:

从图1,可以看到,bifucation特性需要需要相应的硬件支持:

- 共享的16lane的PHY(其中的PMA和PCS是共享逻辑)

- 一个bifucation mux(用于静态配置模式)

- 独立的pcie control

- 每个control包含PHY layer(仅有MAC层)

- 每个control包含 Data link layer

- 每个control包含 transaction layer

参考文档:

P-Tile Avalon Streaming Intel FPGA IP for PCI Express User Guide (公开文档,可以在intel官网下载)

2814

2814

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?