Jpeg Encoder ip

jpeg编码器:

支持YCbCr422输入,422格式输出

每路数据为8bit

支持可编程量化表

纯verilog代码,方便移植到任何FPGA平台

使用vcs进行仿真

ID:341580699188634792

咸鱼_RTL猿

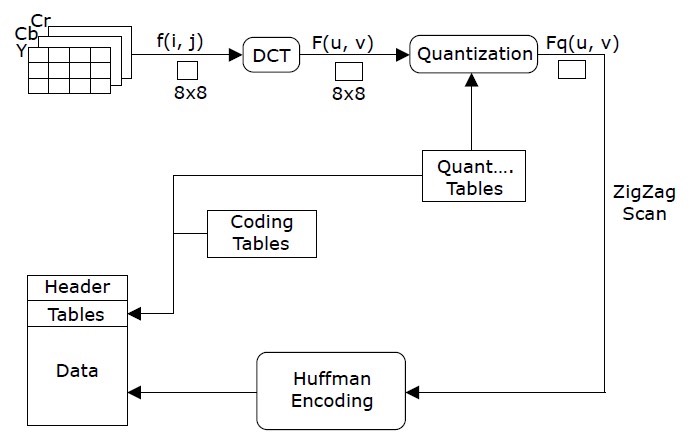

Jpeg编码器是一种用于将图像压缩为JPEG格式的硬件IP。它支持YCbCr422作为输入格式,并将其转换为422格式的输出。每路数据位宽为8位,这样可以保证图像的高质量压缩和还原。此外,该编码器还支持可编程量化表,使用户能够根据实际需求对图像进行更细致的压缩控制。

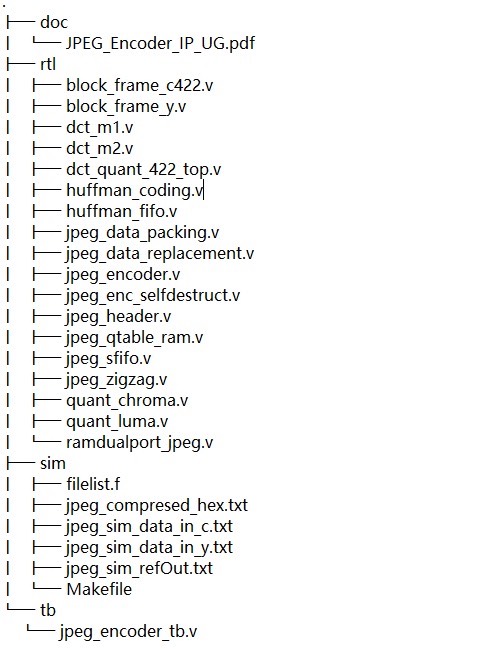

该Jpeg编码器采用纯Verilog代码实现,这使得它能够方便地移植到各种FPGA平台。Verilog是一种硬件描述语言,通过使用Verilog,开发人员可以直接描述电路的结构和功能。这样一来,Jpeg编码器可以根据不同平台的要求进行适配和优化,从而获得更好的性能和兼容性。

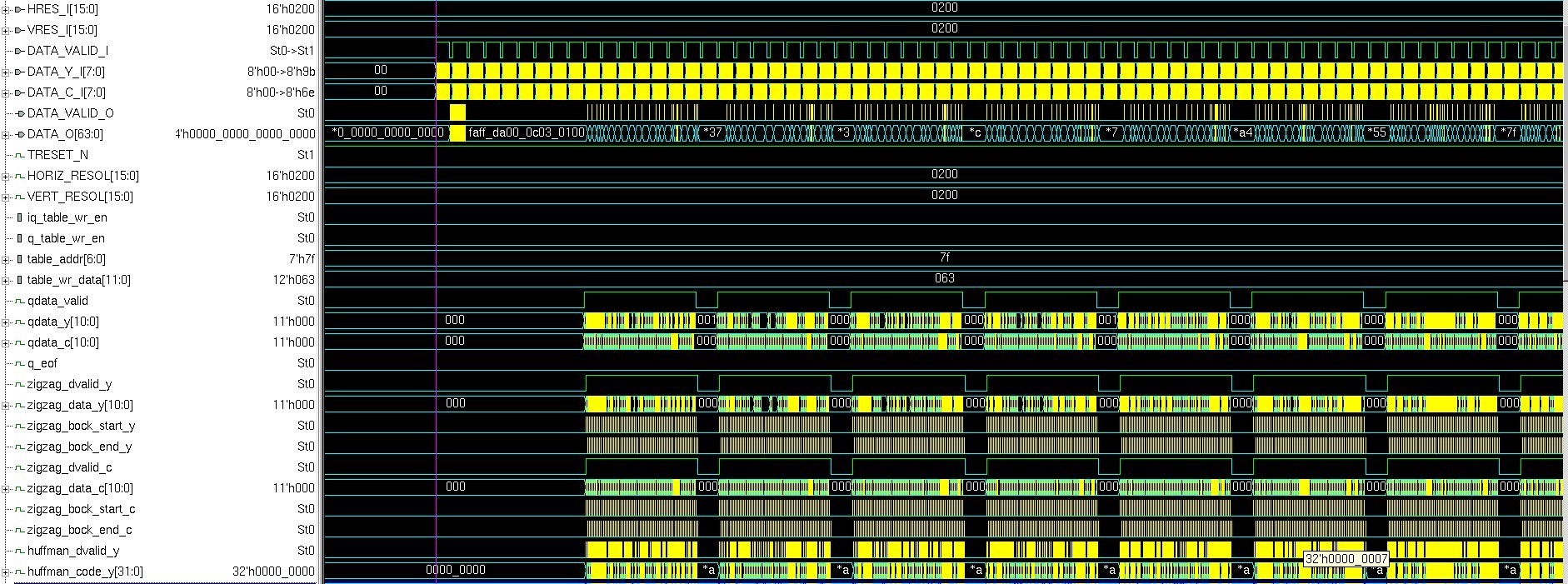

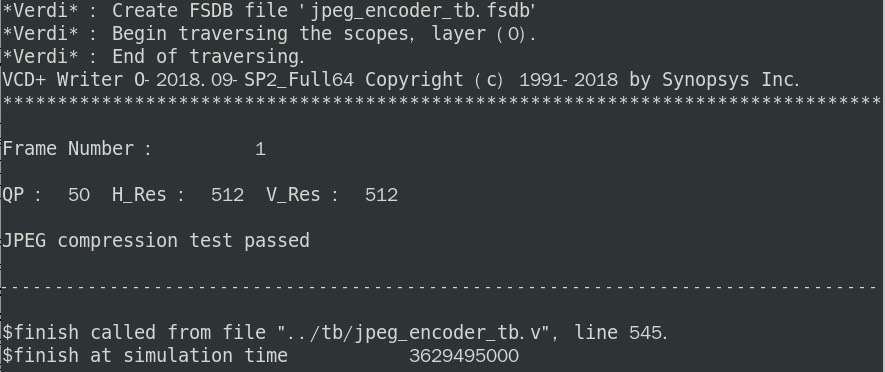

为了保证Jpeg编码器的正确性和稳定性,我们使用vcs进行了仿真。vcs是一种常用的仿真工具,它能够高效地对Verilog代码进行仿真和验证。通过对Jpeg编码器进行仿真,我们可以验证其功能和性能是否符合预期,并及时发现和修复可能的问题。

在实际应用中,Jpeg编码器可以广泛用于图像压缩领域。JPEG(Joint Photographic Experts Group)是一种常用的图像压缩标准,它通过采用DCT(离散余弦变换)和量化等技术,将图像压缩到较小的文件大小,同时保持较高的视觉质量。因此,Jpeg编码器在数字摄像头、图像处理器、视频编码器等领域得到了广泛应用。

总之,Jpeg编码器是一种支持YCbCr422输入、422格式输出的IP,每路数据为8位,支持可编程量化表。它采用纯Verilog代码实现,方便移植到任何FPGA平台,并使用vcs进行了仿真验证。该编码器可以在图像压缩领域发挥重要作用,为实际应用提供高效、高质量的图像压缩解决方案。

【相关代码,程序地址】:http://fansik.cn/699188634792.html

1226

1226

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?