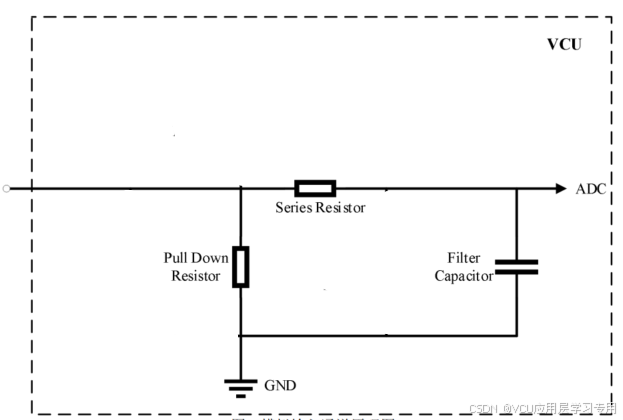

1.不带分压功能的电压型模拟量输入

即由一个下拉电阻和一个一阶RC低通滤波电路组成。

RC滤波电路截止频率计算

- fc=1/2πRC1

在没有电压输入时,下拉电阻将信号线强制拉至低电平(GND)

解决以下关键问题:

- 防止信号浮空(Floating):

- 未连接信号源时,避免引脚电平不确定(可能被噪声干扰误判为高电平)。

- 典型场景:数字输入引脚、未使用的逻辑门输入端。

- 定义默认状态:

- 确保电路在无输入时处于已知状态(如默认低电平)。

- 限流保护:

- 限制意外高压(如静电放电)流入敏感器件(如MCU GPIO)。

失效风险与解决方案

下拉电阻是电子电路中的 “稳定锚”,通过强制定义默认电平状态,提升系统抗干扰能力和可靠性。其设计需平衡 抗噪性、功耗、精度,并符合车规级环境要求(如温度、振动)。

| 失效模式 | 后果 | 解决方案 |

|---|---|---|

| 电阻开路 | 信号浮空,导致误触发或ADC读数异常 | 选用高可靠性电阻(如车规级厚膜电阻) |

| 电阻短路 | 信号被强制拉低,无法检测有效输入 | PCB布局时避免与相邻高压走线过近 |

| 阻值漂移 | 分压比变化,测量误差增大 | 选择低温漂电阻(如±50ppm/℃) |

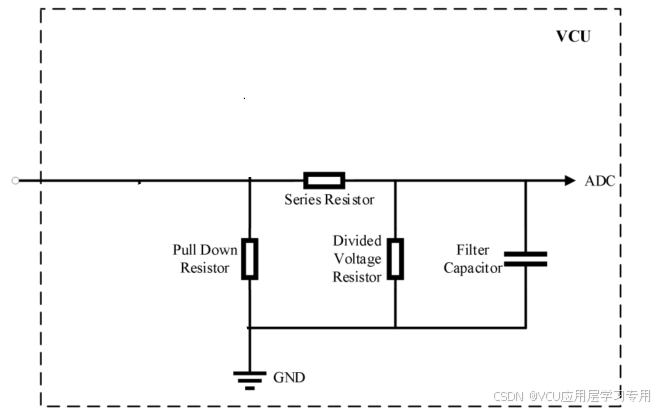

2.带分压功能的电压型模拟量

相比较不分压模拟量输入电路多了一个Divided Voltage Resistor(分压电阻)

- 下拉电阻(100kΩ)确保信号源断开时电位稳定;

- 串联电阻(100kΩ)限流并参与分压;

- 分压电阻(16kΩ)将高压信号压缩至ADC量程;

- 滤波电容(100nF)抑制高频噪声,

Rseries和Rdivide组成分压网络 实际输出为VADC=Vin*Rdivide/(Rdivide+Rseries)

即VADC=Vin*16/116

Rseries与滤组成一阶RC低通电容滤波网络,利用电容通高频阻低频特性,将处于截止频率以上的高频信号旁路,低频信号通过,抑制高频噪声。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?