ASIC FPGA异步FIFO小IP。

可用于ASIC设计和FPGA设计。

集成简单方便,配置灵活。

其相关Feature如下所示:

1) 纯异步设计。

读写时钟异步。

2) FIFO空满标志

3)支持FLUSH操作。

4)FIFO深度及位宽可扩展。

其中深度支持2的整数幂;位宽支持任意可配。

5) 支持读写时钟域FIFO Number Report。

灵活集成。

ID:6929608305673918

深圳洪哥

ASIC FPGA异步FIFO小IP是一种可用于ASIC设计和FPGA设计的简单方便的集成电路。它具有以下几个主要特性。

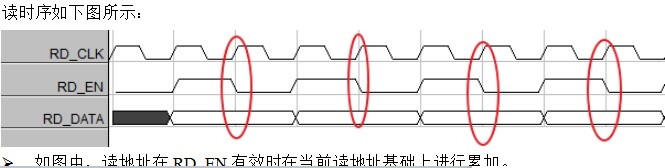

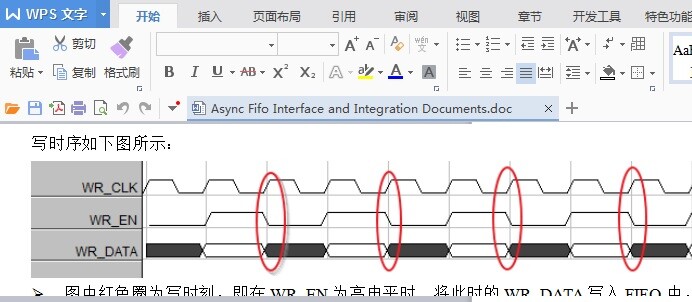

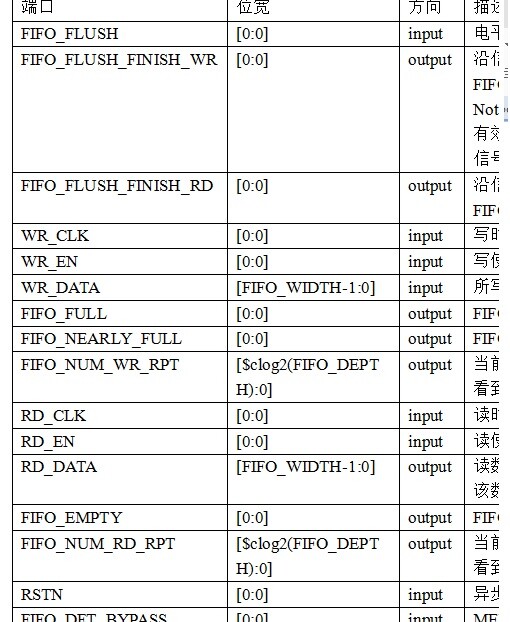

首先,ASIC FPGA异步FIFO小IP采用纯异步设计,读写时钟完全异步。这意味着在读取和写入数据时,不需要使用时钟来同步数据传输,从而大大简化了电路设计的复杂性。

其次,该FIFO小IP提供了FIFO空满标志。这意味着当FIFO已满或者已空时,可以通过标志位来判断其状态,从而方便地实现数据的流控。

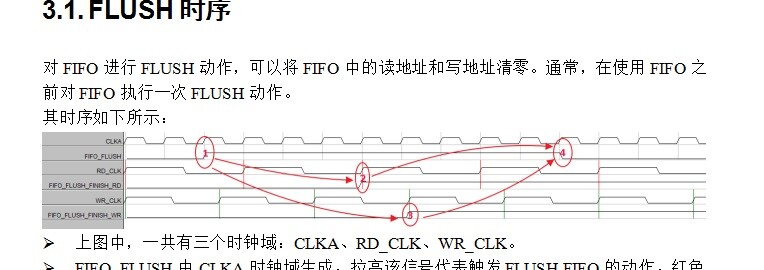

第三,ASIC FPGA异步FIFO小IP支持FLUSH操作。FLUSH操作可以清空FIFO中的所有数据,使得FIFO可以重新开始接收新的数据。这在某些特定应用中非常有用,例如需要重置数据流的情况。

其次,该FIFO小IP的深度和位宽可进行灵活扩展。深度可以支持2的整数幂,这意味着可以根据实际需求选择适当的FIFO深度。而位宽则可以任意可配,使得FIFO可以适应不同数据宽度的情况。

最后,ASIC FPGA异步FIFO小IP支持读写时钟域FIFO Number Report。这意味着在FIFO操作过程中,可以根据读写时钟的不同域来进行报告,从而更好地了解FIFO中数据的状态和传输情况。

总的来说,ASIC FPGA异步FIFO小IP是一种非常灵活集成的FIFO设计,可以在ASIC设计和FPGA设计中广泛应用。它的异步设计、FIFO空满标志、FLUSH操作、深度和位宽灵活扩展、以及读写时钟域FIFO Number Report等特性,使得在各种场景下都能够方便地实现数据传输和流控。无论是在ASIC设计还是FPGA设计中,该FIFO小IP都能够提供高效可靠的数据存储和传输功能。并且,由于集成简单方便,配置灵活,它可以快速应用于各种设计中,极大地提高了设计的效率和可靠性。在实际应用中,通过合理选择FIFO的深度和位宽,以及根据需要进行FLUSH操作,可以更好地满足不同应用场景对数据传输的需求。总的来说,ASIC FPGA异步FIFO小IP为设计人员提供了一种功能强大、灵活可靠的数据存储和传输解决方案。

相关的代码,程序地址如下:http://imgcs.cn/608305673918.html

38

38

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?