下面是基于在Altera Quartus II 下如何调用M odelS im 进行仿真的一个实例。 本来想和上一张 modesin 破解应用一起讲解,但是我在写的时候发现太多了,为了清楚明了,我就单独出了一篇。

Quartus II 9.1,modesim 版本为modesim 6.5a,Quartus无法像ISE 那样方便的直接调用ModelSim,而

是需要额外的做一些工作。这确实给我们的仿真调试带来了一些不便。我也是在摸索了好久以后才彻底搞定这个问题,下面分享下,力求明白易懂,让大家少走一些弯路。

1、首先我们写一个代码如下的文件,保存为.v,因为我们采用的是verilog语言,代码意思为DIV 输出一个2分频的一个时钟,我们这里为什么要用到时钟呢,因为在我们不用到时钟的modesim 仿真中,要简单很多,使用到时钟的modesim 仿真,要全面一点,因此,我们这里主要讲解这个。

module clkdiv //clkdiv 这个名一定要跟文件名相同

(

clk,

rst_n,

div

);

input clk; //系统时钟

input rst_n; //复位信号,低有效

output div; // 2 分频信号

reg div;

always @ (posedge clk or negedge rst_n )

if( !rst_n )

div <= 1'b0;

else

div <= ~div;

endmodule

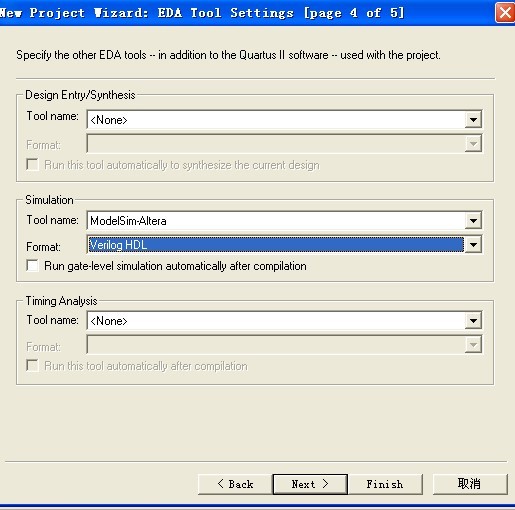

2、然后我们新建工程,新建工程与普通的新建工程是没区别的,最后一步的时候要注意,如下图

选择我们要使用的仿真软件和仿真语言,

3、然后我们编译一下这段代码,在文件夹下面就会多一个(工程目录)\simulation\modelsim 。这个下面生成的是仿真所需要的文件,其中.vo 文件就是我们的代码布局布线信息。

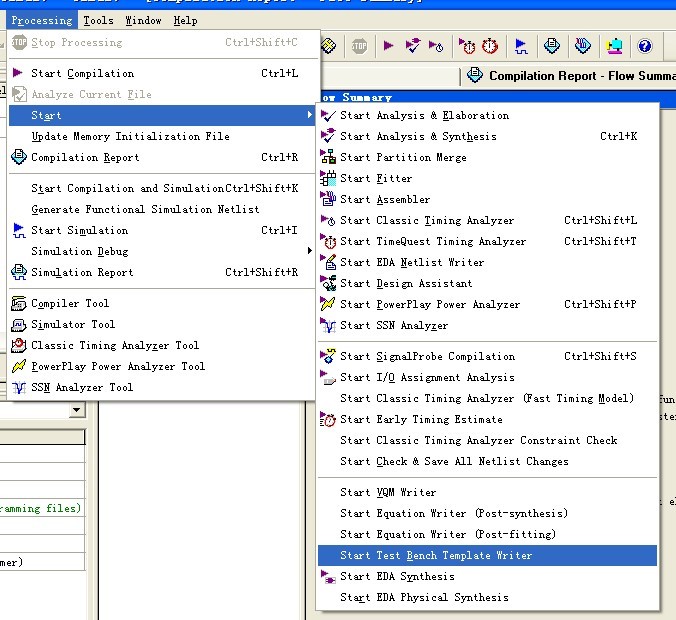

4、打开processing下的start目录下的start test bench template writer自动创建后

缀为vt的文件。

5、接下来我们打开 工程目录\simulation\modelsim\clkdiv.vt 进行编辑,其中默认生成的文件如下:

`timescale 1 ps/ 1 ps

module clkdiv_vlg_tst();

// constants

// general purpose registers

reg eachvec;

// test vector input registers

reg clk;

reg rst_n;

// wires

wire div;

// assign statements (if any)

clkdiv i1 (

// port map - connection between master ports and signals/registers

.clk(clk),

.div(div),

.rst_n(rst_n)

);

initial

begin

// code that executes only once

// insert code here --> begin

// --> end

$display("Running testbench");

end

always

// optional sensitivity list

// @(event1 or event2 or .... eventn)

begin

// code executes for every event on sensitivity list

// insert code here --> begin

@eachvec;

// --> end

end

endmodule

我们要注意到,默认的模块名字是 clkdiv_vlg_tst ,把我们所写的clkdiv.v文件封装成了 clkdiv i1 的文件名,通过write 连接。

因此我们需要修改下面的initial 文件,

`timescale 1 ps/ 1 ps

module clkdiv_vlg_tst();

// constants

// general purpose registers

reg eachvec;

// test vector input registers

reg clk;

reg rst_n;

// wires

wire div;

// assign statements (if any)

clkdiv i1 (

// port map - connection between master ports and signals/registers

.clk(clk),

.div(div),

.rst_n(rst_n)

);

initial begin

clk = 0;

forever

#10 clk = ~clk;

end

initial begin

rst_n = 0;

#1000 rst_n = 1;

#1000;

$stop;

end

endmodule

修改完后的test bench 文件如上面代码。我们进行保存意思为:

上电后1us 复位信号

运行时间为 1us,(当然我们可以一直运行,这个我们可以自行设定)。

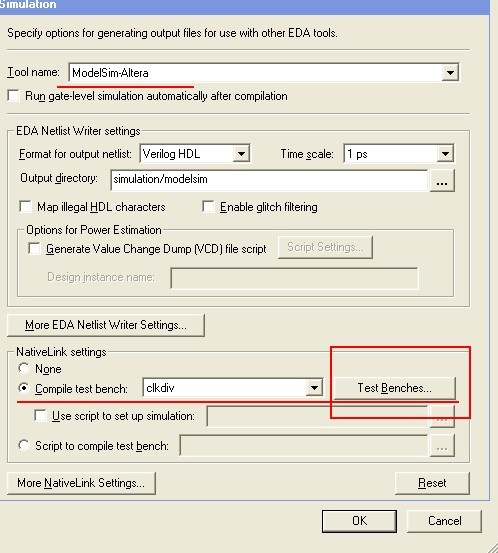

6、下面我们设置仿真选项,打开 Assignments ---> EDA Tool Settings

其中在N ativeLink settings 选择 c ompile test bench 对 test bench 进行设置非常关键

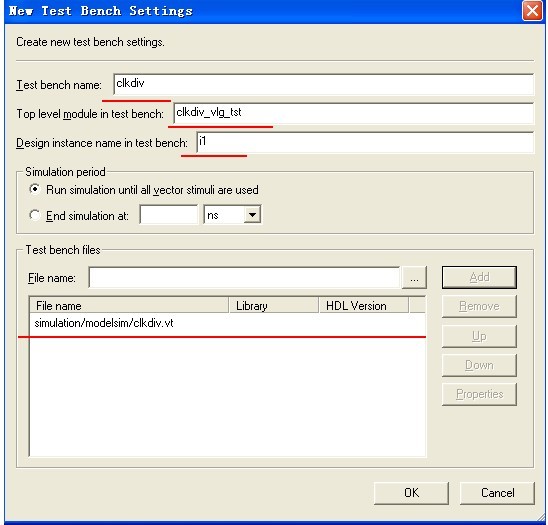

参考如下:按“test benches…”进入设定如下

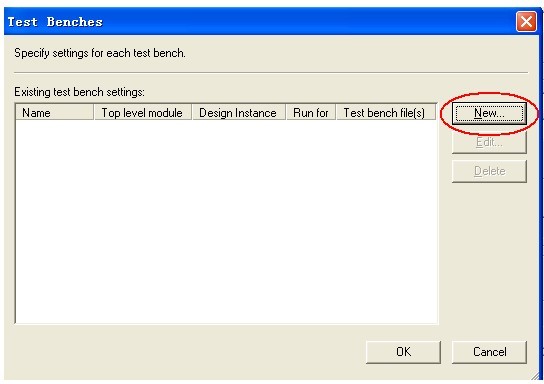

选择NEW

进入下面页面设置

test bench name 填写的是:simulation/modelsim 目录下的 clkdiv.vt 文件名 clkdiv。

Top level module in test bench 填写的是:打开clkdiv.vt 文件内的module 名字。

Design inst ance name in test bench: 默认i1 .

这里的文件名字,我们在修改test bench 已经讲过了。

完成以上3 步填写,在Test bench files 下面添加test bench files->clkdiv.vt点击OK

完成设置。

7、设置完成以后,在进行编译。

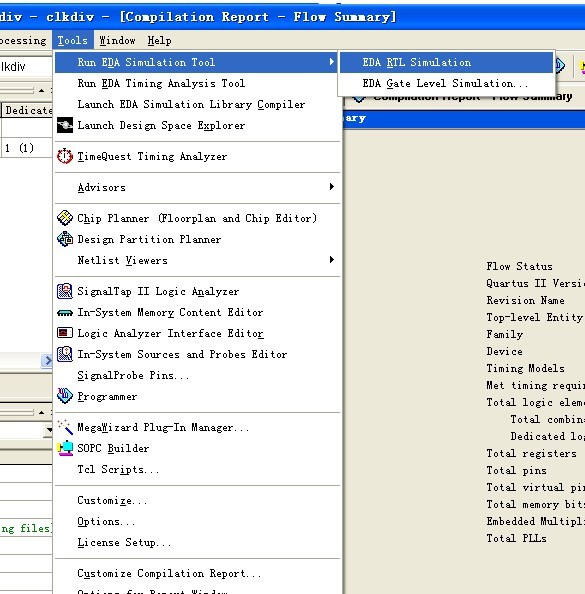

8、在quartus 调用 modesim

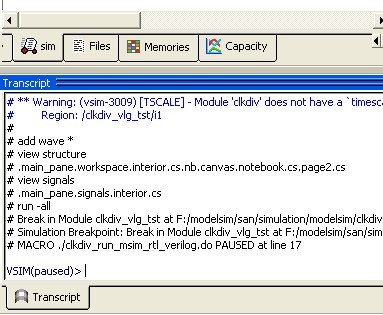

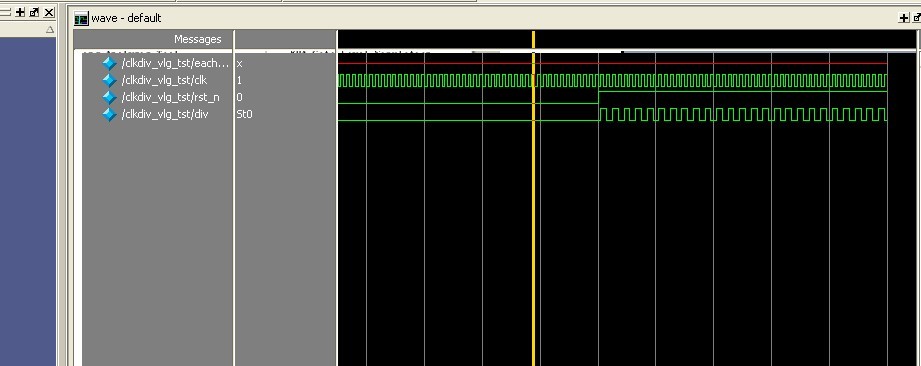

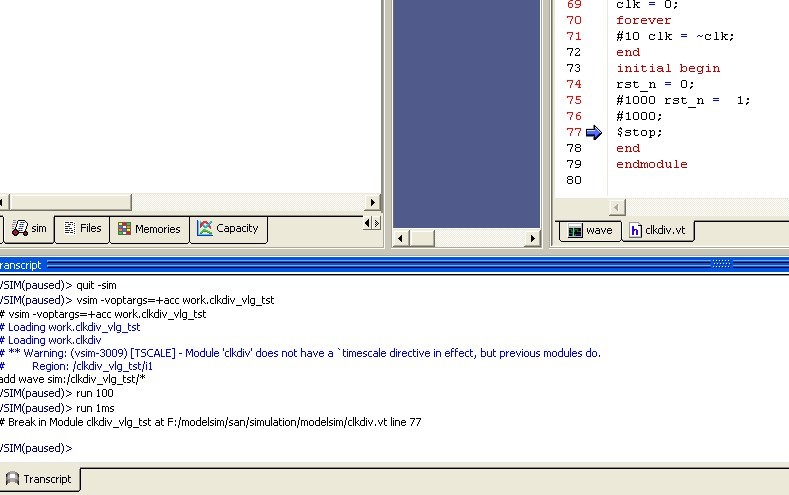

9、由于我们设置了仿真时间,默认就已经运行完了,得到如下波形

1us 后复位,然后运行1us 的2分频,

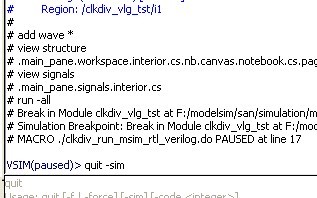

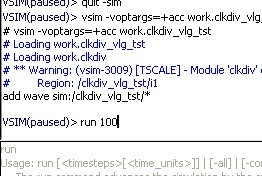

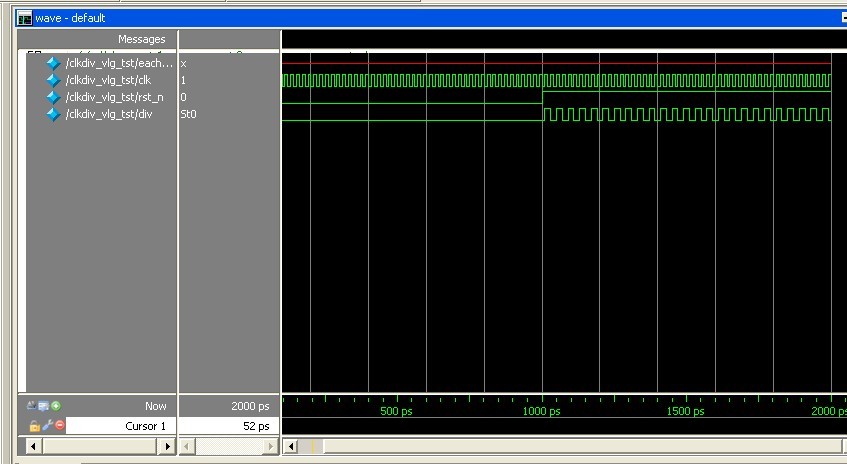

10、如果我们需要一点一点的看,那么我们在下面的命令行中输入命令

首先我们结束当前仿真 quit –sim 回车

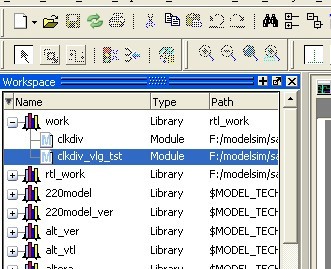

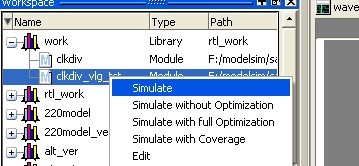

然后在 library 中找到 work 下面的工作文件

为什么要选择clkdiv_vlg_tst 文件仿真呢?在前面我们就说了,因为我们把clkdiv 封装成了一个文件,让clkdiv_vlg_tst 去调用,因此我们只需要仿真clkdiv_vlg_tst 就OK,

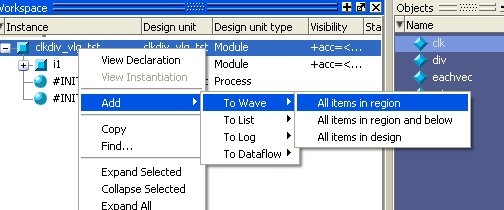

添加仿真网络

假设我们先运行100ps,那么我们如数 run 100

得到如下波形

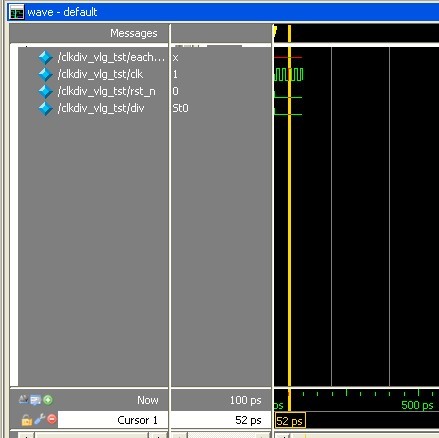

如果我们要运行 1ms ,那么出现如下:

其中波形为

这里提示为:

# Break in Module clkdiv_vlg_tst at F:/modelsim/san/simulation/modelsim/clkdiv.vt line 77

意思我们仿真超过了所设定的值。

到这里我们的仿真和modesim 基本应用就讲完咯!! 886

---------------------------------------------------------------------

转自:http://blog.csdn.net/ywhfdl/article/details/7467471

2198

2198

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?