摘要

普遍认为光子集成光路(PIC)是一种未来可广泛应用低成本光子系统。但当前PIC仍然比IC贵几个数量级,这限制了它在一些利基市场的应用。

最近,一种新的光子集成方法正在出现,它将把PIC的研发和样机成本以及生产时间减少一个数量级以上。它使得无论大型还是小型公司均能够在单个芯片上集成复杂并先进得光子功能,并在PIC应用方面取得突破。本文以埃因霍温大学COBRA研究所开发的技术为例,阐述了通用光子集成技术的概念,并介绍了基于InP的通用集成技术的现状和前景。

1.背景

1.1. 光子集成的历史

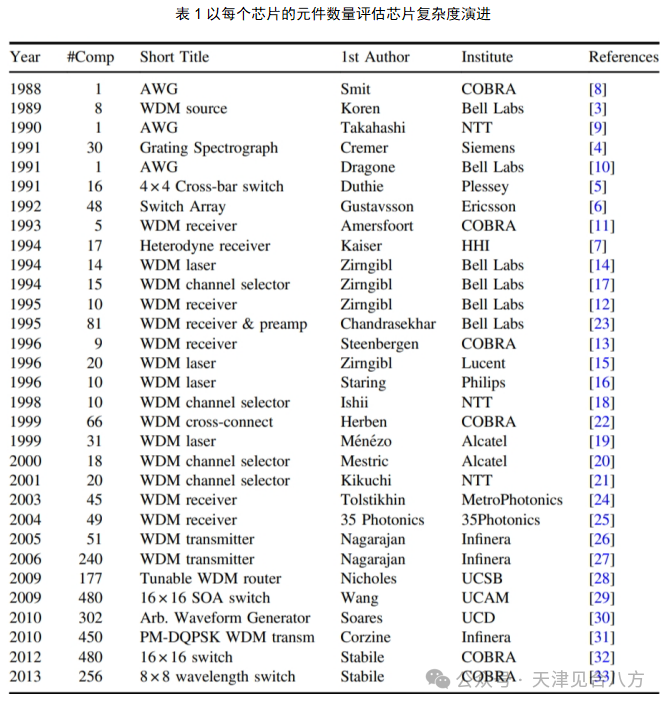

从40多年前首次出现在文献[1]中以后,人们普遍认为微光子集成将走上与微电子集成相似的发展道路。Tien在1977年的综述论文中[2]提到了微光子集成或当时所称的“集成光学”的主要目标之一:“在小衬底上集成大量光学器件,从而形成一个类似微电子集成电路的集成光路”。在接下来的几年里,许多复杂度不断提高的芯片被报道出来。图1显示了以集成在单个芯片上的元件数量衡量的复杂性发展。表1概述了基本数据,并简要介绍如下。

复杂的基于InP的光子集成光路(PIC)的早期例子是Koren[3]的WDM源,其在单个芯片上集成了由半导体光学放大器(SOA)和可调谐布拉格光栅反射器组成的三个激光器,以及功率组合器和功率SOA;Cremer[4]的基于光栅的接收器,将Echelle光栅解复用器与30多个检测器集成;Duthie[5]的4×4交叉开关,集成了16个反向Δβ开关;Gustavsson[6]的开关阵列,集成了24个SOA门开关和24个1×2耦合器;Kaiser[7]的偏振分集外差接收器,将DBR型本地振荡器激光器与偏振模式分离器、偏振模式滤波器、3dB合束器、平衡探测器、结FET和负载电阻器集成在一起。

迄今为止,基于AWG的PICs的复杂性最高。它始于Smit[8]于1988年发布的首个AWG,随后是Takahashi[9]和Dragone[10]。在AWG发明后,报告了许多光路复杂性不断增加的基于AWG的产品:Amers foort[11]、Zirngibl[12]和Steenbergen[13]的具有5–10个元件的WDM接收器;Zirngibl[14,15]和Staring[16]的具有10-20个元件的WDM激光器;Zirngibl[17]、Ishii[18]、Ménézo[19]、Mestric[20]和Kikuchi[21]的具有10–20个元件的WDM波道选择器,以及Herben[22]的具有66个元件的交叉连接芯片;Chandrasekhar[23]的带有集成前置放大器的WDM接收器,该接收器包含81个器件,其中大部分是电子元件(晶体管和电阻器)。

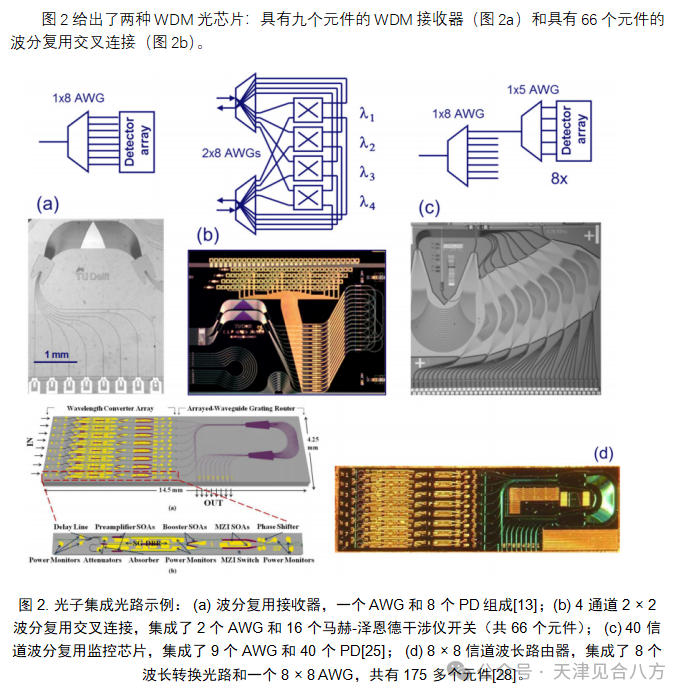

进入21世纪,复杂性的显著提高:Tolstikhin[24]、Three Five Photonics[25]和Infinera [26]的带有44-51个元件的WDM发射和接收器。不久之后,在2006年,Infinera发布了一款具有241个元件的40通道WDM发射机[27]。图2c说明了Nichols在2009年报道的具有49个元件的40通道WDM监控芯片[25]和具有175个元件的8×8波长路由器芯片[28]。同年,王[29]报告了一个16×16 SOA开关矩阵,其中480个元件在全有源晶片中制造,一年后,Soares[30]提出了一个具有300多个元件的100通道任意波形发生器。后一种装置还包含400个移相器,用于降低分离100个波长信道的非常大的AWG中的高串扰电平。Corzine(Infinera)[31]和Stabile(COBRA)[32]报道了两种采用先进的有源-无源集成技术制造的具有450多个元件的PIC。Stabile还报道了一种具有256个元件的8×8波长开关[33]。表1概述了所使用的设备。Coldren[34]对高性能InP基PIC进行了极好的概述。

在微电子技术中,每个芯片的晶体管数量呈指数级增长,在过去四十年中,平均每两年翻一番。这种现象被称为摩尔定律[35,36]。图1揭示了微光子学的类似发展,尽管处于早期阶段,然而,如果我们限制在基于AWG的器件上,使用或多或少具有可比性的技术(具有集成放大器和/或检测器的AWG),大多数异常值都会消失,这表明光子集成正在走与微电子类似的发展道路,可能是由工艺设备的相同改进驱动的。

1.2. 通用光子集成技术

尽管在芯片复杂性的发展方面有相似之处,但今天的微光子和微电子之间有一个显著的区别,那就是所遵循的研发方法。在微光子学中,大多数集成技术都是针对特定应用而开发的。因此,我们拥有几乎与应用一样多的技术,其中大多数技术相似,但差异足够大,无法轻松地将设计从一个晶圆厂转移到另一个晶圆。由于这种巨大的碎片化,许多特定应用技术的市场太小,无法证明它们有理由进一步发展成为低成本的工业批量制造工艺。因此,芯片成本仍然太高,无法广泛应用。

这与微电子技术大不相同,微电子巨大市场由一小部分集成工艺(其中大多数是CMOS工艺)提供服务。在这些工艺中,可以通过基本构建块(BBB)实现各种功能,如晶体管、电阻器、电容器和互连。通过连接不同数量和拓扑结构的这些构建块,我们可以实现各种各样的光路和系统,其复杂性从几百个到超过十亿个晶体管不等。我们将这种过程称为通用集成工艺,在这种工艺中,使用很少得BBB组合各种功能。

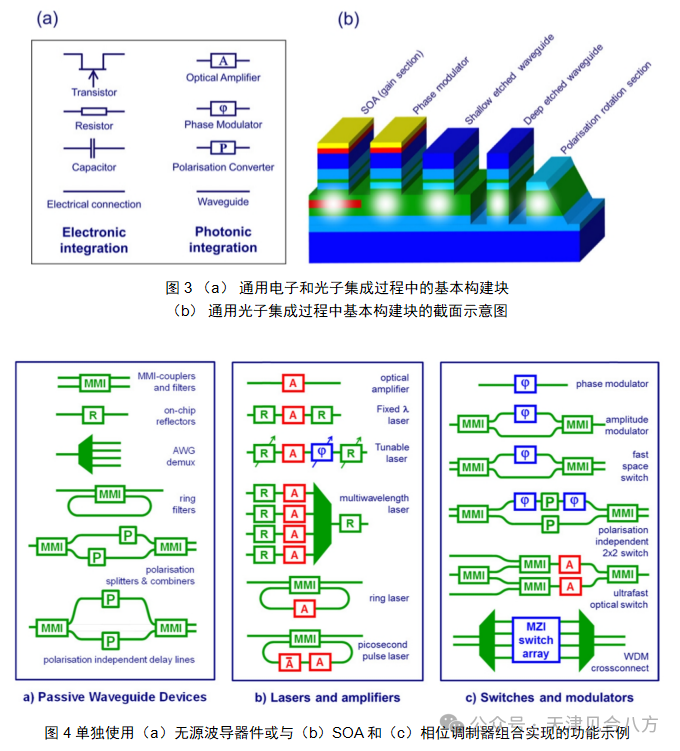

在光子学中,我们可以采用同样方式,如图3a所示。通过构建控制光的基本特性(振幅、相位和偏振)的构建块,并将它们的集成组合成多种功能块。图3b显示了在InP衬底上的单个通用集成工艺中集成的五个不同元件的示意图。该示例取自TU埃因霍温COBRA研究所。绿色层是承载光波导模式(由白点指示)的波导层;波导层中心的暗红色层是光学增益介质。有了良好的波导结构,我们可以进行互连,也可以制作耦合器、滤波器和多路分解器等无源元件。有了光放大器(SOA)、相位调制器和偏振转换器,用于控制光的振幅、相位和偏振,实现更多的功能,如图4所示。

图4a显示了使用无源波导制作的一些元件。最重要的是MMI耦合器和AWG多路解复用器。通过强约束深刻波导,还可以制造MMI反射器和紧凑型环形滤波器。在无源波导中制作的另一个重要构建块是偏振转换器。通过将其适当地放置在马赫-曾德尔干涉仪MZI中,可以制作偏振分离器和组合器;将其放置在偏振相关元件的一半,则该元件的响应与偏振无关。

SOA与无源器件相结合提供了更多功能,如图4b所示:法布里-珀罗(FP)激光器、多波长激光器、环形激光器,当与波长可调反射镜相结合使用时,还包括可调激光器。通过使用反向偏置的短SOA部分作为饱和吸收器,我们可以制造皮秒脉冲激光器。反向偏置的SOA也可以用作光探测器。

图4c说明了将相位调制器与无源元件相结合来实现的一些功能:幅度调制器、空间开关、波长选择开关,如WDM交叉连接和分插复用器。通过利用集成在MZI中的SOA的非线性特性,我们可以制造超快光开关。

通用集成技术的一个优点是,因为它们服务于许多不同的应用,所以它们证明了在构建块级别开发具有非常高性能和可靠性的技术的投资是合理的。这将使在这种技术中实现的光路具有高度竞争力。当然,单一的通用流程并不适用于所有应用程序。就像微电子技术一样,我们需要一些不同的通用技术,针对不同类型的应用进行优化。但通用技术的数量可能很小,比当今技术的种类要少得多。

此外,在标准化技术中,我们可以为设计师们提供标准元件或子光路库以及相关的软件。这大幅缩短设计时间的并提高了设计精度和准确度,从而用更少的设计周期完成开发。

所有这些都给光子学的商业模式带来了根本性的变化,使商业和学术团体能够合作并向前迈进,而不是永远重新发明轮子。

1.3. MPW多项目晶圆

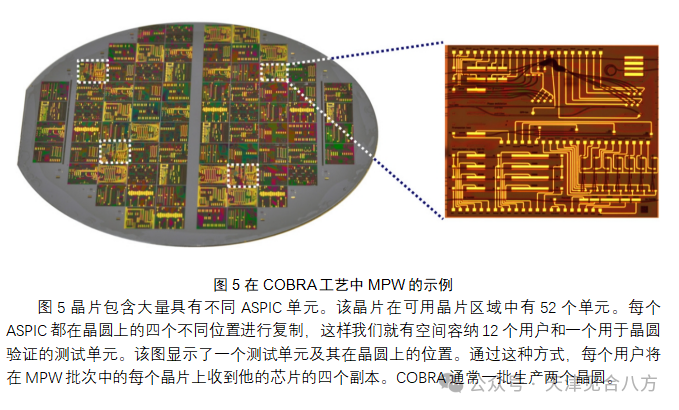

通用集成技术的一个重要优点是,许多不同的设计可以在同一块晶圆上组合,因为它们都使用相同的制造工艺。这种晶片被称为多项目晶片MPW。在这种MPW运行中制造的光子IC被称为ASPIC:专用光子集成光路,相当于光子ASIC。ASPIC是在标准化通用过程中实现的特定于应用程序的PIC。图5展示了多个设计是如何组合在一块晶圆上的。在这个例子中,有12种不同的设计;每个设计重复四次。因此,从MPW批次中的每一块晶圆中,设计者将收到四块芯片。这种方法大大降低了研究和开发成本。在开发阶段,通常需要几个设计和制造周期才能达到所需的性能。通常,晶片中的一些芯片足以在这个阶段测试设计。通过在单个晶片上组合多个设计,每个设计者都可以获得一些芯片,并且运行的成本可以由MPW的所有参与者分担,这大幅降低了设计成本。

图5晶片包含大量具有不同ASPIC单元。该晶片在可用晶片区域中有52个单元。每个ASPIC都在晶圆上的四个不同位置进行复制,这样我们就有空间容纳12个用户和一个用于晶圆验证的测试单元。该图显示了一个测试单元及其在晶圆上的位置。通过这种方式,每个用户将在MPW批次中的每个晶片上收到他的芯片的四个副本。COBRA通常一批生产两个晶圆。

1.4. 通用流片模型

通用集成方法通过在单个或几个高度标准化的工艺中开发不同的产品来大幅降低成本。然而,如果工艺所有者不向外部用户开放,那么可以利用这种方法的公司数量仍然受到限制。因此,通用流片模式的基础是通用光芯片厂:光芯片厂提供对其通用集成过程的开放访问。在硅微电子领域,许多芯片制造商正在提供流片代工,在光芯片领域,该方式刚刚开始。

TU Eindhoven的COBRA研究所自本世纪初以来一直是通用光子集成技术的先驱[37]。通用集成方法在欧洲卓越网络ePIXnet[38]中获得了发展,从2004年到2009年,活跃在光子集成领域的63多个研究小组在许多光子集成技术上进行了合作。基于InP的通用光子集成技术已在许多欧洲和国家项目中进行了探索。JePPIX平台[44]组织了对基于InP的通用流片工艺开放,欧洲基于InP光子集成技术领域的关键参与者正在进行合作。Smit等人[45]对基于InP的通用流片进行了更详细的描述。目前,三家芯片制造商提供了基于InP的通用晶圆工艺的(半)商业化途径:总部位于英国的Oclaro公司、位于柏林的Fraunhofer HHI和位于荷兰埃因霍温的COBRA子公司SMART Photonics。

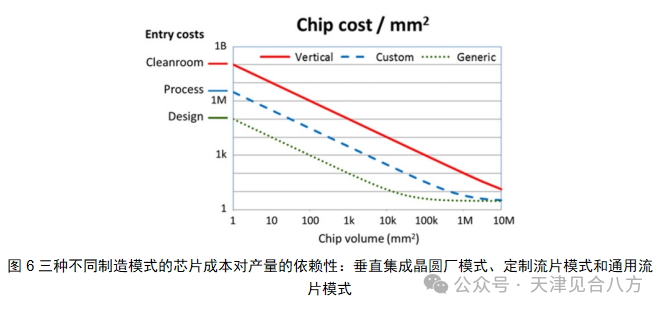

图6给出了一个非常简化的解释,说明如何通过引入通用流片工艺来降低进入成本。在垂直集成晶圆厂模式中,一个用于制造光子芯片的设备齐全的先进晶圆厂成本大约为1亿甚至数亿欧元(美元)。如图6所示,需要超过1000万平方毫米(2500个3〃晶圆)的芯片体积才能使每个芯片的投资成本低于10欧元/平方毫米。中等规模的PIC芯片尺寸为10-30mm2,因此在这个价格水平下,大约需要100万个芯片才能获得投资回报。这种投资只有在市场占主导地位的顶级科技公司才能负担得起。

一些流片厂提供无晶圆厂客户服务,以分担洁净室运营成本。通过这种方式,无晶圆厂客户可以避免对晶圆厂的巨大投资,并将投资限制在特定PIC的特定集成过程的开发成本上。我们将此模型称为定制流片模式:流片厂为定制PIC开发专用工艺。对于中等复杂度的PIC,包括工艺鉴定在内的工艺开发成本约为一百万至几百万欧元,在10000个芯片的几倍体积下达到10欧元/mm2的水平(图6中的第二条曲线标记为定制)。这些数量仍然很大,投资成本加上风险对大多数中小型企业SMEs来说是令人望而却步的。

如果芯片设计基于通用(标准化)集成过程,则可以实现显著的进一步成本降低,该集成过程的开发成本可以由许多用户分担。那么进入成本主要局限于设计成本,可能在10万欧元左右。通过开发具有元件库的专用工艺设计套件(PDK),可以进一步降低设计成本,该元件库包含晶圆平台中构建块的掩模布局和精确模型。这将减少设计时间和达到所需性能所需的设计周期数。在这种方法中,在1000个芯片的体积下,已经可以达到10欧元/mm2的成本水平(图6中的第三条曲线标记为通用集成)。这将使大多数中小企业能够负担得PIC开发的进入成本。因此,预计通用模型的引入将推动光子IC应用的快速发展。

2.通用集成工艺

有许多种专用集成技术,但对于更通用的技术,集成概念有很大的自由度,不同的流片厂有不同的集成技术——即使它们在功能上是等效的。在本节中,我们将以COBRA工艺为代表,解释通用光子集成工艺的基本原理;它是第一个提供MPW服务的通用工艺,并且大多数工艺和构建块信息已经公开。

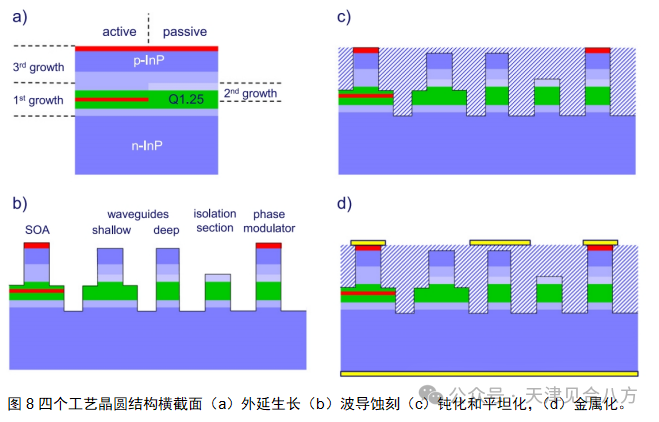

集成过程大致可以细分为四个工艺模块,如图8所示,并将在下文中大致描述。我们还会给出Oclaro、Fraunhofer HHI和SMART Photonics等晶圆厂正在进行或计划进行的通用工艺的一些新进展。

2.1. 外延生长

对于有源(放大器)和无源(透明波导)材料的集成,已经报道了许多集成方案,可分为单步和多步外延生长工艺。

单步外延工艺。如图7a和7b所示,在单步工艺中,包括有源层和无源层的全层堆叠在一起通过单步外延生长,然后通过局部去除有源层来形成透明波导。图7a显示了无源波导顶部的有源波导。在这种方法中,需要特殊的结构,例如垂直锥形,用于将光从有源波导平滑地耦合到无源波导,反之亦然。Menon[46]和Tolstikhin[47]对垂直集成方法进行了详细描述。在图7b中,只有一个(复合)波导,包括有源层。因此,不需要垂直耦合,而是以不连续性为代价这导致耦合损耗和反射。可以通过用InP包层覆盖结构来减少不连续性,但这需要额外的生长步骤。

图7c说明了另一种单步集成方法:量子阱混合。这里的有源层由许多量子阱组成。通过用在半导体晶体中产生空位的材料覆盖有源层,可以使有源层成为无源层,当晶片被加热时,空位扩散到有源层。这些空位导致量子阱原子种类与它们之间的势垒层的原子种类混合,这导致有效带隙的增加。混合可以使有源材料的带隙波长增加100nm以上,使其变得完全透明。但是中间值也是可能的,例如用于电吸收调制器。Skogen[48]对此进行了详细描述。该方法的缺点之一是有源区和无源区中的掺杂剂浓度相同,这导致透明区中的高损耗。这个问题可以通过引入额外的外延步骤来解决,该外延步骤用于在透明波导部分上生长未掺杂的包层(毯式生长)。

多步外延生长工艺。从外延的角度来看,单步工艺是简单的,但为有源和无源之间的有效和良好控制的耦合而采用得锥形结构和/或附加生长步骤的形式引入了额外的复杂性。图7d说明了最常用的方法:对接集成。这里,有源和无源波导结构是在不同的生长步骤中形成的,因此在外延层结构和掺杂水平上提供了很大的灵活性。在过去,额外的生长阶段可能会导致严重的产量问题,然而,随着现代外延技术的发展,这不再是一个问题。

在COBRA通用工艺中,使用三步外延工艺来获得图7d和图8a中示意性描述的结构。

在第一生长步骤中,生长包括p掺杂包层的下部的有源层堆叠。接下来,有源区域被掩模并且暴露的区域被蚀刻掉。在第二选择区域再生长步骤中,用透明波导堆叠代替蚀刻掉的部分,直到与第一生长相同的水平。在透明部分中,包层未被掺杂以避免p掺杂剂引起的吸收损失。在第三生长步骤中,用p掺杂的包层覆盖整个结构。如果重新生长工艺条件被适当地调节,则重新生长晶片具有平滑的表面和在有源和无源波导之间具有低反射率的平滑连接。锥形和倾斜界面有利于进一步减少光学损耗和反射。

COBRA和Oclaro的工艺非常相似,但在细节上有所不同。Fraunhofer HHI的工艺差异较大:它使用半绝缘(铁掺杂)衬底,这导致了更好的射频能力,并能够根据需要对单个设备进行电隔离,例如在平衡探测器中。到目前为止,它还不支持光放大器的集成,但未来发布的平台将提供类似的功能,但在技术细节上有所不同。在下面的段落中,我们将讨论目前正在研究的一些工艺增强技术。

减少波导损耗。在当前的集成方案中,与有源元件的电连接所需的p掺杂顶部包层引入了2dB/cm量级的额外波导传输损耗。在可能具有几厘米波导长度的较大PIC中,这引入了高损耗。这种损耗可以通过将p掺杂的包层限制在有源区来去除,从而在透明波导部分中不具有p掺杂。未掺杂区域中的损耗低于1dB/cm,并且有源区域通常很短,使得由p掺杂剂引起的额外损耗贡献最多为十分之几dB。局部未掺杂的包层可以通过透明波导部分的附加生长步骤来实现,或者通过掩模的扩散仅在有源区掺入掺杂剂来实现。COBRA正在开发基于后一种方法的低损失通用工艺。

提高射频性能。通过在半绝缘(SI)衬底上而不是n型衬底上制造整个光路,可以获得性能的重要改进,正如HHI目前已经为其高速接收器工艺所做的那样。从n型衬底转到到SI衬底需要重新设计工艺,以便用可以从晶片顶部访问的横向n电接触代替晶片背面的公共n电接触接触。基于SI的工艺有两个优点:导电n型接地平面的去除允许更高速度的操作,SI衬底上的检测器和调制器都可以在超过40GHz的频率下工作;此外,不同元件的n接触层可以被分离,这允许平衡光电检测器的集成,其中一个二极管的p接触被连接到另一二极管的n接触。Oclaro和COBRA都致力于在SI基板上引入通用工艺。

自由选择带隙。另一个重要平台能力是允许自由选择有源材料的带隙。目前,相同的平台工艺可以应用于具有包含不同增益材料(例如体层、量子阱层或量子点层)增益部分的晶圆,但在同一晶片上只能实现有限数量的垂直结构(通常为2或3个)。因此,在MPW运行中,必须做出适用于该运行中所有参与者的选择,在单片晶圆中选择不灵活。

在带隙特性方面提供更多灵活性的工艺是选择性区域生长SAG。这里,通过掩蔽有源区之外的区域来提高有源区中的生长速率。在MOVPE生长过程中,材料从遮蔽区域迁移到生长速率变高的未遮蔽区域。如果波导由MQW堆叠组成,则有源区中的阱将变得更厚,这将导致带隙的减小。可以通过调整掩模的宽度和掩模区间隙控制生长来控制带隙减少。通过这种方式,可以在宽至100nm的带隙范围内单独控制每个有源区[49]。因为带隙变化是由扩散过程引起的,所以具有不同带隙的区域之间的连接将是平滑的。为了防止层厚度的变化变得太大,SAG步骤通常限于有源层,并且包层在未掩模的步骤中生长。因此SAG需要多次生长。

通过这种方式,可以在相同的MPW上设计整个范围的垂直结构,这使设计者在设计有源层特性方面有很大的自由度。首先,可以针对同一晶片上的多个功能优化垂直结构:激光器、半导体放大器、电吸收调制器、相位调制器、无源波导等。其次,可以针对每个工作波长优化层堆叠。例如,在WDM发射器PIC中,每个激光器和每个电吸收调制器可以针对每个波长信道单独优化。在PARADIGM项目中,III–V实验室正在与Fraunhofer HHI合作,在其通用平台技术的未来版本中实施该技术。在该版本中,由InGaAlAs而不是InGaAsP制成的有源MQW结构将用于改进的高温操作。

2.2. 波导蚀刻

第二个工艺模块是波导蚀刻。在COBRA工艺中,四个蚀刻步骤用于创建四个不同的蚀刻水平,如图8b所示。最深的能级延伸到衬底中,并用于深刻波导、深刻相位调制器和检测器部分(反向偏置SOA部分)以及提供高折射率对比度。深刻波导用于需要高折射率对比的地方,例如在小半径弯曲和紧凑型MMI耦合器、MMI反射器和AWG复用器中。

浅刻水平用于定义浅刻波导和放大器部分,其中通过有源区的蚀刻将导致增加的表面复合。由于减少了侧壁散射,浅波导显示出较低的传输损耗;它们用于低损耗互连。

施加第三蚀刻水平以提供不同有源元件之间的电隔离。隔离是通过去除高导电p掺杂顶部包层,向下到波导层正上方的低掺杂包层来实现的。此外,如图3b所示,在偏振旋转部分中使用该蚀刻水平。

第四个也是最浅的蚀刻步骤用于从无源波导中去除重p掺杂的三元(InGaAs)接触层,在那里它会导致波导损耗。此外,在平坦化之后,它允许在波导上布线电互连,如图8d所示。这很重要,因为它允许将电连接路由到芯片的边缘。

DUV光刻。波导和基于波导的元件(如AWG和MMI耦合器)的质量在很大程度上取决于光刻和蚀刻工艺的质量。COBRA最近安装了193 nm DUV扫描仪(ASML PAS 5550/1100),分辨率低至90 nm。该机器已被ASML用于处理3′和4′InP晶片,迄今为止,它是全球唯一一台具有此分辨率的机器,可以处理InP晶片。该机器的分辨率是目前用于InP晶片的最佳光学光刻工具(I线步进器)的三倍,后者的分辨率为250 nm。

这种分辨率的提高导致了工艺性能和平台能力的大幅提高。一个重要的优点是DBR和DFB光栅可以用快速光学光刻代替电子束光刻或全息术打印。但是还有更多的优点。通过减少阵列波导之间的间隙的闭合,AWG的插入损耗将从几dB减少到小于1dB。随着分辨率的提高,MMI耦合器和偏振变换器中关键尺寸的控制将变得更好,从而能够更准确地规范器件性能,并带来更高的场。此外,可以预期,由于更平滑的波导边缘,波导传输损耗将变得更低。

用于193nm DUV光刻的非常薄的光致抗蚀剂不适合用作蚀刻厚层的掩模,并且不能容忍超过100nm的高度阶跃。如图8所示,在第一个蚀刻步骤之后,高度差将大很多倍。因此,在每个蚀刻步骤之后将需要平坦化步骤,类似于CMOS处理中所做的步骤。此外,对晶片平坦度的要求比InP衬底制造商今天所能提供的要求更严格。因此,从I线到193nm DU光刻需要对工艺技术进行重大调整。目前,在ASML的支持下,COBRA正在研究这种工艺适应性。

2.3. 平坦化和钝化

在蚀刻工艺之后,深度蚀刻的相位调制器和检测器的侧壁必须进行钝化和保护,如图8c所示。在COBRA工艺中,这是通过沉积聚酰亚胺层来实现的,这也减少了芯片上的高度差(平坦化)。钝化层对于在反向偏置的相位调制器和检测器部分中获得低暗电流是必要的。为了便于后续的光刻步骤,平坦化是必要的,其中不同台面之间的高度差异很大,使接触区域的开口和金属接触的定义等工艺步骤复杂化。平坦化层也用作电极与接合焊盘或探针焊盘之间的金属互连的衬底层。它在必须形成接触开口的所有台面处具有良好定义的高度,并且它覆盖了为了互连目的需要金属交叉的台面。

如前一节所述,DUV光刻的引入对表面平面度提出了更严格的要求。COBRA正在开发BCB平坦化层的化学-机械抛光,以满足这些要求。

2.4. 金属化和互连

最后一个工艺模块用于接触和金属化,如图8d所示。首先对聚酰亚胺平坦化层进行光刻图案化,并对剩余部分进行蚀刻,直到有源台面被打开。接下来,通过光刻沉积薄的Ti-Pt-Au接触层,以获得具有低串联电阻的接触。对准不是关键的,因为所选择的接触比台面更宽。在剥离上接触层之后,沉积下接触层。两个接触层同时退火。对于键合焊盘和金属互连图案的定义,晶片的上侧覆盖有薄的金籽晶层,然后是厚的抗蚀剂层,该层在我们需要金属路径的地方开口。接下来,通过抗蚀剂掩模中的开口电镀厚的金图案,最后将整个金图案稍微回蚀一点,以去除种子层。

[1] Miller S E 1969 Integrated optics: an introduction Bell Syst. Tech. J. 48 2059–69

[2] Tien P K 1977 Integrated optics and new wave phenomena in optical waveguide Rev. Mod. Phys. 49 361–420

[3] Koren U et al 1989 WDM light source with integrated QW tunable lasers and optical amplifier Appl. Phys. Lett. 54 2056–8

[4] Cremer C 1991 Grating spectrograph in InGaAsP/lnP for dense wavelength division multiplexing Appl. Phys. Lett. 59 627–9

[5] Duthie P J et al 1991 Guided wave switch array using electrooptic and carrier depletion effects in indium phosphide Electron. Lett. 27 1747–8

[6] Gustavsson M et al 1992 Monolithically integrated 4 × 4 InGaAsP/InP laser amplifier gate switch arrays Electron. Lett. 28 2223–5

[7] Kaiser R 1994 Monolithically integrated polarization diversity heterodyne receivers on GaInAsP/InP Electron. Lett. 30 1446–7

[8] Smit M K 1988 New focusing and dispersive planar component based on an optical phased array Electron. Lett. 24 385–6 [9] Takahashi H et al 1990 Arrayed-waveguide grating for wavelength division multi/demultiplexer with nanometer resolution Electron. Lett. 26 87–8 [10] Dragone C 1991 An N × N optical multiplexer using a planar arrangement of two star couplers IEEE Photon. Technol. Lett. 3 812–5

[11] Amersfoort M R et al 1993 High performance 4-channel PHASAR wavelength demultiplexer integrated with photodetectors Proc. 19th Eur. Conf. Opt. Comm. (ECOC‘93) Post deadline Papers (Montreux, Switzerland, September 12–16) vol 3 pp 49–52

[12] Zirngibl M et al 1995 WDM receiver by monolithic integration of an optical preamplifier, waveguide grating router and photodiode array Electron. Lett. 31 581–2

[13] Steenbergen C A M et al 1996 Compact low loss 8 × 10 GHz polarization independent WDM receiver 22nd Eur. Conf. on Opt. Comm (ECOC’96, Oslo) vol 1 pp 129–32

[14] Zirngibl M and Joyner C H 1994 12 frequency WDM laser based on a transmissive waveguide grating router Electron. Lett. 30 701–2

[15] Zirngibl M et al 1996 An 18-channel multifrequency laser IEEE Photonics Technol. Lett. 8 870–2

[16] Staring A A M et al 1996 A compact nine-channel multiwavelength laser IEEE Photonics Technol. Lett. 8 1139–41

[17] Zirngibl M and Joyner C H 1994 High performance, 12 frequency optical multichannel controller Electron. Lett. 30 700–1

[18] Ishii H et al 1998 Monolithically integrated WDM channel selectors on InP substrates Proc. 24th Eur. Conf. Opt. Comm. (ECOC’98) (Madrid, Spain, 20–24 September) pp 329–30

[19] Ménézo S et al 1999 10-wavelength 200 GHz channel spacing emitter integrating DBR lasers with a PHASAR on InP for WDM applications IEEE Photonics Technol. Lett. 11 785–7

[20] Mestric R et al 2000 Sixteen-channel wavelength selector monolithically integrated on InP Proc. Opt. Fibre Comm. Conf. (OFC 2000) (Baltimore, March 2000) 81-83

[21] Kikuchi N et al 2001 Monolithically integrated 64-channel WDM channel selector on InP substrate Proc. 27th Eur. Conf. on Opt. Comm. (ECOC’O1) (Amsterdam) pp 4–5

[22] Herben C G P et al 1999 Polarization independent dilated WDM cross-connect on InP IEEE Photonics Technol. Lett. 11 1599–601

[23] Chandrasekhar S et al 1995 Monolithic eight-wavelength demultiplexed receiver for dense WDM applications IEEE Photonics Technol. Lett. 7 1342–4

[24] Tolstikhin V I 2003 44-channel optical power monitor based on an Echelle grating demultiplexer and a waveguide photodetector array monolithically integrated on an InP substrate Proc. Opt. Fibre Comm. Conf. (OFC 2003) Post Deadline Paper PD37-1 (Atlanta, GA, USA, March 23–28)

[25] ASIP/Three-Five Photonics 2004 (www.rle.mit.edu/cips/ conference04/Pennings_ASIP.pdf)

[26] Nagarajan R et al 2005 Large-scale photonic integrated circuits IEEE J. Sel. Top. Quant. Electron. 11 50–65

[27] Nagarajan R et al 2006 Single-chip 40-channel InP transmitter photonic integrated circuit capable of aggregate data rate of 1.6 Tbit /s Electron. Lett. 42 771–3

[28] Nicholes S C 2009 The world’s first InP 8 × 8 monolithic tunable optical router (MOTOR) operating at 40 Gbps line rate per port Opt. Fibre Com (OFC 2009) Postdeadline Paper PDPB1 (San Diego, CA, USA, 22–26 March)

[29] Wang H, Wonfor A, Williams K A, Penty R V and White I H 2009 Demonstration of a lossless monolithic 16 × 16 QW SOA switch Proc. 35th Conf. on Optical Comm. (ECOC 2009) Post-deadline Paper (Vienna, 20–24 September)

[30] Soares F M 2010 Monolithically integrated InP wafer-scale 100-channel × 10 GHz AWG and michelson interferometers for 1 THz-bandwidth optical arbitrary waveform generation Opt. Fibre Com (OFC 2010) (San Diego, CA, USA, 21–25 March)paper OThS1

[31] Corzine S W 2010 Large-scale InP transmitter PICs for PMDQPSK fibre transmission systems Photon. Technol. Lett. 22 1015–7 [32] Stabile R, Albores-Mejia A and Williams K A Monolithic active-passive 16 × 16 optoelectronic switch Opt. Lett. 37 4666–8

[33] Stabile R, Rohit A and Williams K A 2014 Monolithically integrated 8 × 8 space and wavelength selective crossconnect J. Lightwave Technol. 32 201-7

[34] Coldren L A et al 2010 High performance InP-based photonic ICs—a tutorial J. Lightwave Technol. 29 554–70

[35] Moore G E 1965 Cramming more components onto integrated circuits Electronics 38 114–7

[36] Moore’s law http://en.wikipedia.org/wiki/Moore’s_law

[37] Smit M K InP photonic integrated circuits Procs. 15th Ann. Meeting of the IEEE Lasers and Electro-Optics Society LEOS 2002 2 pp 843–4

[38] The FP6 Network of Excellence ePIXnet www.epixnet.org

[39] EU-FP7 NMP SME project EuroPIC www.europic.jeppix.eu

[40] EU-FP7 IST Integrating Project Paradigm www.paradigm. jeppix.eu

[41] Dutch Smartmix project MEMPHIS (Merging Electronics and Micro&Nano-Photonics in Integrated Systems) www. smartmix-memphis.nl/

[42] Dutch IOP Photonic Devices www.agentschapnl.nl/subsidiesregelingen/iops/iop-photonic-devices

[43] STW (Dutch Technology Foundation) Perspective Program 2010: Generic Technologies for Integrated Photonics (GTIP)

[44] Joint European Platform for Photonic Integration of Components and Circuits (JePPIX) www.JePPIX.eu

[45] M K Smit M K, Leijtens X J M, Bente E A J M, Tol J J G M van der, Ambrosius H P M M, Robbins D J, Wale M, Grote N and Schell M 2011 Generic foundry model for InP-based photonics IET Optoelectron. 5 187–94

[46] Menon V M, Xia F and Forrest S R 2005 Photonic integration using asymmetric twin-waveguide (ATG) technology: part II —devices JSTQE 11 30–42

[47] Tolstikhin V 2011 Regrowth-free multi-guide vertical integration in InP for optical communications Proc. IPRM 2011 (Berlin, Germany, May 22–26)

[48] Skogen E J et al 2005 Monolithically integrated active components: a quantum-well intermixing approach IEEE J. Sel. Top. Quantum Electron. 11 863–9

[49] Debregeas H, Decobert J, Lagay N, Guillamet R, Carrara D, Patard O, Kazmierski C and Brenot R 2012 Selective-areagrowth technology for flexible active building blocks Procs. Integrated Photonics Research, Silicon and Nanophotonics (IPRSN) (Colorado: Colorado Springs) Paper IM2A.3 doi:10.1364/IPRSN.2012.IM2A.3

注:本文由天津见合八方光电科技有限公司挑选并翻译,旨在推广和分享相关SOA基础知识,助力SOA技术的发展和应用。特此告知,本文系经过人工翻译而成,虽本公司尽最大努力保证翻译准确性,但不排除存在误差、遗漏或语义解读导致的不完全准确性,建议读者阅读原文或对照阅读,也欢迎指出错误,共同进步。

天津见合八方光电科技有限公司(http://tj.jhbf.cc),是一家专注半导体光放大器SOA研发和生产的高科技企业,目前已推出多款半导体光放大器SOA产品(1060nm, 1310nm, 1550nm),公司已建立了万级超净间实验室,拥有较为全面的光芯片的生产加工、测试和封装设备,并具有光芯片的混合集成微封装能力。目前公司正在进行小型SOA器件、DFB+SOA的混合集成器件、可见光波长SOA器件、大功率SOA器件的研发工作,并可对外承接各种光电器件测试、封装和加工服务。

1108

1108

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?