中断控制机制

CPU运行过程中,如何知道各类外设发生了某些不预期的事件,比如串口收到了数据、按键被按下?

此时ARM有两种中断机制:

1.查询方式。程序不断地查询各设备的状态,并作出相应的反应。该方式实现比较简单,常用在比较单一的系统中,比如一个温控系统中可以使用查询方式不断检测温度的变化。特点:实现简单;但CPU利用率很低,不适合多任务的系统。

2.中断方式。当事件发生时,硬件会设置某个寄存器;CPU在执行完一个指令时,查看这个寄存器,如果所关注的事件发生了,则中断当前程序,跳转到一个固定的地址处理这个事件,处理完后返回到被终端的程序中继续运行。特点:实现相对复杂,但效率较高,是常用的方法。

中断处理流程

1.中断控制器汇集各类外设发出的中断信号,然后通知CPU。

2.CPU保存当前程序的运行环境,然后调用中断服务程序(ISR)来处理中断。

3.在ISR中通过读取外设的相关寄存器来识别终端的类型,并进行相应的处理。

4.清除中断。通过读写相关中断控制寄存器和外设相关寄存器来实现。

5.恢复被中断程序的执行环境,继续执行被中断的程序。

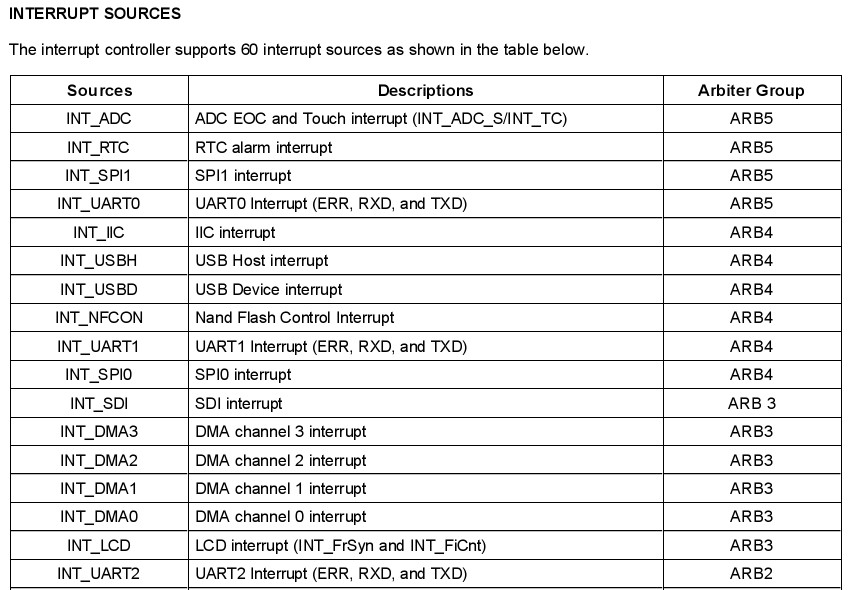

S3c2440的中断源和子中断源

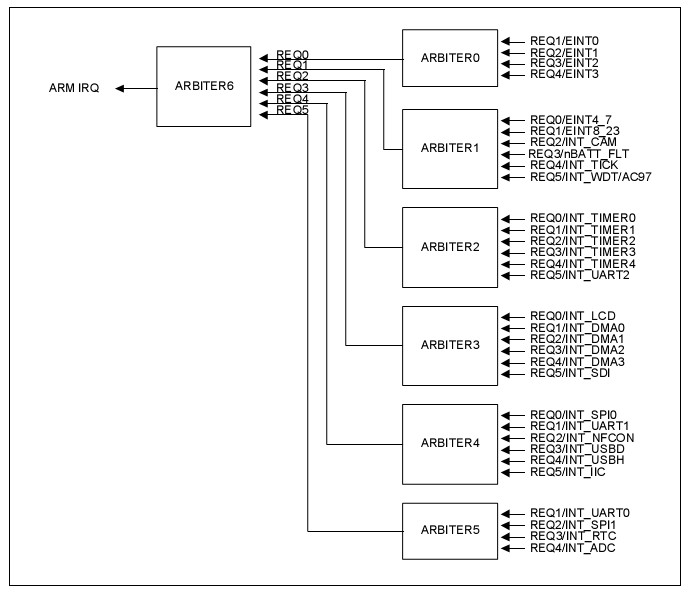

S3c2440有60个中断源(含子中断源),如下图:

中断通知

外设产生的中断如何被通知到CPU?

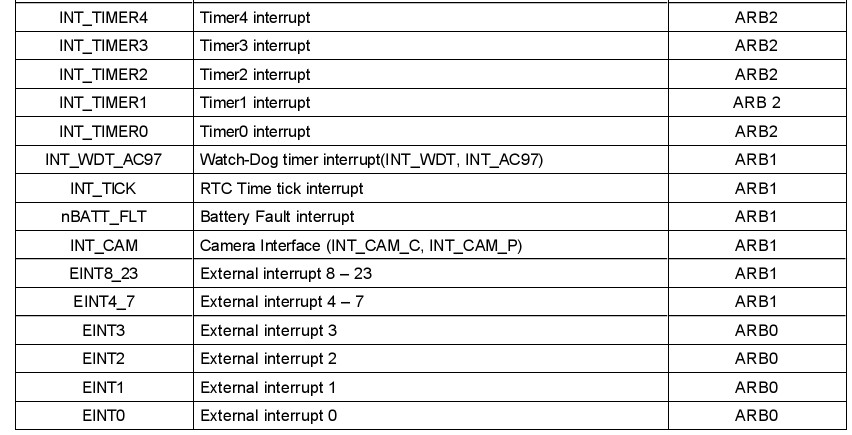

The arbitration procedure depends on the hardware priority logic and the result is written to the interrupt pending

register, which helps users notify which interrupt is generated out of various interrupt sources.

根据上图,下面着重介绍其中的几个重要寄存器:

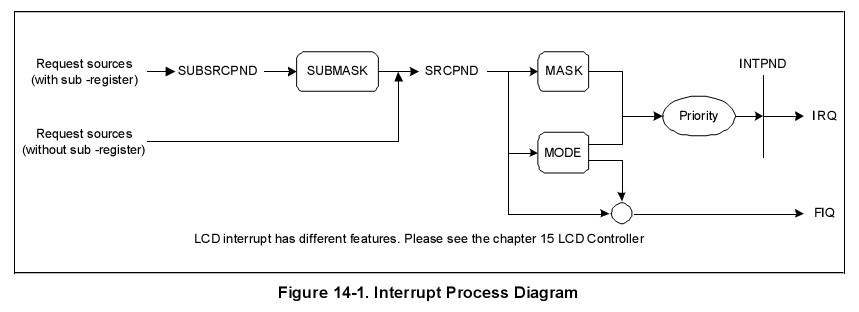

SUBSRCPND:SUBSRCPND寄存器用来标明子中断(如:INT_RXD0)是否发生。S3c2440有15个子中断,SUBSRCPND中每一位对应一个子中断,当这些子中断发生时,相应的位被置为1。清除子中断只需向SUBSRCPND寄存器中相应位写入0。

INTSUBMSK:INTSUBMSK寄存器用来屏蔽SUBSRCPND寄存器所标示的中断。INTSUBMSK寄存器中某位被设为1时,相应的子中断被屏蔽。设为0时,表示子中断被允许。

SRCPND:SRCPND中每一位用来标明一个(或一类)中断是否已经发生。例如:SUBSRCPND

寄存器中的子中断INT_RXD0发生了,且没有被INTSUBMSK屏蔽,则SRCPND的INT_UART0位被置1。SRCPND寄存器的清除与SUBSRCPND寄存器相似,若想清除某一位,往此位写入0。

INTMSK:INTMSK寄存器用来屏蔽SRCPND所标示的中断。INTMSK某位被

设置为1时,对应的中断被屏蔽,设置为0时,相应中断被允许。INTMSK只能屏蔽设置为IRQ的中断,不能屏蔽设置为FIQ的中断。

INTMOD:INTMOD寄存器中某位被设置为1时,它所对应的中断源会被设置为FIQ模式,即此中断发生时,CPU将进入快速中断模式。这通常用来处理特别紧急的中断。当该位被置为0时,表示为

IRQ模式。

FIQ & IRQ:IRQ模式下,中断处理程序需要自己保存R8到R12这几个寄存器,退出中断处理时需要自己恢复这几个寄存器,而FIQ模式由于这几个寄存器都有back寄存器(fiq_R8...),模式切换时CPU自动保存这些值到back寄存器,退出FIQ模式时自动恢复,所以这个过程FIQ比IRQ快。FIQ比IRQ有更高的优先级,如果FIQ和IRQ同时产生,那么FIQ先处理。

IRQ优先级选择-分析:The priority logic for 32 interrupt requests is composed of seven rotation based arbiters: six first-level arbiters and one

second-level arbiter as shown in Figure 14-1 below.

INTERRUPT PRIORITY

Each arbiter can handle six interrupt requests based on the one bit arbiter mode control (ARB_MODE) and two bits

of selection control signals (ARB_SEL) as follows:

— If ARB_SEL bits are 00b, the priority order is REQ0, REQ1, REQ2, REQ3, REQ4, and REQ5.

— If ARB_SEL bits are 01b, the priority order is REQ0, REQ2, REQ3, REQ4, REQ1, and REQ5.

— If ARB_SEL bits are 10b, the priority order is REQ0, REQ3, REQ4, REQ1, REQ2, and REQ5.

— If ARB_SEL bits are 11b, the priority order is REQ0, REQ4, REQ1, REQ2, REQ3, and REQ5.

Note that REQ0 of an arbiter always has the highest priority, and REQ5 has the lowest one. In addition, by changing

the ARB_SEL bits, we can rotate the priority of REQ1 to REQ4.

Here, if ARB_MODE bit is set to 0, ARB_SEL bits doesn’t change automatically changed, making the arbiter to

operate in the fixed priority mode (note that even in this mode, we can reconfigure the priority by manually changing

the ARB_SEL bits). On the other hand, if ARB_MODE bit is 1, ARB_SEL bits are changed in rotation fashion, e.g., if

REQ1 is serviced, ARB_SEL bits are changed to 01b automatically so as to put REQ1 into the lowest priority. The

detailed rules of ARB_SEL change are as follows:

— If REQ0 or REQ5 is serviced, ARB_SEL bits are not changed at all.

— If REQ1 is serviced, ARB_SEL bits are changed to 01b.

— If REQ2 is serviced, ARB_SEL bits are changed to 10b.

— If REQ3 is serviced, ARB_SEL bits are changed to 11b.

— If REQ4 is serviced, ARB_SEL bits are changed to 00b.

最后,IRQ中断通过INTPND寄存器产生:经过中断优先级仲裁器选出优先级高的中断后,这个中断在INTPND寄存器中的相应位被置1,随后,CPU进入中断模式处理它。同一时间内,此寄存器只有一位被置1,在ISR中可以根据这个位确定中断类型。清除该中断时,往这个位写入0。

1125

1125

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?