这里的模板,不是指C++的template,而是verilog或者VHDL的模板。

在verilog最烦的,还是写begin end,所以把这些重复的工作预先做好,那么下次再也不用烦了。

要使用模板,还是有好几种方法的。

一、记事本。

二、脚本。

三、配置编辑器。

四、使用quartus或ISE自带的模板。

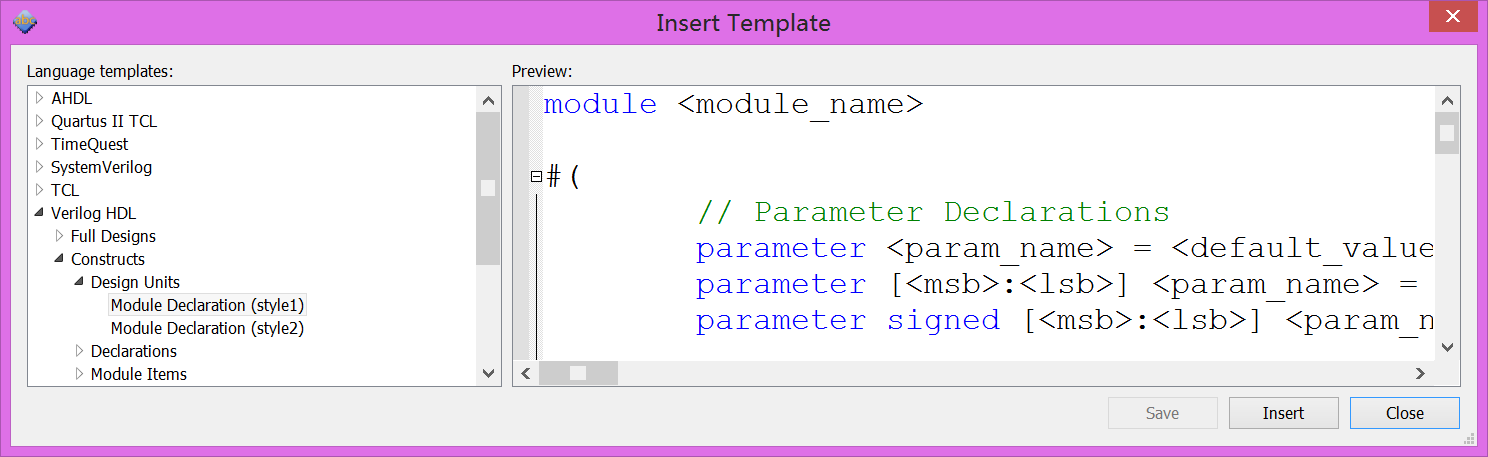

由于quartus和ISE自带的模板是相当恶心的,所以不推荐,理由如下:

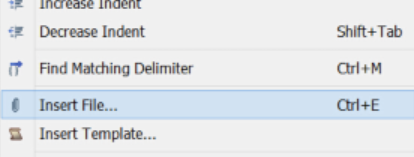

点上图所示位置,插入模板,会出现如下图所示。

你会花大量时间去删掉那些垃圾(如<param_name>),效率太慢,还不如不用。

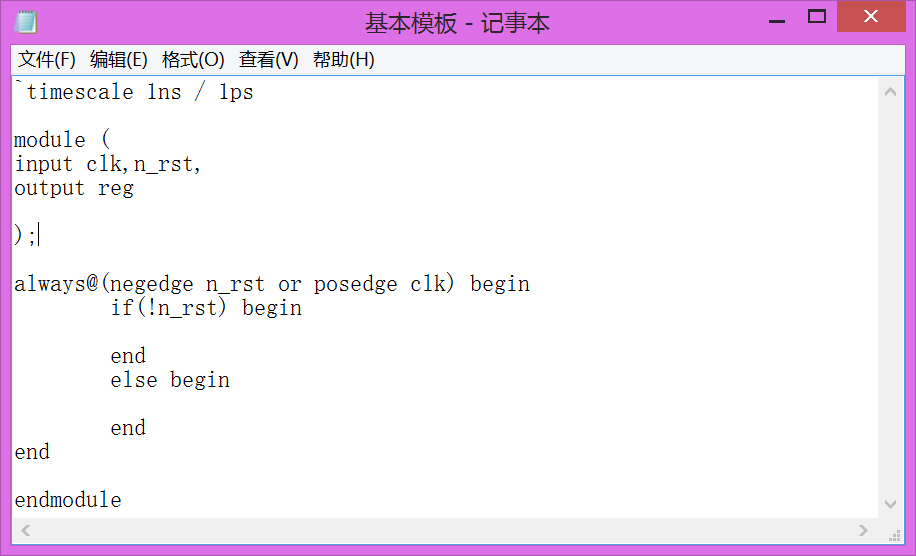

所以,我们还是得自制模板,这里介绍最简单的用记事本自制模板。

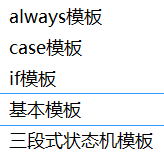

很简单,用记事本记录你想要的模板即可。如下图所示。

然后在quartus的编辑界面下使用Ctrl+E插入文件。

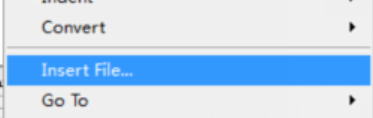

ISE也有,在菜单栏的Edit下,但是没有快捷键。

选了一次文件之后,就自动记录路径,下次插入就相当方便。

这样就可以大大提高工作效率了,我这里就写了几个模板。

写的模板最好能全选使用,不要在一个记事本下写几个模板。

但是用记事本的方法比较死板,某些功能无法实现,如:case语句下的由4'h0到4'hf,这16条分支,写起来是相当烦人的。要实现这种功能就得靠脚本或者配置编辑器了,这部分以后再介绍。

注意:对语法不熟悉或者打字比较慢的人(英文录入速度低于180字母/分的),不建议使用模板。

7万+

7万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?