计算机系统总线详解:AXI、PCIe、DDR及其应用场景

引言

在现代计算机系统中,总线是连接各个硬件组件的"数字高速公路",负责数据传输、地址映射和控制信号传递。不同类型的总线各有特点,适用于不同的应用场景。理解这些总线技术对于系统设计、性能优化和故障诊断都至关重要。本文将详细剖析AXI、PCIe、DDR等主要总线技术的特点、异同及应用场景,帮助读者全面了解现代计算机系统中的互连架构。

总线分类框架

计算机系统中的总线可以按照其功能、性能和应用位置进行分类:

计算机系统总线

│

├── 片上互连总线 (On-chip Bus)

│ ├── AMBA系列 (ARM)

│ │ ├── AXI (高级扩展接口)

│ │ │ ├── AXI4

│ │ │ ├── AXI4-Lite

│ │ │ └── AXI4-Stream

│ │ ├── AHB (高级高性能总线)

│ │ └── APB (高级外设总线)

│ ├── Wishbone (开源)

│ └── OCP (开放核心协议)

│

├── 内存总线 (Memory Bus)

│ ├── DDR (双倍数据率)

│ │ ├── DDR4

│ │ ├── DDR5

│ │ └── LPDDR (低功耗DDR)

│ └── HBM (高带宽内存)

│

├── 系统/扩展总线 (System/Expansion Bus)

│ ├── PCIe (外围组件互连)

│ │ ├── PCIe 3.0/4.0/5.0/6.0

│ │ └── CXL (计算快速链接)

│ ├── Thunderbolt

│ └── DMI (直接媒体接口)

│

├── 存储总线 (Storage Bus)

│ ├── SATA (串行ATA)

│ ├── SAS (串行附加SCSI)

│ ├── NVMe (非易失性内存快速)

│ └── UFS (通用闪存存储)

│

└── 外设总线 (Peripheral Bus)

├── 高速外设总线

│ ├── USB (通用串行总线)

│ └── Thunderbolt

└── 低速外设总线

├── I²C (集成电路间总线)

├── SPI (串行外设接口)

├── UART (通用异步收发器)

└── CAN (控制器局域网)

AXI总线详解

基本概念

AXI(Advanced eXtensible Interface,高级可扩展接口)是ARM公司开发的一种高性能片上互连总线协议,是AMBA(Advanced Microcontroller Bus Architecture,高级微控制器总线架构)规范的一部分。它被广泛应用于SoC(System-on-Chip,系统级芯片)设计中,用于连接处理器、内存控制器和各种片上外设。

架构特点

AXI的核心设计理念是通过多个独立通道实现高效并行传输:

-

五个独立通道:

- 读地址通道(AR)

- 读数据通道(R)

- 写地址通道(AW)

- 写数据通道(W)

- 写响应通道(B)

-

主要特性:

- 乱序执行:支持多个未完成事务的乱序完成

- 地址/数据分离:地址和数据传输分离,提高并行性

- 突发传输:支持多种突发类型,提高传输效率

- 多种数据宽度:支持8/16/32/64/128/256/512位数据宽度

- QoS支持:提供服务质量控制机制

-

AXI协议版本:

- AXI3:早期版本,最大支持16次突发传输

- AXI4:支持最多256次突发传输,增强QoS功能

- AXI4-Lite:简化版本,用于低带宽的控制寄存器访问

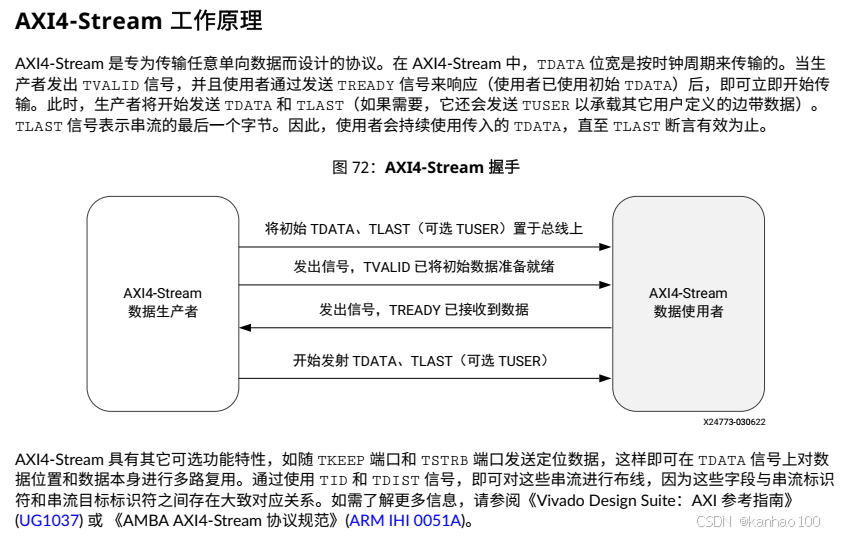

- AXI4-Stream:专为数据流设计,无地址阶段,适合视频、音频处理

工作原理

AXI总线采用主从(Master-Slave)架构,主设备发起事务,从设备响应事务。以读操作为例:

- 主设备通过读地址通道发送读请求(地址、突发长度等)

- 从设备通过读数据通道返回请求的数据

- 整个过程中,地址和数据传输可以并行进行

写操作同样使用独立的写地址通道和写数据通道,并通过写响应通道确认完成状态。

应用场景

AXI主要应用于:

- SoC内部高性能模块间通信

- 处理器核心与内存控制器的连接

- 高速外设控制器(如GPU、视频编解码器)与处理器的连接

- FPGA内部模块互连

- 硬件加速器与主处理器的通信

PCIe总线详解

基本概念

PCIe(Peripheral Component Interconnect Express,外围组件互连)是一种高速串行计算机扩展总线标准,用于连接主板与各种高性能外部设备,如显卡、存储设备、网络适配器等。

架构特点

PCIe采用点对点串行连接架构,具有以下特点:

-

分层协议:

- 事务层:处理读写请求和完成包

- 数据链路层:提供可靠的数据传输,包括错误检测和纠正

- 物理层:处理电气接口、信号编码和解码

-

通道(Lane)结构:

- 每个通道由一对差分信号线组成(发送和接收)

- 多个通道可以组合形成更宽的链路(x1, x2, x4, x8, x16等)

- 通道数量越多,带宽越高

-

数据传输:

- 基于分组(Packet)的传输机制

- 支持TLP(Transaction Layer Packet)和DLLP(Data Link Layer Packet)

- 使用8b/10b编码(PCIe 3.0之前)或128b/130b编码(PCIe 3.0及以后)

-

热插拔支持:允许在系统运行时添加或移除设备(需硬件支持)

PCIe各代技术对比

| 代际 | 发布年份 | 每通道单向带宽 | x16链路总带宽 | 编码方式 |

|---|---|---|---|---|

| PCIe 1.0 | 2003 | 250 MB/s | 8 GB/s | 8b/10b |

| PCIe 2.0 | 2007 | 500 MB/s | 16 GB/s | 8b/10b |

| PCIe 3.0 | 2010 | 985 MB/s | 31.5 GB/s | 128b/130b |

| PCIe 4.0 | 2017 | 1969 MB/s | 63 GB/s | 128b/130b |

| PCIe 5.0 | 2019 | 3938 MB/s | 126 GB/s | 128b/130b |

| PCIe 6.0 | 2022 | 7877 MB/s | 252 GB/s | PAM4+FLIT |

应用场景

PCIe广泛应用于:

- 显卡连接(通常使用x16通道)

- 高性能存储设备(NVMe SSD通常使用x4通道)

- 网络适配器(从x1到x16不等)

- AI加速卡和计算卡

- 扩展卡(如音频卡、视频采集卡等)

- 外部GPU盒(通过Thunderbolt接口)

DDR内存总线详解

基本概念

DDR(Double Data Rate,双倍数据率)是一种内存总线技术,通过在时钟信号的上升沿和下降沿都传输数据,实现"双倍"数据传输率。DDR总线连接处理器(或内存控制器)与DRAM内存模块。

架构特点

-

总线结构:

- 命令/地址总线:从处理器到内存的单向总线

- 数据总线:双向总线,通常为64位宽(单通道)

- 控制信号:包括时钟、片选、行/列地址选通等

-

双倍数据率:

- 在时钟信号的上升沿和下降沿都传输数据

- 相比SDR(单数据率),数据传输率翻倍

-

突发传输:

- 支持突发读写操作

- 一次地址访问可以连续传输多个数据

-

预取技术:

- DDR4采用8n预取,每次访问读取8个数据字

- DDR5采用16n预取,进一步提高带宽

DDR各代技术对比

| 特性 | DDR3 | DDR4 | DDR5 |

|---|---|---|---|

| 发布年份 | 2007 | 2014 | 2020 |

| 工作电压 | 1.5V/1.35V | 1.2V | 1.1V |

| 最高传输率 | 2133 MT/s | 3200 MT/s | 6400+ MT/s |

| 最大容量(DIMM) | 16GB | 64GB | 256GB |

| 预取位数 | 8位 | 8位 | 16位 |

| 通道架构 | 单通道 | 单通道 | 双子通道 |

| ECC支持 | 可选 | 可选 | 片上ECC |

应用场景

DDR内存总线主要应用于:

- 处理器与系统主内存之间的连接

- 服务器内存系统(通常采用多通道配置)

- 高性能计算系统

- 图形处理器与显存的连接(GDDR是针对图形优化的DDR变种)

其他重要总线技术

片上互连总线

1. AHB (Advanced High-performance Bus)

特点:

- AMBA标准的一部分,比AXI简单

- 单一共享的地址/数据总线

- 支持流水线操作和突发传输

- 主要用于中等性能要求的片上连接

应用场景:

- 中低端微控制器

- 连接中等性能的外设控制器

- 作为AXI网络的次级总线

2. APB (Advanced Peripheral Bus)

特点:

- AMBA标准中最简单的总线

- 非流水线,单次传输

- 低功耗,资源占用少

- 简单接口,适合低速外设

应用场景:

- 连接低速外设(如UART、GPIO、I²C控制器)

- 配置寄存器访问

- 低功耗设计

高速系统互连总线

1. CXL (Compute Express Link)

特点:

- 基于PCIe物理层的开放标准

- 维持内存一致性,支持共享内存

- 三种协议:CXL.io(兼容PCIe)、CXL.cache(缓存一致性)、CXL.mem(内存语义)

- 专为异构计算和内存扩展设计

应用场景:

- CPU与加速器(如GPU、FPGA、专用AI芯片)的连接

- 内存扩展和内存池化

- 数据中心和高性能计算

- 大规模AI训练系统

2. Thunderbolt

特点:

- 结合PCIe和DisplayPort的高速接口

- Thunderbolt 4提供40Gbps带宽

- 支持菊链连接多个设备

- 可同时传输数据、视频信号和供电(最高100W)

应用场景:

- 笔记本电脑扩展坞

- 外部GPU解决方案

- 高分辨率显示器连接

- 高性能外部存储设备

存储总线

1. NVMe (Non-Volatile Memory Express)

特点:

- 专为闪存设计的高性能存储协议

- 直接通过PCIe连接,减少延迟

- 高度并行,支持多队列和深队列

- 低CPU开销,高IOPS

应用场景:

- 高性能SSD

- 企业级存储系统

- 实时数据处理

- 高性能计算和数据中心

2. UFS (Universal Flash Storage)

特点:

- 移动设备高性能存储接口

- 全双工通信

- 基于SCSI架构

- 相比eMMC提供更高性能和更低功耗

应用场景:

- 高端智能手机

- 平板电脑

- AR/VR设备

- 汽车信息娱乐系统

外设总线

1. USB (Universal Serial Bus)

特点:

- 通用外设连接标准

- 支持热插拔和即插即用

- 最新USB4版本提供40Gbps带宽

- 可提供电源(USB-PD可达240W)

应用场景:

- 外部存储设备

- 输入设备(键盘、鼠标)

- 外部摄像头、打印机

- 移动设备充电和数据传输

2. I²C (Inter-Integrated Circuit)

特点:

- 简单的双线制串行总线

- 主从架构,地址寻址

- 低速(标准模式100kbps,高速模式3.4Mbps)

- 资源占用极少

应用场景:

- 传感器连接

- EEPROM访问

- 低速控制接口

- 系统管理接口

3. SPI (Serial Peripheral Interface)

特点:

- 全双工串行通信

- 高速(可达数十Mbps)

- 简单的主从架构

- 片选机制

应用场景:

- 闪存芯片连接

- 显示器控制器

- 高速传感器

- ADC/DAC接口

总线技术对比

| 总线类型 | 带宽范围 | 延迟特性 | 应用领域 | 主要优势 | 主要挑战 |

|---|---|---|---|---|---|

| AXI | 高(数十~数百GB/s) | 极低(几个时钟周期) | SoC内部互连 | 高性能、多通道并行、可配置 | 复杂性高、资源消耗大 |

| PCIe | 高(x16 PCIe 5.0: ~126GB/s) | 中(数百纳秒) | 系统扩展设备 | 高带宽、可扩展、标准化 | 实现复杂、功耗较高 |

| DDR | 高(DDR4-3200: ~25.6GB/s) | 低(40-100纳秒) | 系统内存 | 成本效益高、标准化 | 信号完整性、时序要求严格 |

| CXL | 高(基于PCIe 5.0: ~64GB/s) | 低(接近内存延迟) | 异构计算、内存扩展 | 缓存一致性、内存语义 | 新标准、生态系统发展中 |

| NVMe | 高(PCIe 4.0 x4: ~8GB/s) | 低(~10微秒) | 高性能存储 | 低延迟、高IOPS | 成本较高 |

| UFS | 中(UFS 3.1: ~2.9GB/s) | 中(~100微秒) | 移动存储 | 低功耗、全双工 | 复杂性高于eMMC |

| USB | 中-高(USB4: 40Gbps) | 中(毫秒级) | 外设连接 | 通用性、易用性 | 协议开销 |

| SATA | 中(SATA III: 6Gbps) | 中(~100微秒) | 存储设备 | 成本低、广泛支持 | 带宽限制 |

| I²C | 低(100kbps-3.4Mbps) | 高(毫秒级) | 低速外设 | 简单、资源占用少 | 带宽低、距离短 |

| SPI | 低-中(最高数十Mbps) | 中(微秒级) | 中速外设 | 全双工、简单 | 设备数量受限 |

实际应用案例

现代x86台式电脑/服务器

┌─────────────────────┐

│ CPU Core │

└──────────┬──────────┘

│

┌──────────▼──────────┐ ┌──────────────────┐

│ CPU Uncore/IO Die │◄────►│ DDR4/DDR5 │

│ (内存控制器/L3缓存) │ │ Memory │

└──────────┬──────────┘ └──────────────────┘

│

┌──────────▼──────────┐ ┌──────────────────┐

│ PCIe Root Complex │◄────►│ PCIe Devices │

│ │ │ (GPU/NIC/NVMe) │

└──────────┬──────────┘ └──────────────────┘

│

┌──────────▼──────────┐ ┌──────────────────┐

│ Platform Hub │◄────►│ SATA Devices │

│ (PCH/Southbridge) │ │ USB Devices │

└──────────┬──────────┘ └──────────────────┘

│

▼

┌─────────────────────────────────────┐

│ 低速外设总线 (USB/I²C/SPI/LPC等) │

└─────────────────────────────────────┘

在现代x86系统中:

- CPU内部使用专有高速互连总线连接各个核心和缓存

- CPU通过内部内存控制器和DDR4/DDR5总线连接系统内存

- 高性能外设(如显卡、NVMe SSD)通过PCIe总线连接到CPU

- 平台控制器集线器(PCH)通过DMI总线连接到CPU

- SATA设备、USB设备等通过PCH连接到系统

- 低速外设通过I²C、SPI等总线连接到PCH

典型SoC(如手机或嵌入式系统)

┌─────────────┐ ┌─────────────┐

│ CPU Cluster │ │ GPU/DSP/NPU │

└───────┬─────┘ └───────┬─────┘

│ │

▼ ▼

┌─────────────────────────────────┐

│ AXI Interconnect │

└─┬───────────┬────────────┬──────┘

│ │ │

▼ ▼ ▼

┌───── ┐ ┌────────┐ ┌────────┐

│LPDDR │ │高速外设│ │ AHB桥接│

│控制器│ │(UFS/ │ │ │

│ │ │ USB3.0)│ │ │

└──┬ ──┘ └────────┘ └────┬───┘

│ │

▼ ▼

┌─────┐ ┌──────────┐

│LPDDR│ │ AHB总线 │

│内存 │ └─────┬────┘

└─────┘ │

▼

┌──────────┐

│ APB桥接 │

└─────┬────┘

│

▼

┌──────────┐

│ APB总线 │

│(I²C/SPI/ │

│UART等) │

└──────────┘

在典型SoC中:

- CPU、GPU、NPU等核心组件通过AXI总线互连

- 内存控制器通过LPDDR总线连接到片外内存

- 高速外设(如UFS存储、USB 3.0)直接连接到AXI总线

- 中速外设通过AHB总线连接

- 低速外设(如传感器、控制接口)通过APB总线连接

未来趋势

计算机系统总线技术正在朝着以下方向发展:

-

更高带宽:

- PCIe 7.0预计将提供双倍于PCIe 6.0的带宽

- DDR6将进一步提高内存带宽

- 高速串行总线将普遍采用PAM4等先进调制技术

-

异构计算互连:

- CXL将成为连接CPU与加速器的关键标准

- 片上网络(NoC)将取代传统总线,提供更高效的片上互连

- 定制互连架构

1586

1586

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?