前言

以下是本文的思维大纲:

什么是LockStep Core?

首先什么是Lockstep,直译过来就是“步调一致”,Lockstep由本来是由军事语境引入,用来表示齐步行军,队伍中的所有人都执行一致的动作步伐,而后引入计算机领域,应该是用于计算机容错系统,即“使用相同的、冗余的硬件组件在同一时间内处理相同的指令,从而保持多个CPU或内存精确的同步”。

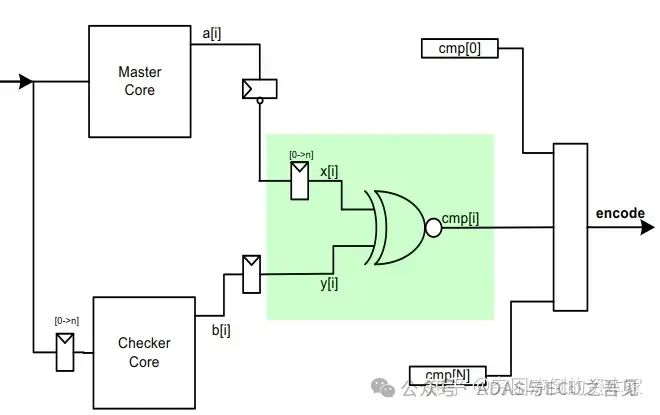

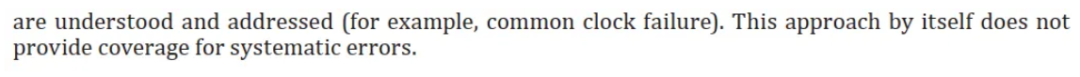

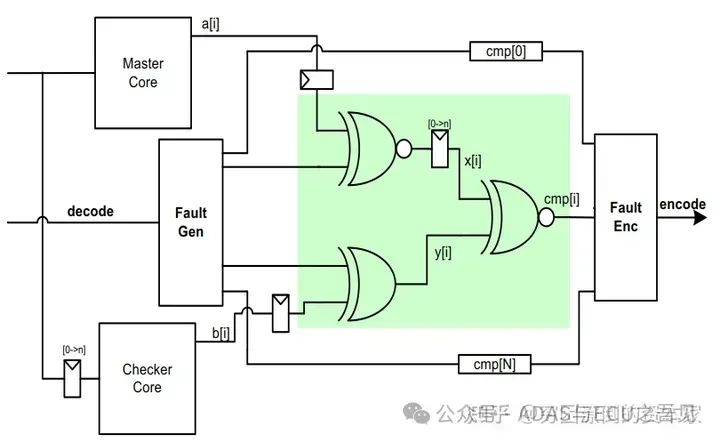

LockStep Core我们现在叫锁步核,分为Master Core 和 Checker Core,它们使用相同的输入数据,执行相同的操作,并且使用硬件比较器逐周期比较Master CPU 和Checker CPU 的输出。以英飞凌Aurix为例, 工作原理图[1]如下:

LockStep工作原理图

-

Master core和Checker core的输入是相同的

-

在Checker core输入的位置插入n个cycle的延时,通常n设置为2

-

Master Core的输出为a[i], Checker Core的输出为b[i],两个核的算法一致

-

a[i]进行一次“非”操作,也就是对其进行一次反转,然后插入n个cycle的延时,得到x[i]

-

最后x[i]和y[i]进行一次同或操作,得到cmp[i]。

-

如果cmp[i]等于1,说明lockstep出现错误,如果cmp[i]等于0,说明lockstep检查正常。

我们来总结一下

相同点:

1.两个核输入相同

2.处理算法逻辑相同(硬件)

不同点:

1.Checker Core在输入端做了延时,Master Core在输出端做了延时,但是延时时间是相等的

2.Master Core做了反转,Checker Core没有做反转,这样做是为了防止共模干扰。

所以在正常情况下,x[i]和y[i]必然是严格相反的,这样按位同或的输出值必然是0,这就证明了此时两个CPU都是正常工作的。

而且LockStep是纯硬件电路的冗余与保护,所以不会影响软件运行。英飞凌Aurix的lockstep CPU还复制了以下区域:

-

The TriCore TC16E or TC16P core

-

The CPU SFR and CSFR

-

The master and slave interfaces to SRI

-

The master interface to SPB

-

The interface to the interrupt router

-

The interface to the SCU

-

The interface to the program memories (PMI)

-

The interfaces to the data memories (DMI)

LockStep有什么作用?

英飞凌的安全手册中写道:“锁步通过硬件冗余的方式检测 TriCore CPU 的永久性和暂时性故障”

有点抽象,我们不妨自己尝试取分析和思考一下,到底什么会“永久性和暂时性故障”。

有点抽象

分析LockStep的作用,我们可以从故障的角度来思考,什么情况下会出现故障,

1.延时电路失效,造成比较信号出现错位

2.CPU硬件失效(ALU算术逻辑单元),造成计算值错误

3.非门失效,造成输出结果反转失败

4.输出路径出现电路的短路,断路等失效,造成结果错误

如果LockStep检查通过,起码可以认为以上4部分都在正常工作。

而永久性或暂时性的故障就说明上面的这些硬件或者电路损坏了或者暂时失效了。

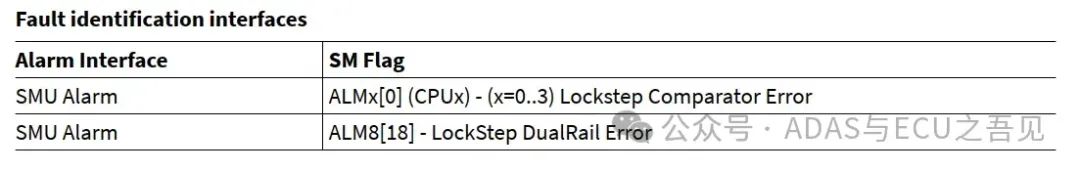

故障通常需要连接到SMU的Alarm的寄存器上,当LockStep故障发生时,通过SMU触发系统reset。

说到这里,大家可能都理解了,其实它的本质上就是用一个独立的CPU去监控另外一个独立的CPU。

什么情况下需要激活LockStep?

英飞凌官方推荐在功能安全等级为ASIL C 和 ASIL D的情况下,要激活启用LockStep功能;对于QM,ASILA和ASILB没有强制要求。在多核系统中,要求功能安全等级在ASIL C以上的核,必须开启LockStep功能。

为什么需要做LockStep?

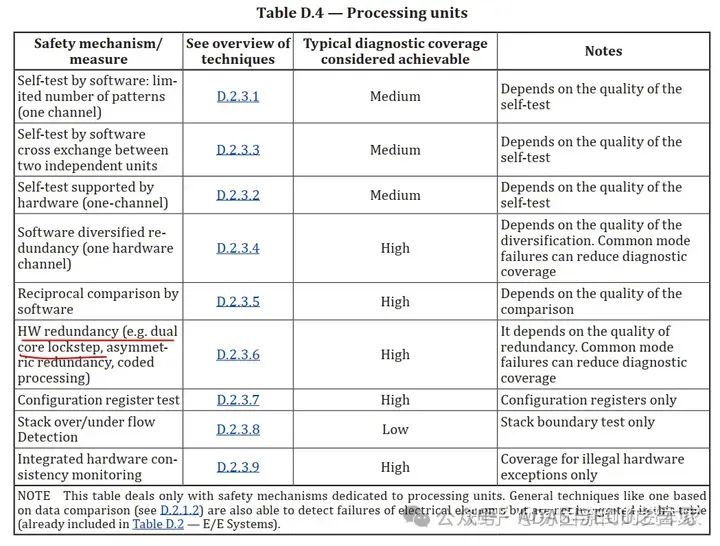

在ISO2626标准中的第5部分硬件安全的附录D中表格4处理器模块的安全机制中提到了双核锁步是具有较高诊断覆盖率的安全机制。

硬件安全机制

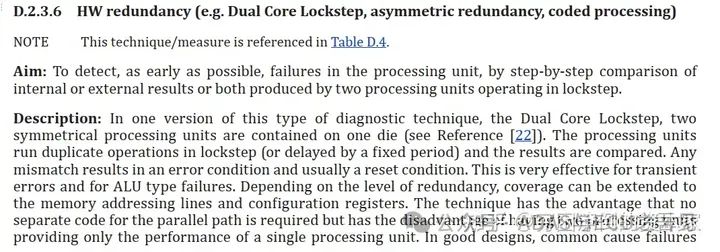

并且在D2.3.6中进行了更详细的描述,标准中的目的和描述总结的都比较到位。

双核锁步描述(续下图)

双核锁步描述(续上图)

解释一下标准中的含义:

目的:通过逐步比较内部的或外部的结果,或比较锁步运行的两个处理单元的结果,尽早地探测出处理单元中的失效。

描述:一个芯片中包含双核锁步的两个对称处理单元。处理单元以锁步(或以固定的延迟运行)方式运行两次并将结果进行比较。任何不匹配会导致错误状态,并通常导致复位。这对于瞬态错误和ALU类型失效是非常有效的。基于冗余的程度,覆盖范围可扩展到存储器地址线和配置寄存器。

此技术的优点在于对于并行路径不要求单独的代码,缺点是两个处理单元只提供一个处理单元的性能。在好的设计中,共因失效会被获知并被处理(例如,共同的时钟失效)。此方法本身对系统性错误不能提供诊断覆盖。

标准中参考文献

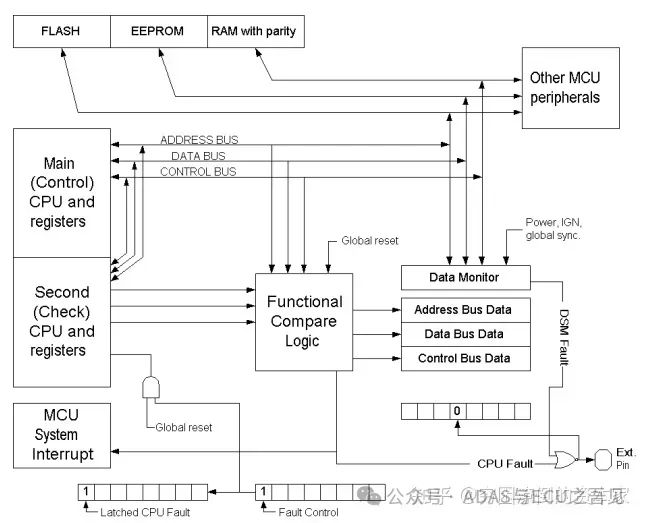

关于ISO26262标准中提到的参考文献22,Fruehling T., & Delphi Secured Microcontroller Architecture 文章,进行了查阅,文章中提到了更多的关于Check core技术方案和细节,这可能是lockstep在单片机领域应用最原始的模型。

Check CPU

一个主控CPU——控制MCU系统外设。

一个辅助CPU – 与主CPU 同步操作,接收与主CPU 相同的所有输入,但其只输出给到功能比较模块。

一个功能比较模块——比较主CPU 和辅助CPU 的地址、数据和控制输出。如果发生故障,ECU 系统输出将被禁用。在 Delphi 系统中,CPU 保持活动状态以帮助诊断。

一个数据流监视器(DSM)。– 内存映射模块,专为内存的自主并发后台测试而设计。此外,该模块还能够在 CPU 位于总线上时对数据流进行签名。

• RAM 上的奇偶校验

• 选定外设模块的备份

• 辅助时钟振荡器和错误检测电路。

怎样使用LockStep?

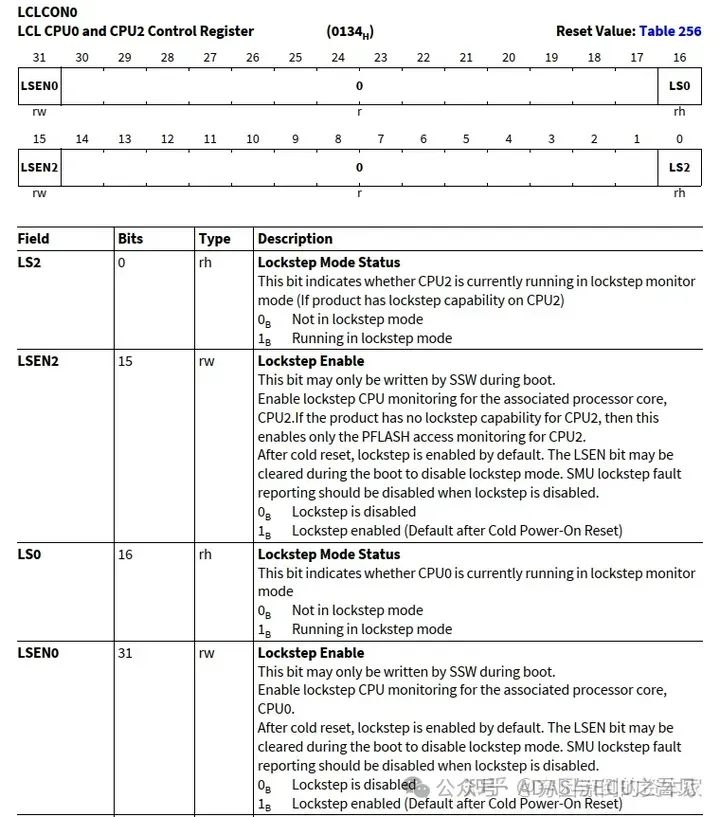

LockStep本质上属于硬件的安全机制,所以使用起来比较容易,只需要配置使能就可以了,我们以英飞凌Aurix Tc39x为例,该芯片共有6个核,其中core0默认是LockStep模式,core1,core2,core3可以配置为激活或禁用LockStep功能,core4和core5不支持LockStep。

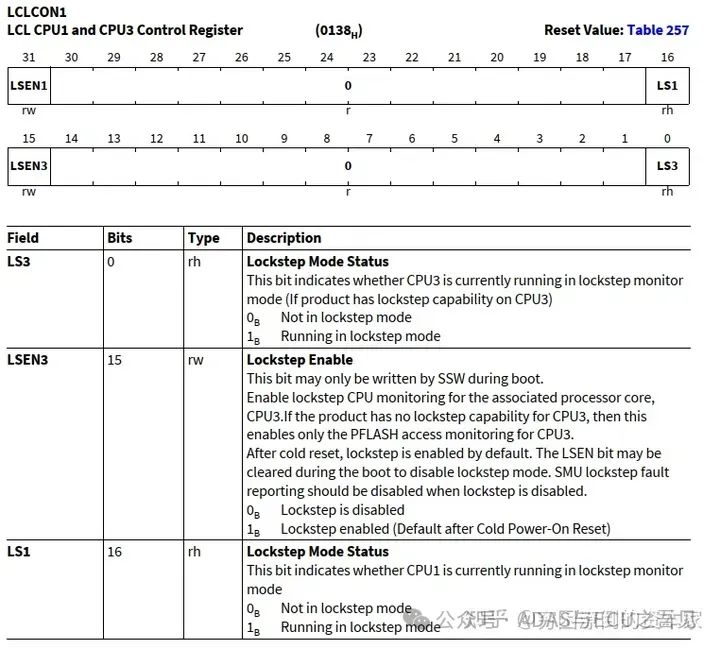

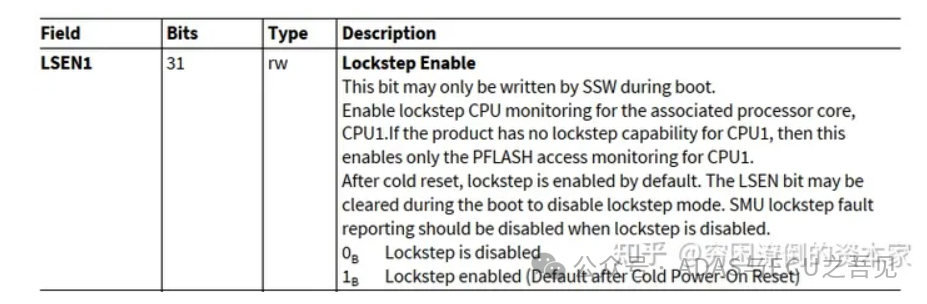

主要配置的寄存器为LCLCON0和LCLCON1。

LSEN0,LSEN1, LSEN2, LSEN3 对应4个CPU的Lockstep enable的使能寄存器

当该bit设置为1,激活LockStep功能, 设置为0,禁用LockStep。

LS0, LS1, LS2, LS3为只读寄存器,用于观测CPU的实际模式,1:Lockstep mode,0:Not in Lockstep mode

LCLCON0寄存器

LCLCON1寄存器(续下表)

LCLCON1寄存器(续上表)

注意,上面这些寄存器只能由启动固件写入,并通过BMI进行配置。

img

Lockstep Configuration

LockStep故障默认连接到SMU Alarm的ALMx[0]核ALM8[18], 其中x代表CPUx SMU ALARM故障连接

img

LockStep如何进行测试?

1.故障注入原理

通过上面对LockStep的理解,我们可以知道只有芯片内部的永久性失效和暂时性失效才会导致lockstep错误,所以如何测试LockStep就成为一个难题,不过好在芯片公司一般都会设计self-test的机制,给故障注入留出接口,以英飞凌AurixTc39x为例,故障注入工作原理如下:

故障注入工作原理图

1.使用故障生成块注入故障。使用二进制数解码来计算要测试哪个节点。解码将从使用格雷码数字表示的自由运行的二进制计数器(输入计数器)生成。

\2. 自测试电路将每 8192 个时钟周期测试每个节点一次。交替测试周期将注入 比较器节点的 a 侧或 b 侧发生故障。因此,完整的自测试周期将每 16384 个时钟周期重复一次。将故障注入比较器节点的任一侧都会导致该节点发生故障,除非在同一时钟周期内发生真正的故障,在这种情况下,两个故障将相互抵消。

\3. 故障节点由故障编码块处理,以生成故障节点的二进制表示形式,进行编码。它包含两个数字,即从最低的最小节点索引开始向上计数的第一个失败节点的节点索引,以及从最大节点索引开始向下计数的第一个发现失败的节点的节点索引。

4.如果锁步块正常工作,则编码中的两个值要么为 0(如果未检测到故障),要么为自测试逻辑引起故障的节点数。编码中的值根据第二个独立的二进制计数器(监视计数器)进行检查。监视器计数器还会与输入计数器的值进行比较。如果编码中的值或输入计数器的值与监控计数器的值不匹配,则会向 SMU 标记故障。

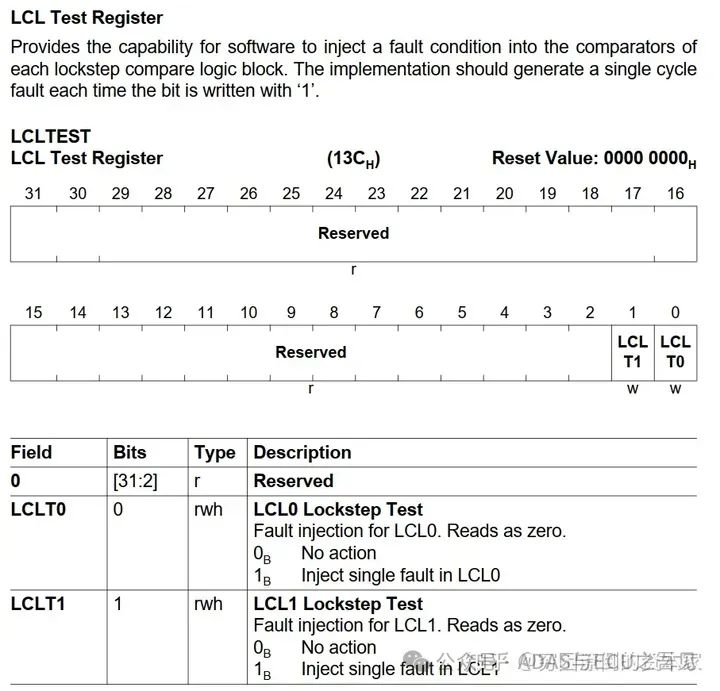

2.寄存器配置

LCLTEST寄存器,LCLT0和LCLT1两个bit对应LCL0和LCL1的故障注入,0为没有动作,1为故障注入。

故障注入寄存器

结语

今天关于LockStep CPU的分享就到这里了,其实在功能安全审核时或介绍自己产品的安全优势时,我们经常会讲产品的MCU是支持LockStep CPU的,但实际上对于LockStep工作原理和细节并不清楚,希望今天的分享能够让各位同学理解LockStep的工作原理和细节,真正体会到安全机制的重要意义。

6309

6309

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?