1.二选一数据选择器,要求如下:

【注】 always语句块里赋值的变量需要是reg型

module fn_sw(a,b,sel,y);

input a,b,sel;

output y;

assign y = (sel==0)?(a&b):(a^b);

endmodule`timescale 1ns/10ps

module fn_sw_tb;

reg a,b,sel;

wire y;

fn_sw fn_sw(

.a(a),

.b(b),

.sel(sel),

.y(y)

);

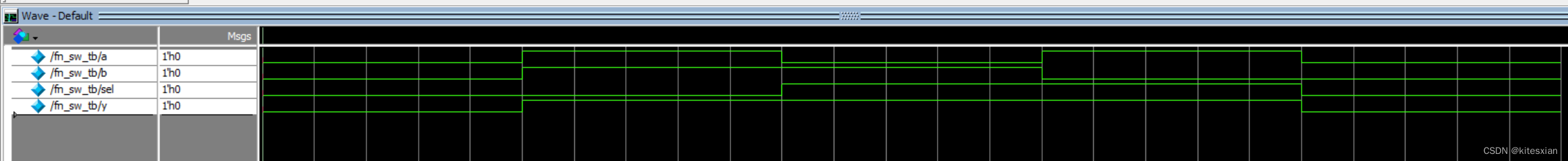

initial begin

a<=0;b<=0;sel<=0;

#10

a<=1;b<=1;sel<=0;

#10

a<=0;b<=1;sel<=1;

#10

a<=1;b<=0;sel<=1;

#10

a<=0;b<=0;sel<=0;

#10

$stop;

end

endmodule

【注】 我们在上述代码中使用了assign,其实也可以尝试使用一下always

即将下面代码

assign y = (sel==0)?(a&b):(a^b);

更换为

reg y;//因为下面要改变y了,所以声明reg y;

always @(a or b or sel)//敏感列表(即括号中任意值改变,则执行下述代码)

begin

if(sel==0)

begin

y<=(a&b);

end

else if(sel==1)

begin

y<=(a^b);

end//如果只有一个语句,就不用begin end块,为了养成良好习惯,还是写上;

end

显然,这个题使用assign相当于always更简单,但是有些题用assign是实现不了的,比如下一题;

2. 四选一选择器

module fn_sw(a,b,sel,y);

input a,b;

input[1:0] sel;

output y;

reg y;

always @(a or b or sel)begin

case(sel)

2'b00: begin y<=a&b;end

2'b01: begin y<=a|b;end

2'b10: begin y<=a^b;end

2'b11: begin y<=~(a^b);end

endcase

end

endmodule`timescale 1ns/10ps

module fn_sw_tb;

reg a,b;

reg[1:0] sel;

wire y;

fn_sw fn_sw(

.a(a),

.b(b),

.sel(sel),

.y(y)

);

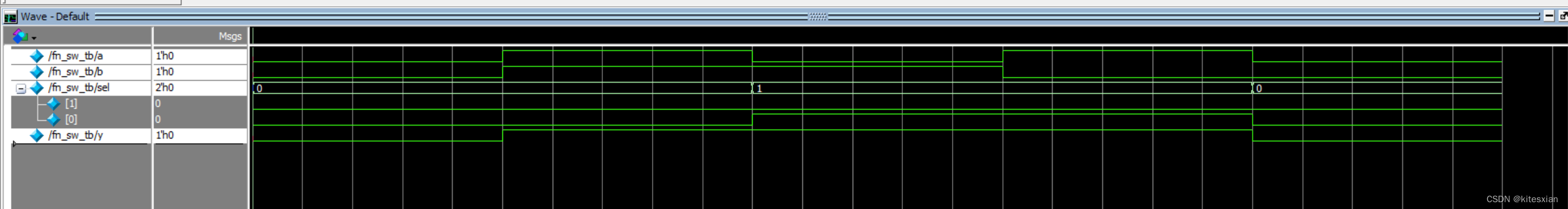

initial begin

a <= 0; b <= 0; sel <= 2'b00; // 初始化为00

#10

a <= 1; b <= 1; sel <= 2'b00; // 然后变为00

#10

a <= 0; b <= 1; sel <= 2'b01; // 然后变为01

#10

a <= 1; b <= 0; sel <= 2'b01; // 再次变为01

#10

a <= 0; b <= 0; sel <= 2'b00; // 最后回到00

#10

$stop; // 停止仿真

end

endmodule这其实是2位的sel来选择四种状态,所以是一个四选一选择器;

参考链接:精准空降

6922

6922

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?