众所周知,后仿真消耗资源,消耗时间,短则1~2周,长则1个月都是有可能的。那么如果仿真时间超过1~2周的,势必需要进行一些加速手段。基于本人2个项目的后仿真经验来看,后仿80%的时间都消耗在寄存器配置上,后门配置寄存器针对一些配置寄存器慢,或配置寄存器多的case是一个好手段,但实际过程中遇到不少问题,现总结如下:

一、确认hierarchy是否存在

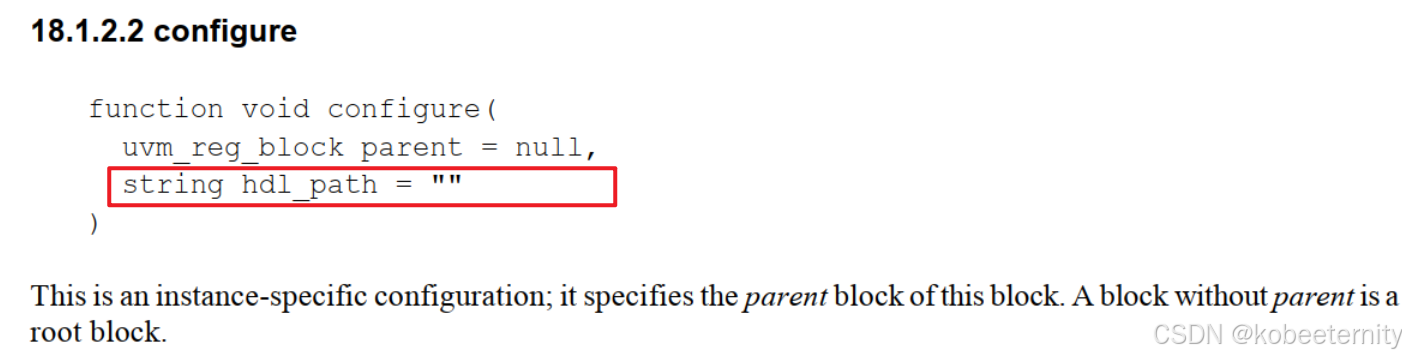

1. 先确保前仿真的后门配置无误,然后需要针对后仿真netlist中各自模块的regbank的hierarchy是否有变化,即我们在ral model 实例化时的configure中的hdl_path是否有变化。如果hdl_path有变化,需要修改hdl_path,确保在netlist的hierarchy中能够找到对应的regbank。

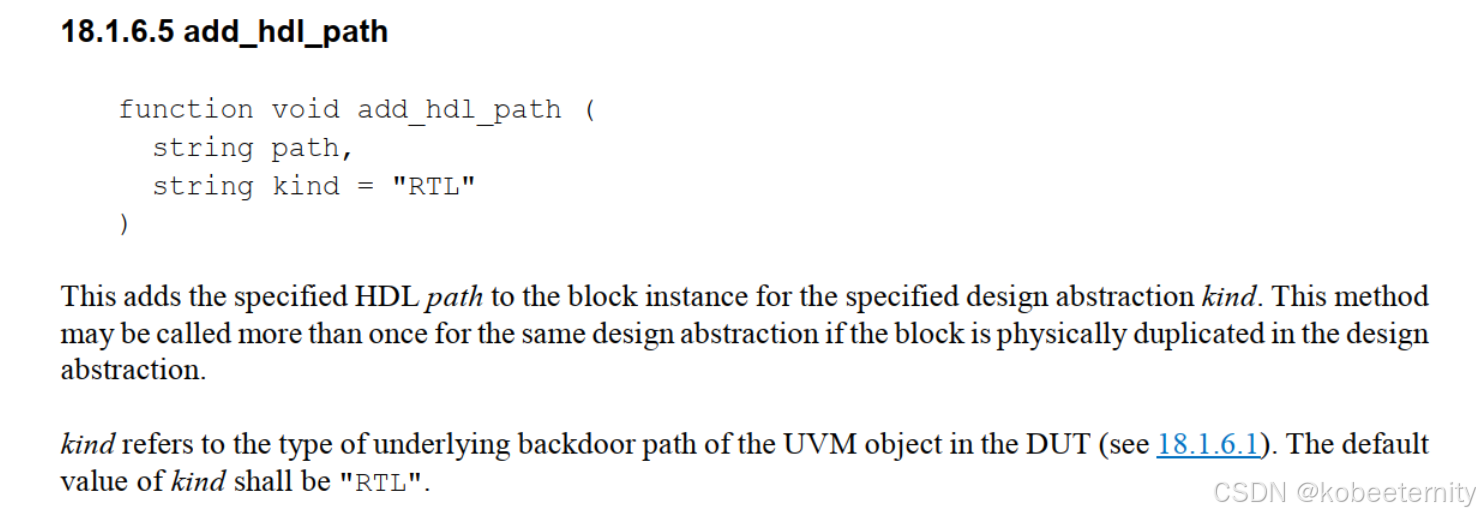

2. 当确定各自regbank的hierarchy无误之后,需要查看regbank中最终配置生效的register name是否有变化,如果有变化,那么需要修改对应的uvm_reg中的add_hdl_path中的path。

3. 以上2步是为了确保当我们从RTL切换到netlist后,依旧能够找到对应的reg_name,因为后门的本质是deposit,所以确保hierarchy没有问题才能确保可以使用后门访问,注意如果一些冗余寄存器,即没有load的寄存器可能会被直接优化掉。

二、增加-debug_acess+wn option

当后仿真进行后门访问时,debug option这边需要注意进行增加-debug_access+wn,不然会报UVM_ERROR:set:unable to write hdl path(tb.x.x.x.x.x.x)。但其实hierarchy(tb.x.x.x.x.x.x)是真实且存在的。

但是注意,不建议在后仿真直接使用-debug_access+all,会拖慢仿真速度,还是基于自我需要去分开增加debug选项。

三、inverter对backdoor的影响

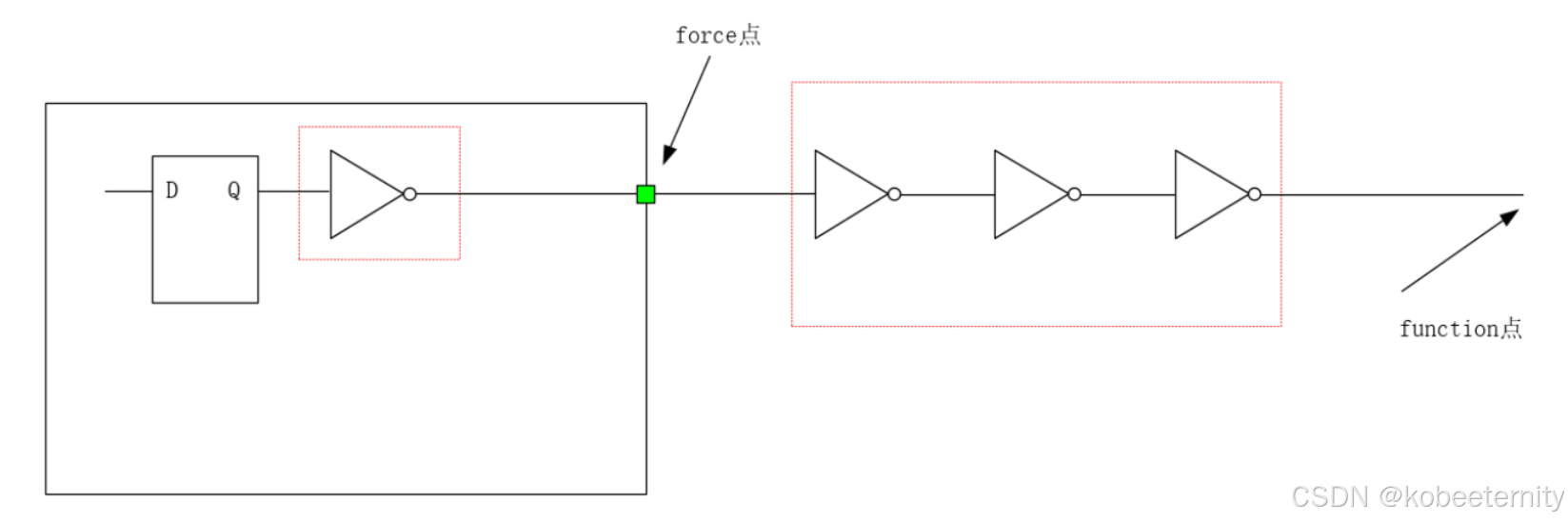

以上步骤完成,基本就能在波形上看到对应的寄存器被后门配置成功了,但是也只是寄存器被配置成功了,并不意味着配置是正确的。为什么这么说,是因为在后端修Timing的时候,会插一些inverter,那就有可能在regbank之前的path上有插,这有可能会对最终寄存器的function value有影响。

(1)偶数个inverter:如果插的inverter是成对的(偶数个),那没有任何问题。比如说我们期望要配置寄存器A为1,那其实依旧backdoor配置为1即可,因为在regbank这一层级,此刻寄存器A的value就是1。

(2)奇数个inverter:但是如果他在regbank之前的path有插入奇数个inverter,那就有问题了,也就意味着其实我们应该backdoor把这个寄存器A配置为0。如下图所示,绿色点为regbank中的reg_name,也是我们后门配置的force点,我们如果backdoor为1,其实最终到对应的function点,其实变成了0(1->0->1->0),即配置没有生效。这就是因为在regbank前面的path有插单个inverter,但其实如果是前门配置,我们配置1是没有任何问题的,因为(1->0->1->0->1),最终function点依旧是1。

所以这个地方需要注意,在正式跑后仿之前,找一条后仿真netlist的case进行try_run,先把需要配置的寄存器的默认值通过backdoor都读出来,如果与前仿真RTL的默认值相同,意味着并没有插inverter或者说没有插奇数个inveter,前仿真配置什么值,后门依旧配置什么值即可。如果与前仿真的默认值相反,即后门backdoor配置时取反即可。

四、无法使用ral model时,找到Q端 force

如果regbank和reg_name的hierarchy存在,又或者有变化但是是有规律的变化,还是建议通过上述方式进行backdoor访问,即通过ral model进行backdoor访问寄存器。

那么如果regbank和reg_name的hierarchy 变化很大且无规律,还想要进行backdoor访问,这个时候确实没办法使用ral model的backdoor访问了,因为ral model依靠hdl_path。

那此刻就必须请后端同事能够找到每个寄存器的function Q端,然后自行根据对应的寄存器value进行force,当然找到Q端进行force就不会遇到上述inverter的问题了,但是这样做略显复杂,且都是单个bit的Q端,最好能用脚本处理。

五、总结

虽然后门访问能够极大程度加速后仿进度,但是建议不要100%寄存器全用backdoor访问,可以遗留一小部分寄存器依旧使用前门访问,这样也可以在后仿中看物理总线访问寄存器是否无误,是否发生Timing violation,如果100%寄存器全用backdoor,可能会导致我们miss一些bug。

530

530

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?