开发了TDR Gating(时域门) 算法模块,可提供dll,算法和PLTS进行过比对,数据一致

一、时域门控的应用:

印刷电路板(PCB)、电缆导体和介电材料对高速数据信号的损耗影响很大。使用矢量网络分析仪(VNA)直接测量这种损耗是确定PCB走线和/或电缆是否会对所需的数据速率和路径长度造成不可接受的损失的常用方法。然而,与大多数PCB走线相关的长度,当然也与大多数电缆相关,当电缆或走线没有完美地端接在电缆或走线的特性阻抗中时,会导致s参数数据中反射和共振效应的可能性。这些共振与长度有关,因此s参数的结果不能准确地指示走线/电缆的真实效果,而是指示与特定长度的走线/电缆以及所使用的特定连接器相关的损耗。由于这些测量伪影,测量结果通常不适用于PCB走线(没有连接器,但直接连接到IC)的更一般分析,或者可能使用不同连接器的电缆,或者当走线/电缆的长度可能变化时。通常需要测量单位长度(每英寸,每米等)的走线/电缆损耗,以便可以从原始测量数据创建任何所需长度的s参数。

消除不需要的连接器效果的一个选择是使用TRL(通过,反射,线)VNA校准。这种VNA校准方法通过在PCB上执行校准,有效地消除了这些末端效应。然而,这种技术需要在PCB上有许多不同长度的走线,以便在宽频率范围内进行校准。此外,连接器本身必须是高质量的连接器,因此它们的高频特性都是相似的,以及PCB上的介电材料必须在PCB上保持一致。这些要求并不总是可能的,特别是当使用低成本电介质的pcb时,TRL不适用于电缆。

本文给出了时间门控对PCB走线和电缆影响的一些例子。一致性非常好,表明该程序有效地消除了不必要的反射/共振,并允许准确确定走线和电缆的单位长度参数。

二、时域门控原理:

时域门控是一种在数学上消除时域中不需要的响应的函数。该函数进行时域变换,选择时域内的区域,删除区域内(或外)的响应,并变换回频域。如果有用信号和杂散信号在时域上是可分离的,则该功能允许用户在频率响应中去除夹具设备的杂散影响。该函数仅适用于反射系数(S11, S22等)的测量。

门控提供了从数学上消除特定电路元件影响的能力。定义栅极的起始点和停止点。门控部分用具有相同电延迟的理想传输线代替

门控应用于单个参数的时间图。当对一个参数的时域图进行门控时,您可以观察到门控对同一参数的频域的影响。

加q:2498202411

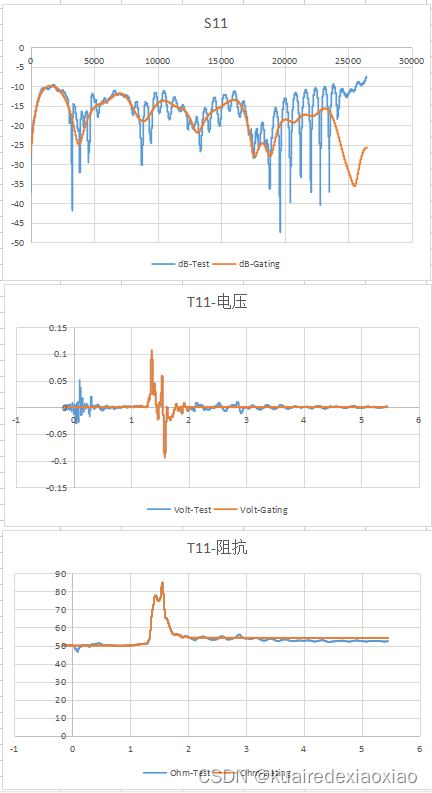

三、时域门控算法数据结果显示

Bandpass : 保持响应在门跨度内,移除栅极范围外的响应,栅极的起始点和停止点:1ns到2ns

8824

8824

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?