Riscv五级流水线64位cpu,systemverilog编写,指令集rv64i,支持csr寄存器,可跑通dhrystone测试。

支持2bit饱和分支预测

本包括:

1.rv64单周期Cpu

2.rv64多周期Cpu

3.rv64五级流水线Cpu,支持数据前递

4.上述cpu的测试平台(可跑通dhrystone测试)

5.一份五级流水线cpu的详细说明文档

从单周期cpu到多周期cpu到五级流水线,支持csr ,适合riscv的深入学习。

ID:59300664424451223

云赐记

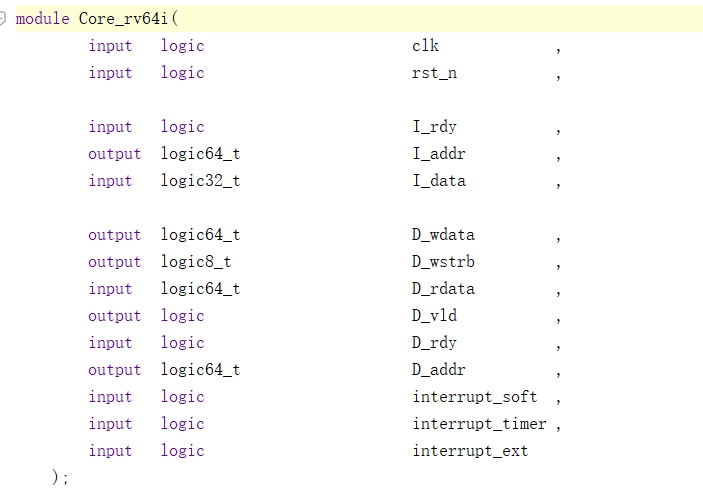

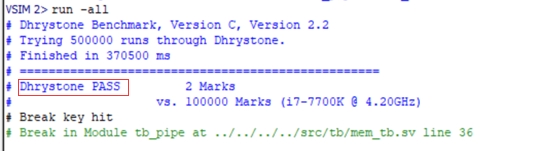

RISC-V五级流水线64位CPU,使用SystemVerilog编写,指令集为RV64I,支持CSR寄存器,并能够成功运行Dhrystone测试。除此之外,还包括了以下内容:

- RV64单周期CPU

- RV64多周期CPU

- RV64五级流水线CPU,支持数据前递

- 上述CPU的测试平台,能够顺利通过Dhrystone测试

- 一份详细的五级流水线CPU说明文档

本文将围绕这些内容展开,帮助读者深入学习RISC-V架构。我们将从单周期CPU开始介绍,逐步深入到多周期CPU和五级流水线CPU,让您对RISC-V的原理有更加全面的了解。

首先,我们回顾一下单周期CPU的设计。单周期CPU是最简单的CPU设计之一,每个指令在一个时钟周期内完成。其设计思想简单明了,适合初学者学习RISC-V架构。然而,由于每个指令都需要在一个时钟周期内完成,导致了指令执行效率低下。为了解决这个问题,我们引入了多周期CPU。

多周期CPU是在单周期CPU的基础上进行改进的,它将每个指令的执行划分为多个阶段,每个阶段在一个时钟周期内完成。这样一来,每个阶段可以专注于完成特定的任务,大大提高了指令的执行效率。多周期CPU的设计相对复杂一些,需要考虑指令之间的依赖关系和冲突,但能够更好地发挥CPU的性能。

然而,多周期CPU还存在一些问题,例如指令之间的停顿和资源冲突。为了进一步提升CPU的性能,我们引入了五级流水线CPU。五级流水线将指令的执行过程划分为五个阶段:取指阶段、译码阶段、执行阶段、访存阶段和写回阶段。通过将指令流水线化,我们可以同时执行多条指令,大大提高了CPU的并行性和执行效率。

在五级流水线CPU中,我们还支持了数据前递技术。数据前递能够解决数据相关导致的停顿问题,提高指令的执行效率。当一个指令需要使用前一条指令的计算结果时,通过数据前递将计算结果直接传递给当前指令,避免了停顿的产生。

为了验证我们设计的CPU的正确性和性能,我们还开发了一套测试平台,其中包括了Dhrystone测试。Dhrystone是一种常用的CPU性能测试程序,通过执行一系列基准测试,可以评估CPU的性能和效能。

最后,我们还提供了一份详细的说明文档,对五级流水线CPU的设计和实现进行了详细解释。文档内容包括CPU的整体架构、各个阶段的功能和实现细节,以及一些设计上的优化思路。通过阅读这份文档,读者可以更深入地了解五级流水线CPU的原理和实现方法。

综上所述,本文围绕RISC-V五级流水线64位CPU展开了详细的介绍和分析。我们从单周期CPU到多周期CPU再到五级流水线CPU,深入探讨了每个阶段的设计和实现。除此之外,我们还提供了测试平台和详细说明文档,帮助读者更好地理解和学习RISC-V架构。通过阅读本文,读者可以对RISC-V的原理有更加全面的了解,并且能够通过自己的实践来进一步加深对RISC-V的理解。

相关的代码,程序地址如下:http://nodep.cn/664424451223.html

779

779

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?