目录

1 初步怀疑电源供电能力不够

1.1 电流测量

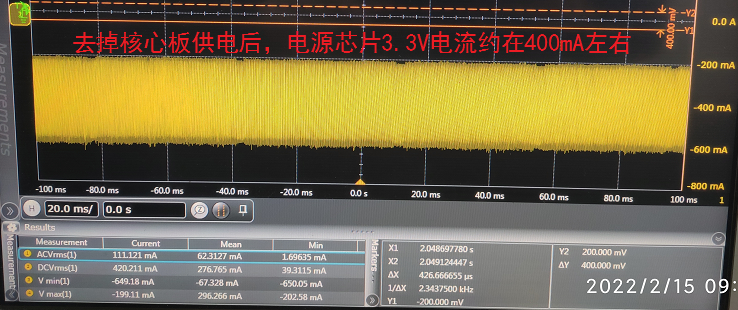

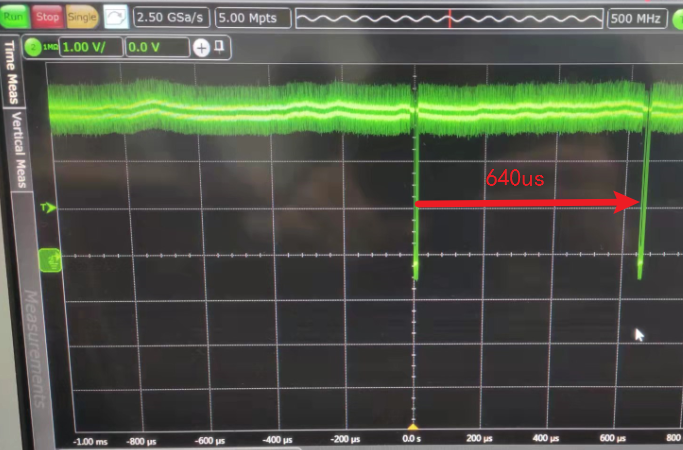

产品调试人员反馈冷启动75分钟断开连接一次,后续越来越频繁。在3.3V的源头串入导线,用示波器测量电流,同时检测3.3V电压。5V转3.3V的电源芯片62084最大输出2A电流,图中可以看到电流会冲到3A,且电压会下降到3V以下,确有些过载。

1.2 改供电方式

为实现装置平台的无缝切换,ZX701核心板仅5V电源供电(原自研核心板仅3.3V供电),在转接板上用3.3V升压得到,核心板功耗大约在3W。同时转接板还有两个ETH PHY SR8201F,USB转UARTx4 CH9344L,看门狗,RS232等直接使用3.3V的芯片。将转接板上的3.3V升压5V的61088去掉,核心板5V从底板的5V直接飞线供电,减少62084负载。再次测量3.3V电流约在400mA左右,专供核心板的5V电流约在300mA左右。

长时间测试网口仍然有断连,但是基本固定在75min左右,且电脑的连接图标不再断开![]() 。

。

1.3 原设计注意问题整改

ZX核心板上的MCU_3V3是从核心板的5V转出给SWD调试口,不能连接底板的VCC_3.3V,否则可能会形成倒灌。

2 怀疑CPU对PHY的reg有错误的写操作

寄存器0x00的reg中[9]=1重启自动协商时会断连。

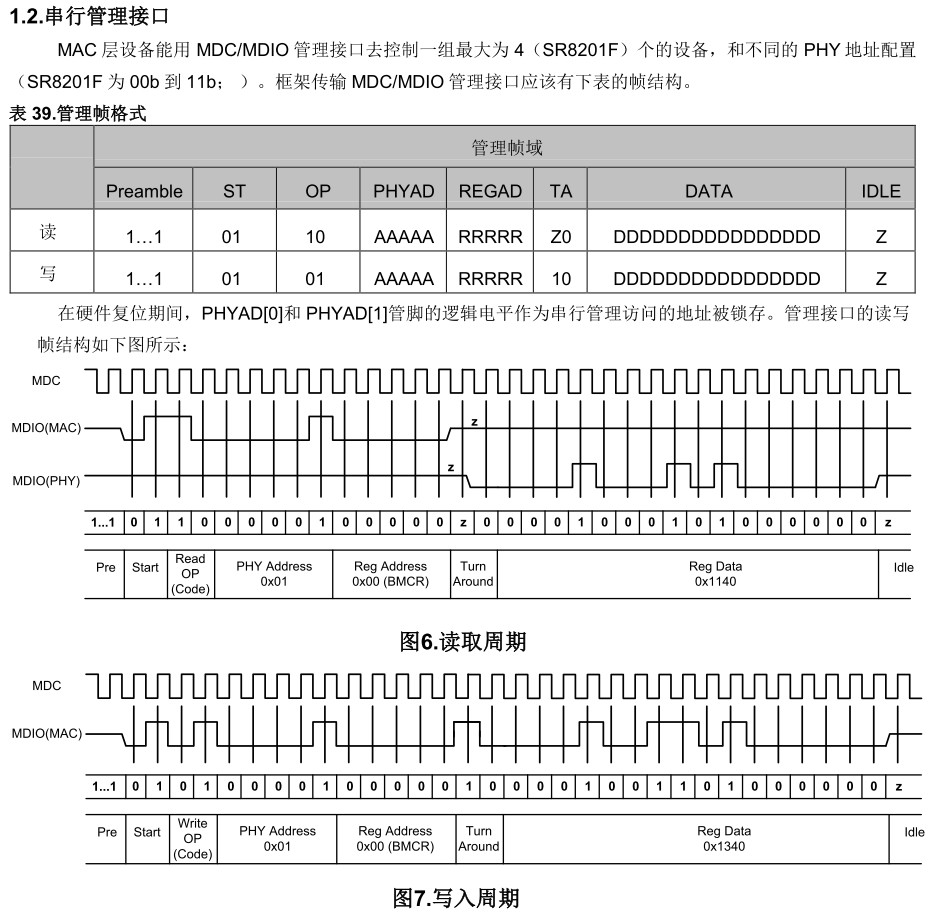

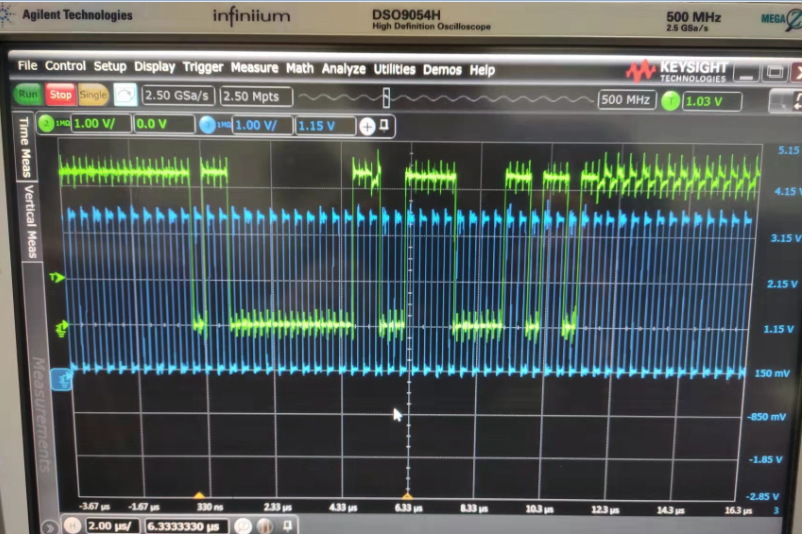

SR8201F的MDIO时序如下。

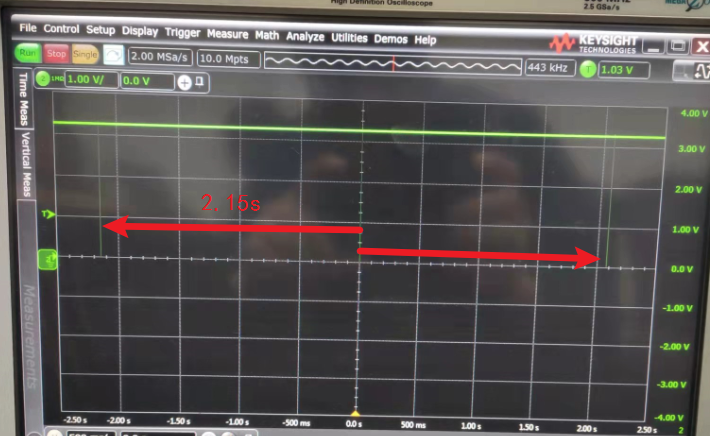

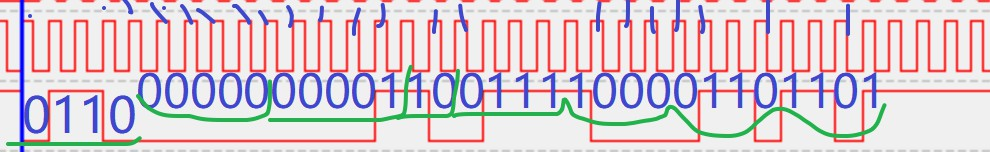

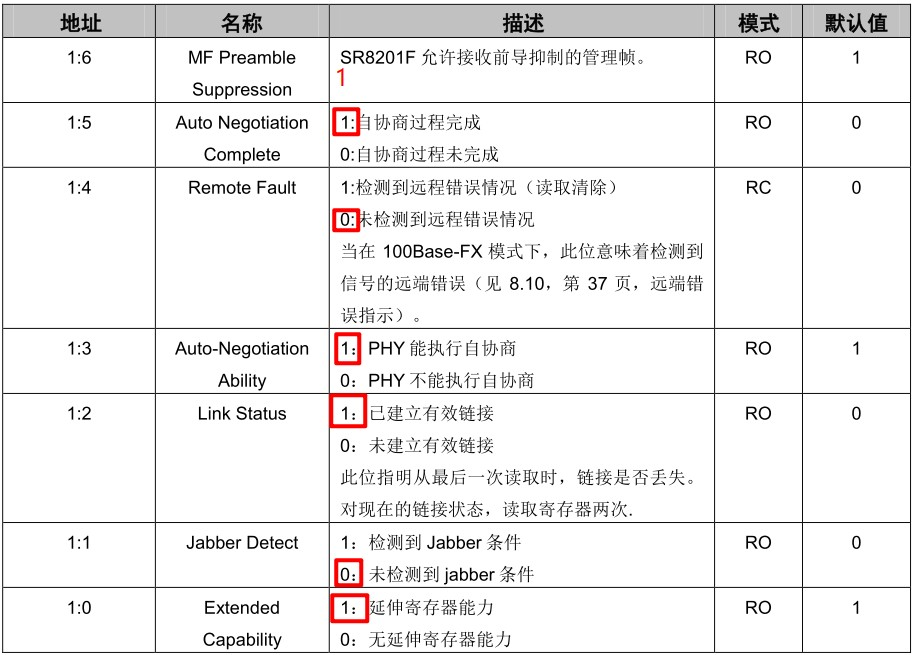

抓取MDIO总线上的数据。每隔2.15s会被读取一组,每组内为间隔约640us的两次读寄存器0x01的操作,读出值为0x786d。

把MDIO的两根线接入一块有FPGA的板子GPIO上,在FPGA中编写抓取代码 ,在TD软件的Chipscope中触发抓取读写,自制逻辑分析仪。

always @( posedge mdc )

begin

mdio_reg <= mdio;

s_data[0] <= mdio_reg;

s_data[31:1] <= s_data[30:0];

end

always @( posedge mdc )

begin

if (s_data == {23'h7fffff ,2'b01,2'b10,5'h00} ) rd_reg <= 1;//0xFFFF_FEC0

else rd_reg <= 0;

if (s_data == {23'h7fffff ,2'b01,2'b01,5'h00} ) wr_reg <=1;//0xFFFF_FEA0

else wr_reg <=0;

wr <= wr_reg;

rd <= rd_reg;

end 抓取的读操作如下,数据与示波器相同。触发抓取一晚上写操作,没有抓到,没有写操作。

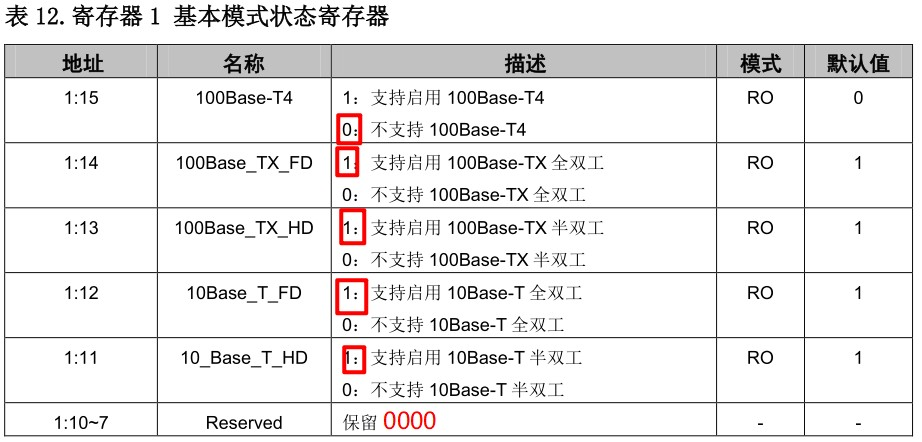

0x01寄存器内容如下:

3 怀疑CPU对PHY 有错误的复位行为

抓取复位信号,示波器开启触发模式,在PHY出错时并未抓到复位信号。

4 更换测试工具

更换网口测试工具,建立TCP连接后,定时通讯,两天未发生断链。基本定位在应用软件bug,需要软件进一步检查。软件已定位时间reg存在溢出。

SR8201F的兼容型号YT8512T。

6159

6159

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?