这是我的第一篇文章分享,以后我有时间就会做一些项目来分享,我希望这是一个菜鸟走上高手的征程。

AHB-Lite总线协议

AHB特性:Burst传输、单边操作、非三态、宽数据位。其是为高性能、高频率系统而设计,对于低带宽外围器件可以连接到APB总线。(通过桥接)。

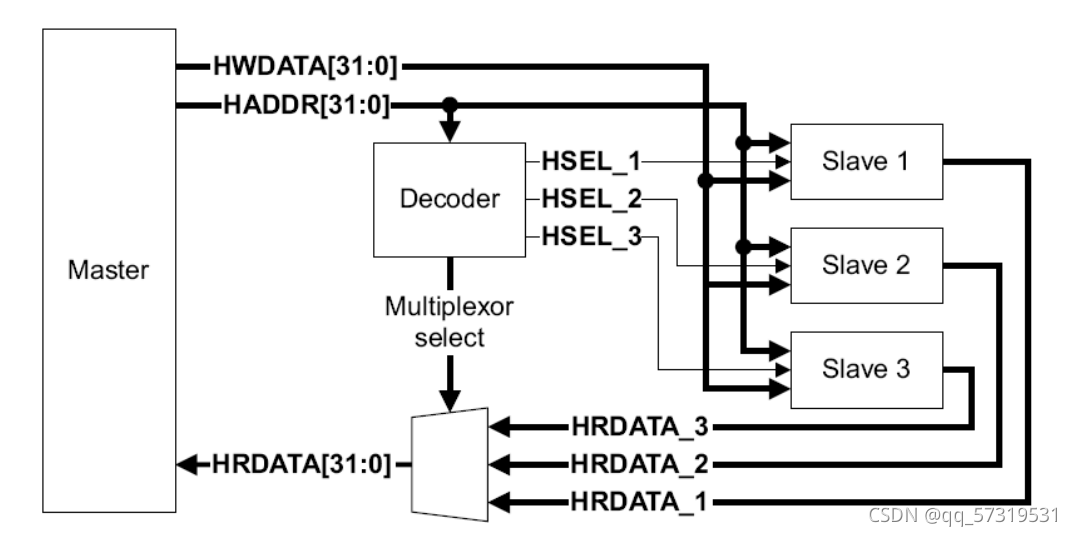

对于多个Mster和Slave的AHB总线结构由四个部分组成:Mster设备、Slave设备、地址译码器、仲裁器。但是,目前AHB总线多用于一个MASTER对多个Slave,此时仲裁器替换为多路选择器。下将详解一个MASTER和多个SLAVE的传输过程。

信号描述:

全局信号:

HCLK:总线时钟

HRESETN:总线复位信号,低电平有效。

Mster信号:

HADDR:32位系统地址总线。

HBURST[2:0]: 传输类型指示,支持固定长度4、8、16拍。总数据量等于拍数×每一拍数据大小。

HMASTLOCK:为高时表示当前传输是锁定序列的一部分。与地址和控制信号具有相同时序。

HPROT:保护控制信号提供额外的关于总线访问的信号,主要用在一些需要调用某种级别保护的Slave模块。

HSIZE:传输大小。

HTRANS:传输类型,可以有四种方式。

HWDATA:写数据。

HWRITE:表示传输方向,高为写传输,低为读传输。

Slave信号:

HRDATA:读数据信号。

HREADYOUT:为高时,表示传输在总线上结束。该信号可以通过拉低来对传输进行延迟扩展。

HRESP::传输响应。为低表示传输状态正常;为高表示传输状态错误。

译码器信号:

HSEL:每个Slave都拥有对应的HSEL信号,当Slave被选中,就会将对应的HSEL信号拉高表示被选中。

多路转换器信号:

HRADATA:读数据传输。

HREADY:为高时,提示Mster和所有的Slave,先前的传输完成。

HRESP:传输响应,由译码器选择。

系统解释:

图示是一个MASTER和三个SLAVE的系统:

内部逻辑生成了一个地址解码器和多路选择器。

接下来分别从master和slave来讨论对应的信号接口:

MASTER:

<

本文介绍了AHB-Lite总线协议的特性,包括其在高性能系统中的应用,以及与APB总线的关系。详细阐述了一个MASTER对多个SLAVE的传输过程,涉及信号描述、传输模式、传输类型、保护控制和总线互连等内容,为理解嵌入式系统的总线通信提供了清晰的指南。

本文介绍了AHB-Lite总线协议的特性,包括其在高性能系统中的应用,以及与APB总线的关系。详细阐述了一个MASTER对多个SLAVE的传输过程,涉及信号描述、传输模式、传输类型、保护控制和总线互连等内容,为理解嵌入式系统的总线通信提供了清晰的指南。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2874

2874

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?