文章目录

UG949设计方法学

原则

理解时序报告

设计基准

时钟域交汇约束

检查时钟关系

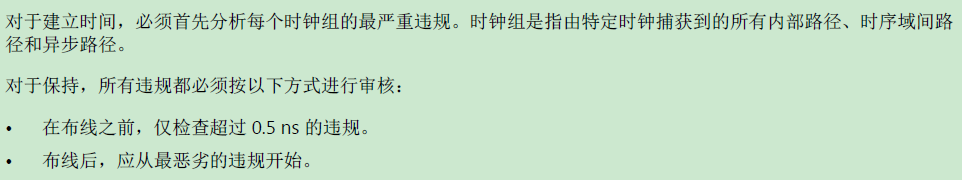

使用 report_clock_interaction Tcl 命令查看时钟之间的关系。该报告给出一个源时钟和目标时钟的表格。每个单元中的颜色都表示时钟之间的交互类型,其中包括它们之间的任何现有约束。

明确严格的时序要求

同时约束主时钟和生成时钟

限制 I/O 约束和时序例外

大部分时序违规都存在于内部路径上。在首次基准 (baseline) 设计迭代过程中无需 I/O 约束,尤其对于发送和捕获寄存器位于 I/O bank 内部的 I/O 时序路径来说更不需要 I/O 约束。在设计及其它约束已稳定并且时序接近收敛之后,就能添加 I/O 时序约束。

评估WNS

分析解决时序违例

确定根源

分析路径特性

report_design_analysis -max_paths 50 -setup -name design_analysis_postRoute

查看逻辑层次分布

report_design_analysis -logic_level_distribution -logic_level_dist_paths 5000 -name design_analysis_prePlace

report_design_analysis -logic_level_distribution -min_level 16 -max_level 20 -logic_level_dist_paths 5000 -name design_analysis_1

拥塞

相关warning和info

WARNING: [Place 46-14] The placer has determined that this design is highly congested and may have difficulty routing

INFO: [Route 35-449] Initial Estimated Congestion

报告设计分析复杂性报告

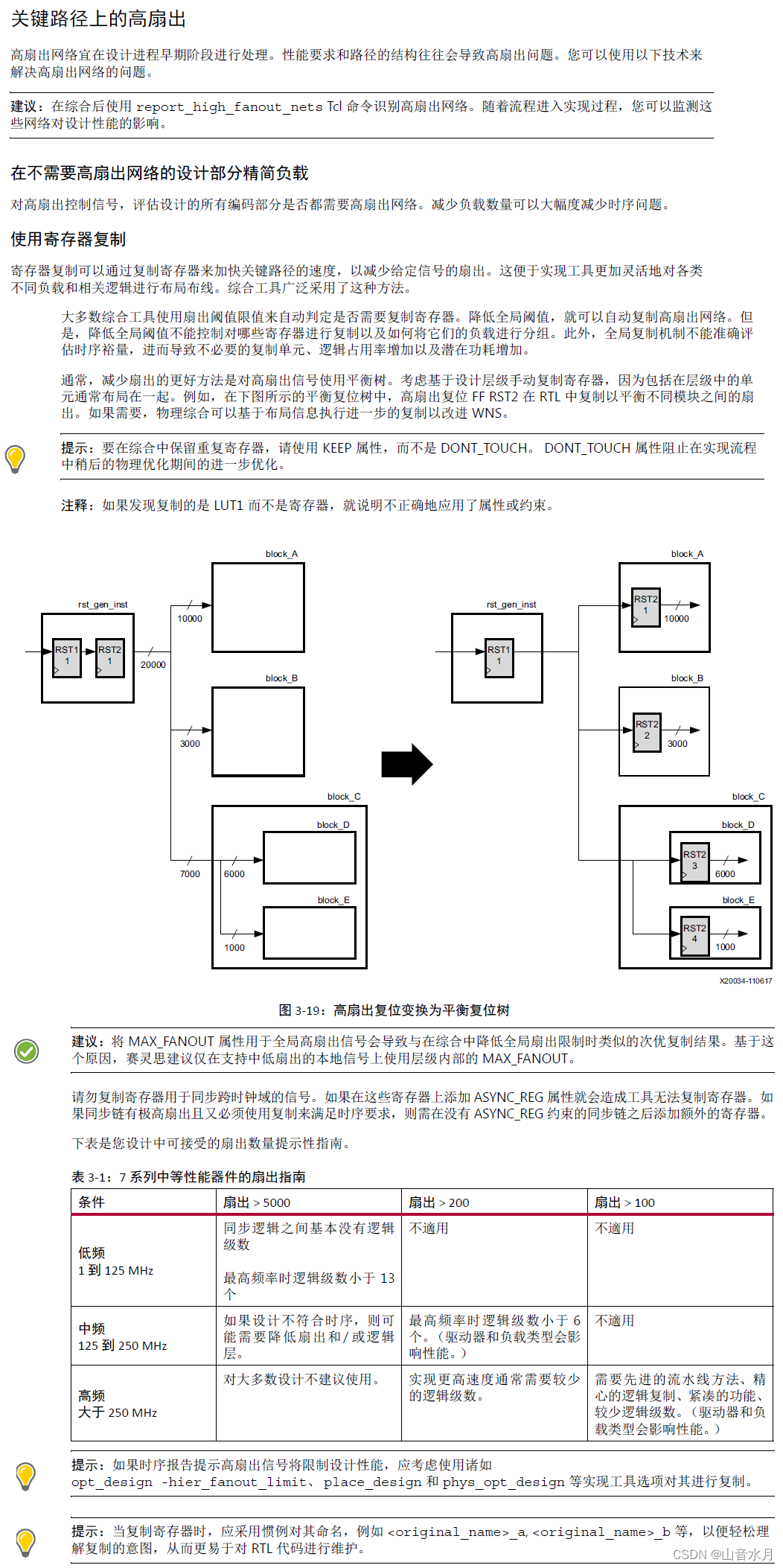

解决关键路径上的高扇出

UG1292快速指南

497

497

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?